1、重点讲解:

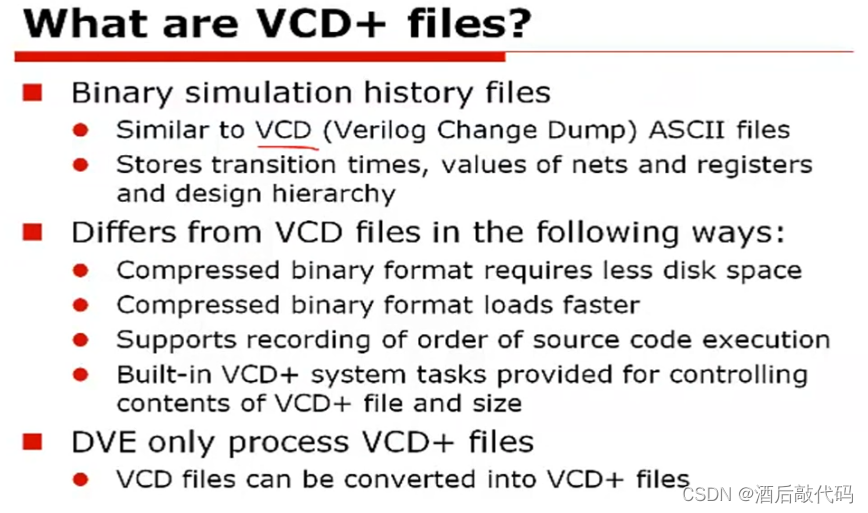

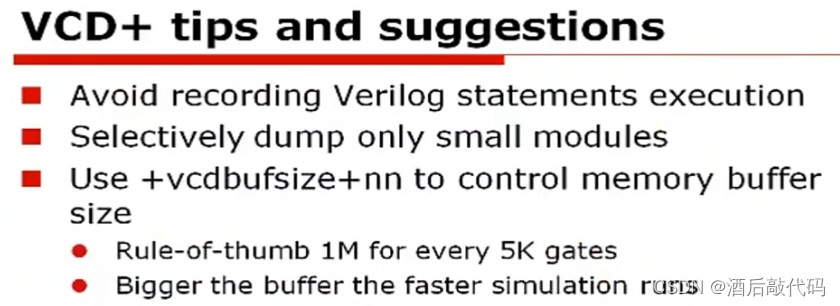

在verilog源代码中嵌入VCD+ 系统函数,重点如testbench文件中。VCD文件是VCS产生的仿真波形文件,未经压缩,占用空间较大。VCD+是压缩后的波形文件。

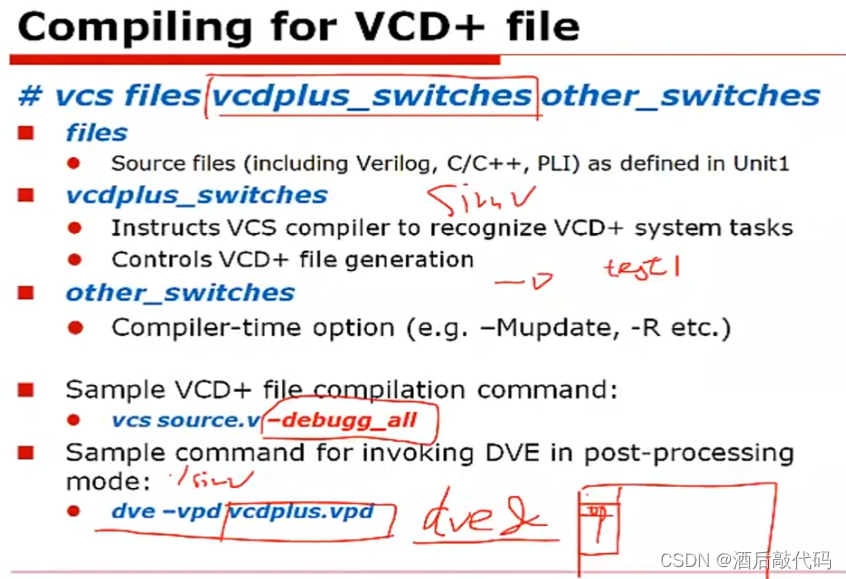

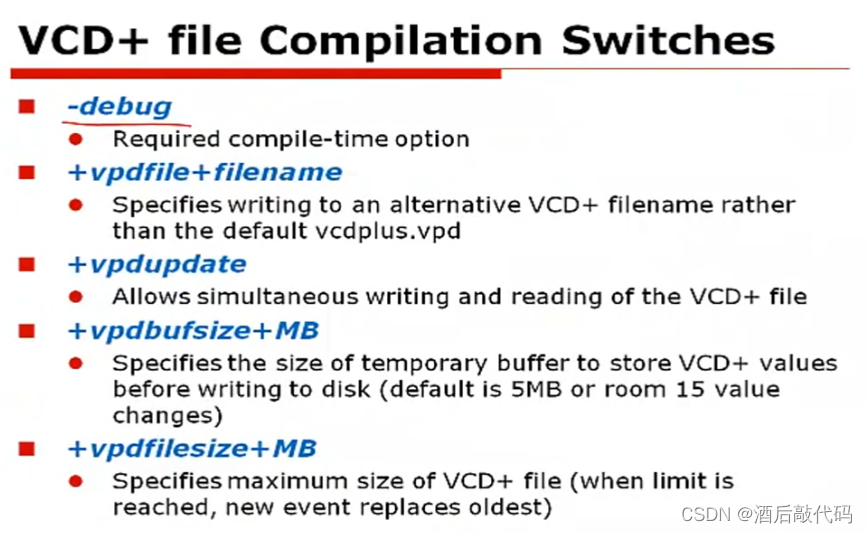

编译、仿真以生成VCD+文件。

在后处理模式中使用激活DVE+log对产生的errors进行修改优化。

将VCD+文件读进debugger memory中。

最后,Debug。

2、DVE后处理模式

1)仿真速度:

2)信号可视性:用户定义

3)信号可追踪性:可通过源码、原理图或者波形追踪信号,以便后期通过log记录的信息消除errors。

4)适用性:友好的图形界面以及可以应用于所有级别复杂度的电路仿真。

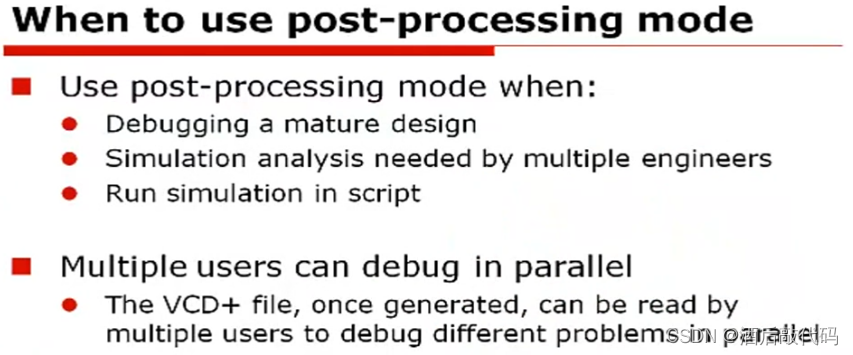

什么情况下使用后处理模式?

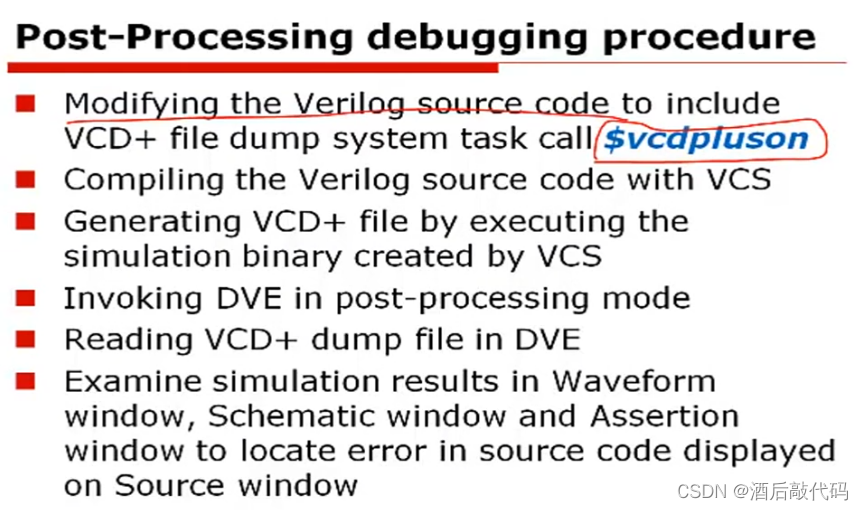

后处理debug的步骤:

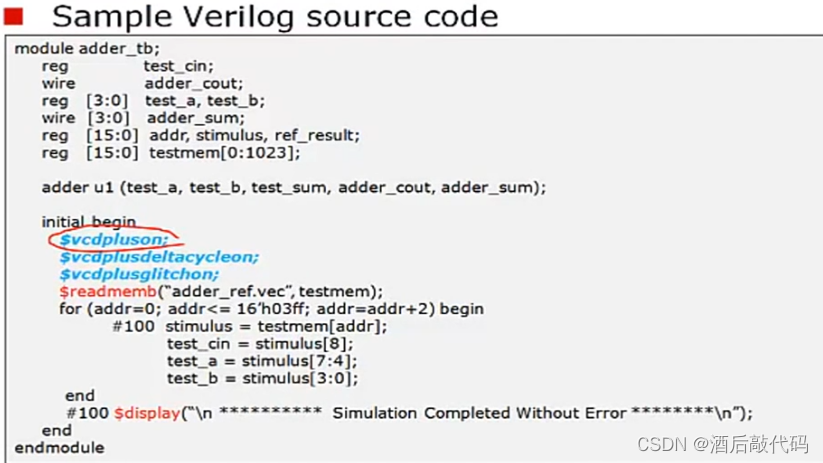

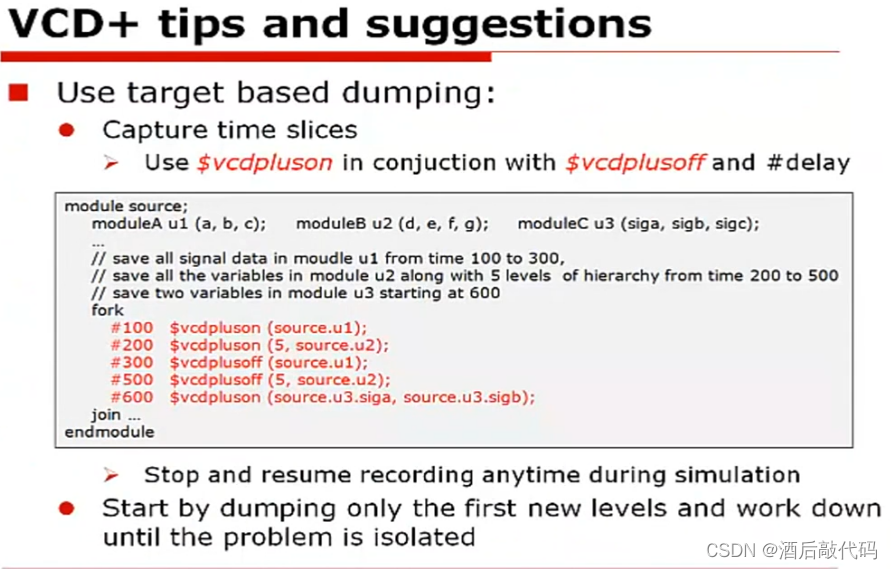

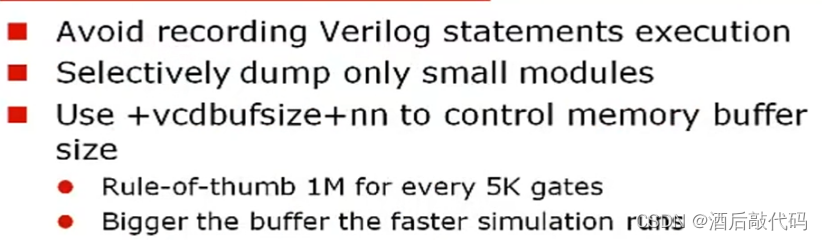

重点是画线句:要在源代码中嵌入系统函数$vcdpluson,便于在仿真过程中将波形、log等等信息全部记录下来,以便后期使用。

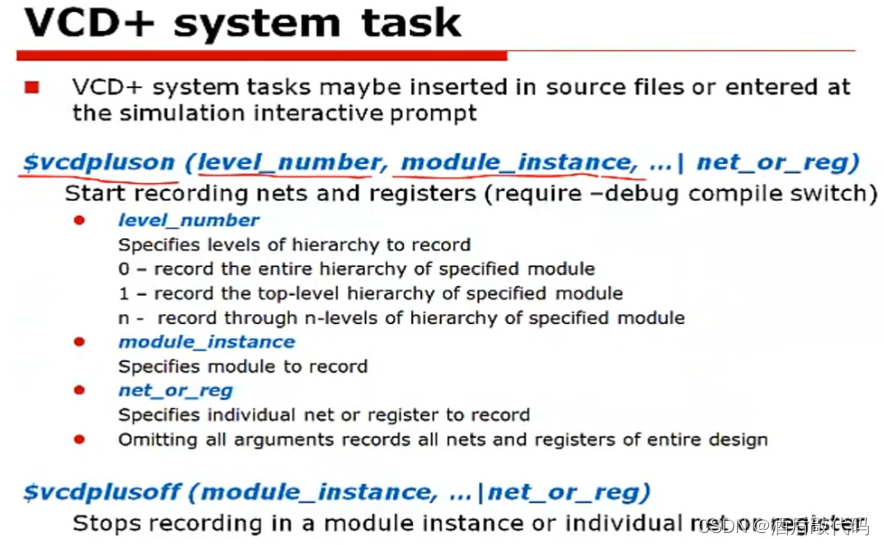

系统函数:

level_number:0表示记录全部层级产生的信息;1表示记录当前层产生的信息;n表示记录n层产生的信息。

module_instance:开始记录产生的信息的开始层级,类似起点层。

net_or_reg:记录哪根线或者哪个寄存器产生的信息。

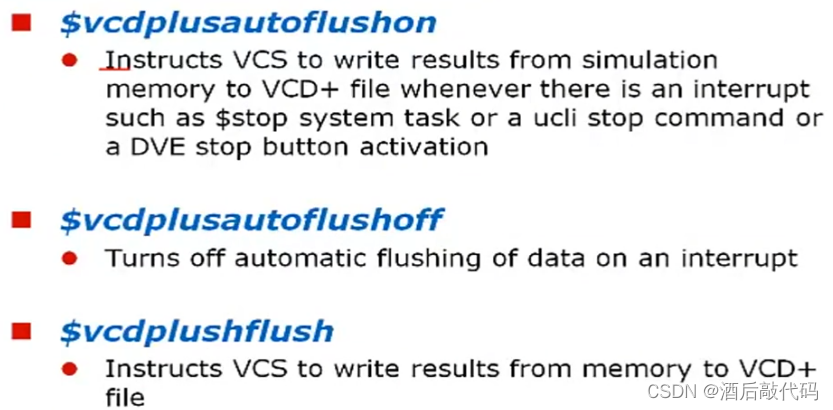

$vcdplusautoflushon:无论何时出现一个断点(例如$stop系统函数、命令行停止命令或者DVE的停止按钮等等),VCS将把仿真结果等信息从仿真内存写入到VCD+文件中。

$vcdplusautoflushoff:关闭在断点时自动写入数据功能。

$vcdplusautoflush:手动通过VCS写入数据到VCD+文件。

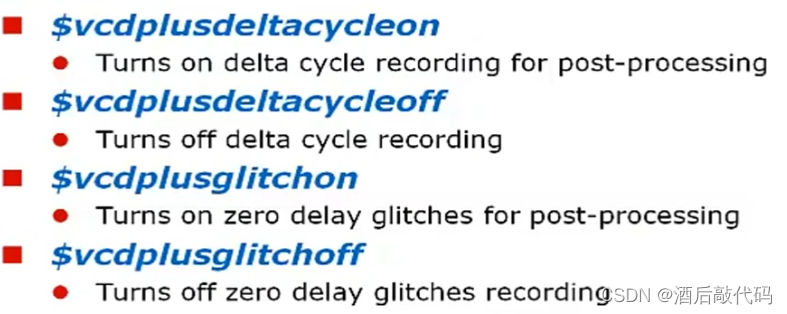

$vcdplusdeltacycleon:

$vcdplusdeltacycleoff:

$vcdplusglitchon:

$vcdplusglitchoff:

$vcdpluson:出现在哪个模块中,该模块以及其子模块的波形都会记录下来。

$readmemb:表示数组中存放的数据为二进制数据,如果结尾为-h则存放的是十六进制数据。

编译:

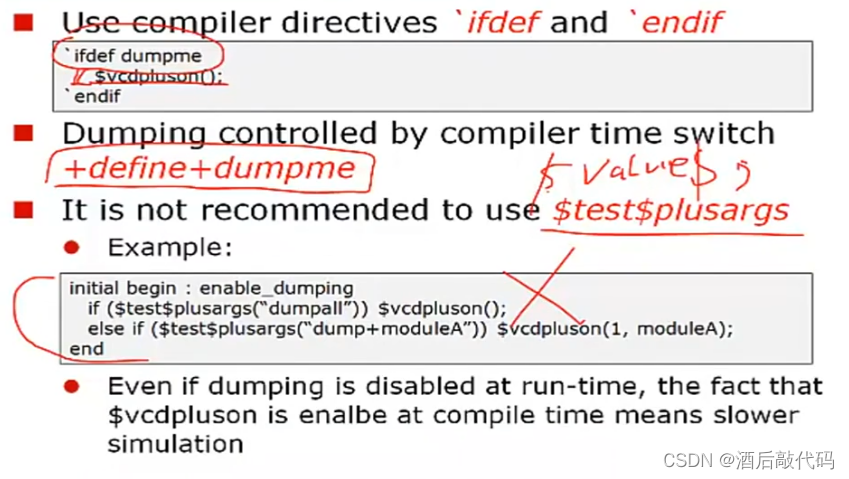

条件编译:通过判断是否定义宏,然后是否执行$vcdpluson()函数;

文章介绍了如何在Verilog源代码中嵌入VCD+系统函数,特别是在testbench文件中的应用,以生成压缩后的波形文件。VCS编译和仿真产生VCD+文件,然后通过DVE的后处理模式进行错误优化。后处理模式适用于复杂电路的调试,具有良好的信号可视性和可追踪性。关键步骤包括使用$vcdpluson记录信息,以及控制数据写入VCD+文件的时机。此外,文章还提到了条件编译和数组数据的表示方法。

文章介绍了如何在Verilog源代码中嵌入VCD+系统函数,特别是在testbench文件中的应用,以生成压缩后的波形文件。VCS编译和仿真产生VCD+文件,然后通过DVE的后处理模式进行错误优化。后处理模式适用于复杂电路的调试,具有良好的信号可视性和可追踪性。关键步骤包括使用$vcdpluson记录信息,以及控制数据写入VCD+文件的时机。此外,文章还提到了条件编译和数组数据的表示方法。

8157

8157

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?