用某个哲学家的一句话,来形容旁路电容真的很合适,“人们总是对挂在嘴边的东西最为无知”。

最近重翻资料,又多了一些运放电源引脚必须放置电容的理解。之前也整理过两次关于旁路电容的笔记,但是随着工作经验的积累,对它总是会有新的体会,所以今天再整理一次,希望也是最后一次,因为这个知识点真的很重要,毕竟有哪个电路板的芯片电源引脚附近是没有电容的呢?

本文重点整理旁路电容,不涉及去耦电容。一般噪声敏感器件(比如运放等)电源引脚放置的都叫作旁路电容,噪声源器件(比如数字芯片、电源芯片等)电源引脚放置的叫去耦电容。简单记忆就是,去耦电容是不让自己影响到别人,旁路电容是为了不让别人影响到我。

不过实际工作中,不必太纠结这两个概念的区分,一律把芯片电源引脚附近的电容称为旁路电容也没什么不可,因为这样更加实用。比如,对于高速时钟芯片,它既是噪声源,同时又对噪声非常敏感,一般都会用LDO供电,那我们该把在它电源引脚放置的电容叫作什么呢?

1 运放的旁路电容怎样放置最好?

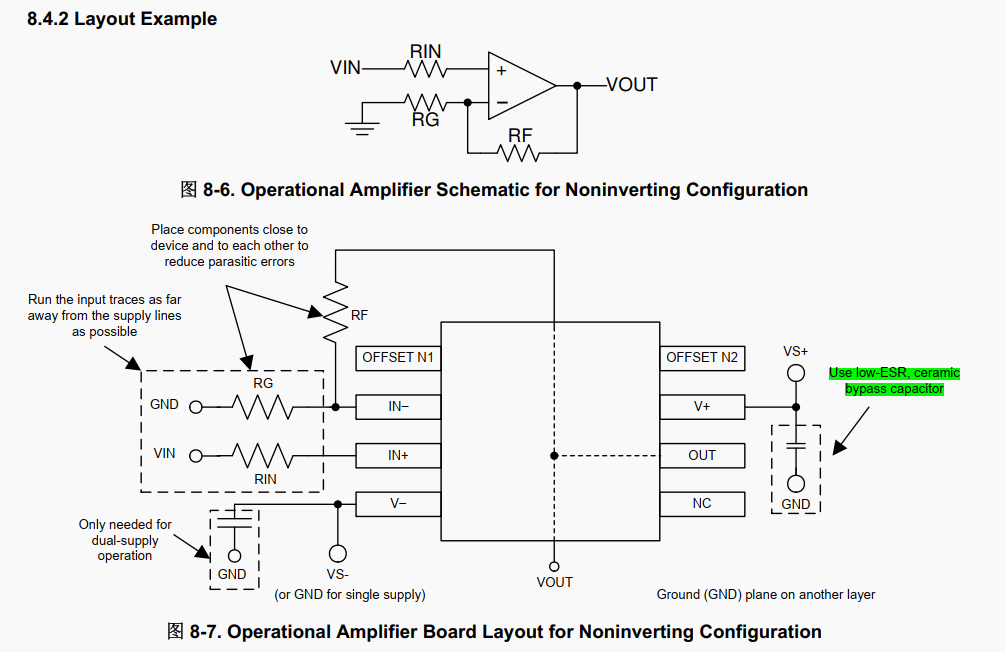

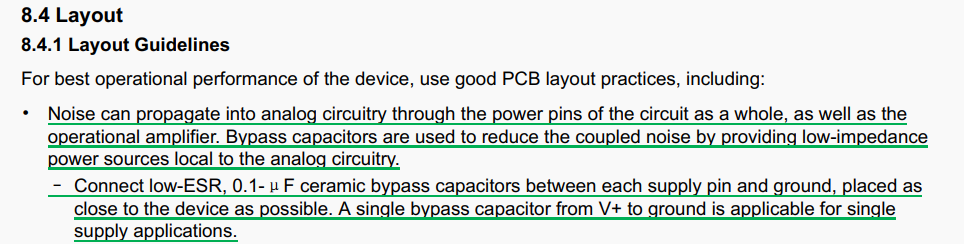

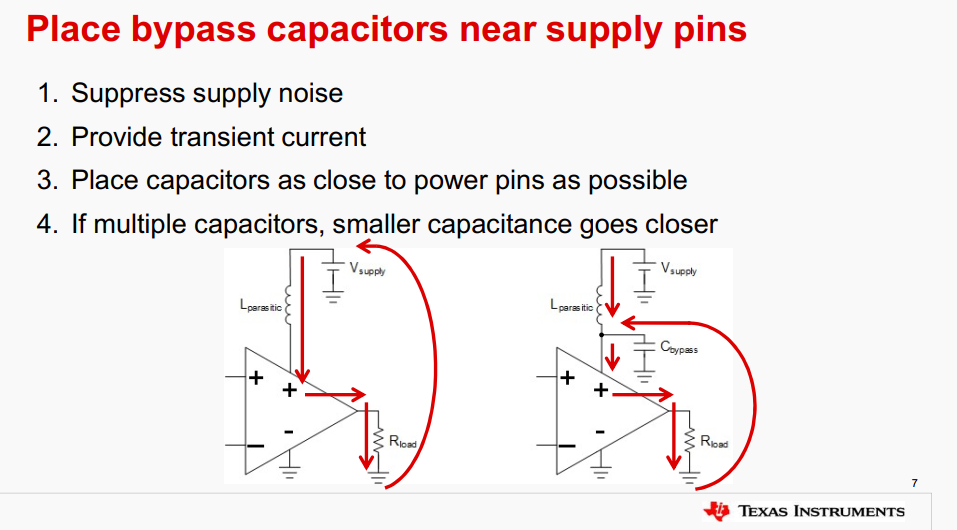

几乎每个运放说明书里,厂家都会对运放旁路电容如何放置进行说明,参见图1.1和图1.2,表1.1对此做了总结。

| 序号 | 注意点 | 说明 |

| 1 | 小封装小容值电容,靠近运放电源引脚放置,越近越好。 | 小封装小容值电容ESL小,滤除高频噪声,提供瞬态电流 |

| 2 | 大封装大容值电容,可以距离运放远一些。如果电路板上有多个运放电路,还可以每两个运放放一个10uF的钽电容。 | 滤除低频噪声等 |

| 3 | 电源走线先经过电容,而后再达到运放电源引脚 | 就像戴口罩,脏空气先要经过口罩再进入鼻腔,口罩才有意义 |

| 4 | 对于双电源运放,Vcc和Vee引脚附近都要放置电容,对于单电源,GND引脚不需要。 | / |

| 5 | 旁路电容的接地端要最小路径到GND层,一般都会打过孔。 | 减小ESL |

2 旁路电容对于运放的四个作用

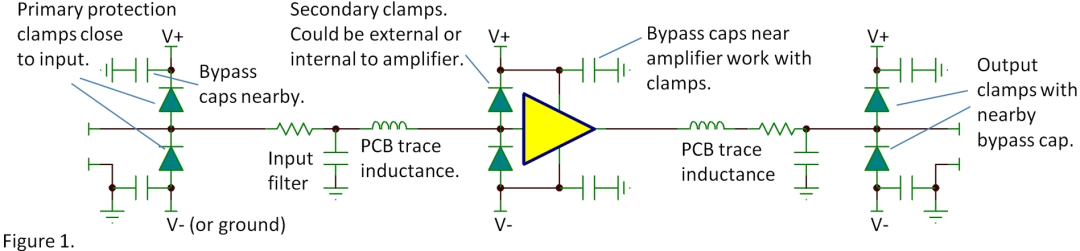

2.1 ESD保护

这是最近学到的又一个运放放置旁路电容的原因,即可以提供ESD保护。图2.1给出了一种运放保护电路的一种最基本的形式,非常值得收藏下来。运放输入端一般都会有保护电路,通常是钳位二极管,参见图2.2,我们都知道静电就是一个脉冲电压,当它出现在输入端,如果运放电源引脚附近有旁路电容,脉冲电流可以直接通过电容直接泄放到低阻抗的GND,可以起到ESD保护作用。如果没有旁路电容,或者放置的不好(ESL高了),脉冲电流可以不会那么容易泄放,路径不会那么直接……当然一般这也不会出现问题,参见图2.1,PCB走线也会有电感电容。

2.2 避免运放震荡

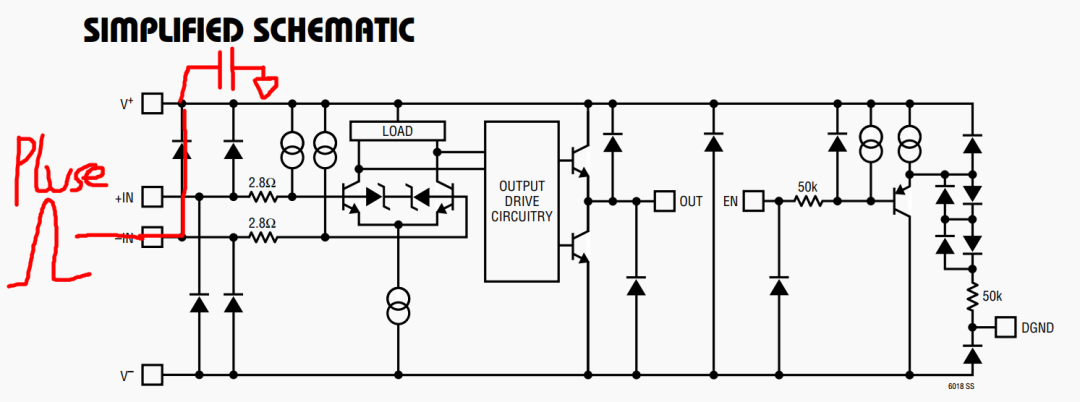

其实这一点我也理解的不好,让我们先知道有这条吧。某个老外写了一本光电设计的书,里面特别提到了这点。它是用波特图解释的,在此之前,我们需要复习一下PSRR的知识点。

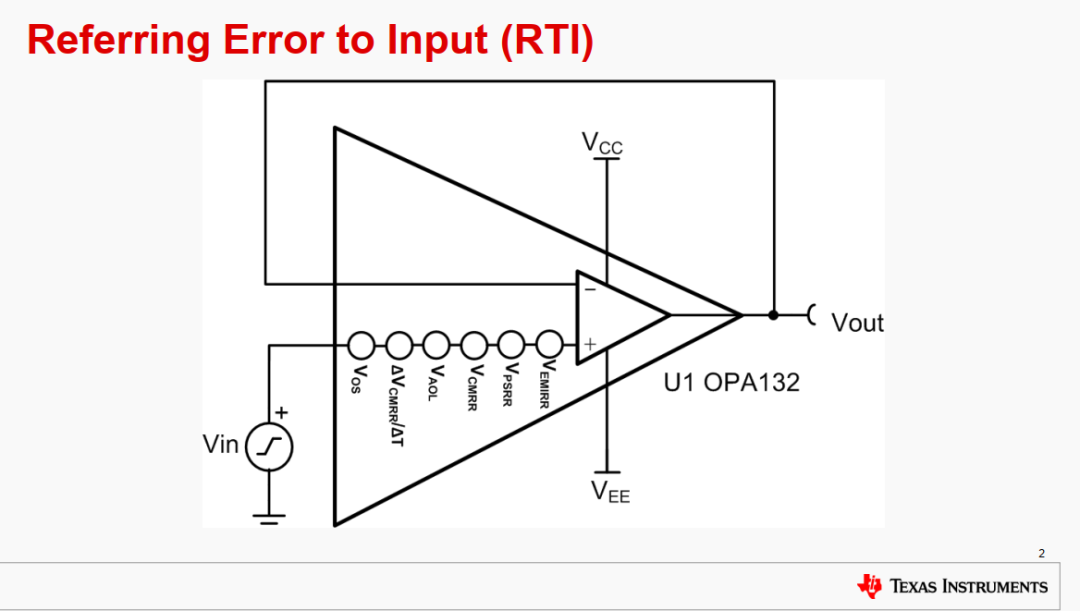

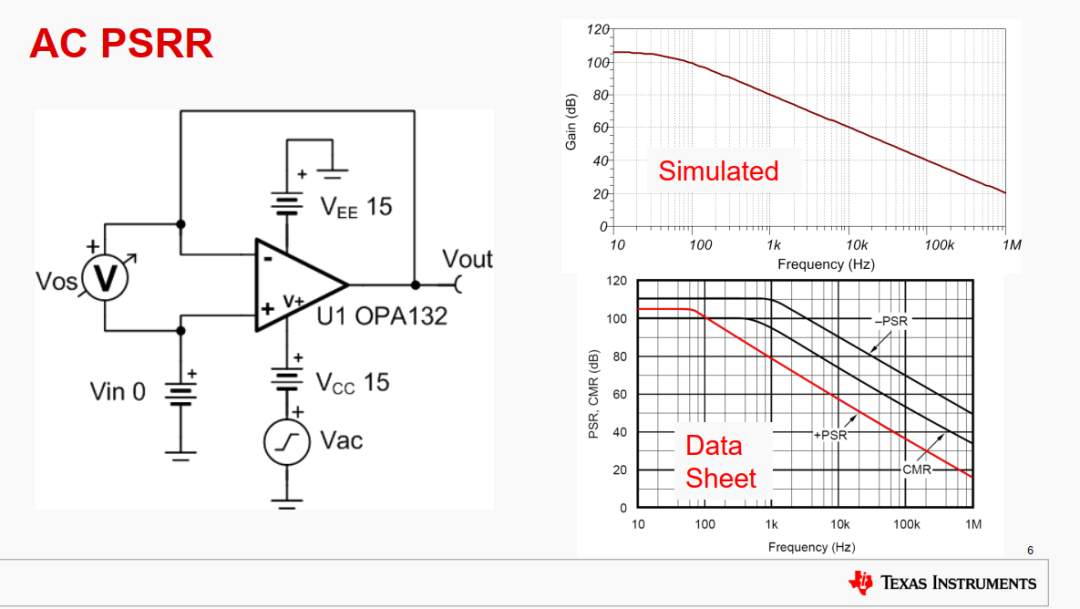

运放的PSRR可以理解成,电源的波动折算到同相输入端,参见图2.3,所以噪声增益越大被放大的倍数也就越大。PSRR随着频率增加而降低,正负电源的PSRR也不相等,通常负电源PSRR更大。那么我们在图2.4可以看到,PSRR类似AOL曲线,有一个pole,极点过后以-20dB/dec滚降,如果电源引脚附近没有电容,或者容值不够,那么由于ESL,很可能在0dB之前就出现了另一个pole,这可能会导致震荡。

当然这个解释不太直观,可能如果想要直观理解不加电容,运放会震荡,可能需要了解一些它的内部结构,比如哪条回路会出现正反馈。在一些文档中都会反复提到,运放的设计是假设了电源是低阻抗、干净的。

2.3 提供瞬态电流

参见图2.5。运放输出脉冲波形,就需要瞬态电流,如果电源与运放之间未放置旁路电容,中间的ESL会有很大的压差,V=L*di/dt。这时电容充当电荷桶的作用。当然,布局时候一定要注意尽量减小ESL。

2.4 滤波

滤波很容易理解,参见图2.6。

3 总结

虽然给运放设置旁路电容的原因不止一两种,有些甚至很难理解,幸运的是,电气方面的问题都是相互关联的,其指向大致相同。正确的旁路电容布局,不仅会滤波效果好,提供瞬态电流能力强,减小震荡风险,还会增强ESD保护。想起了《安娜卡列尼娜》小说的开头,“幸福的家庭都是相似的,不幸的家庭会各有各的不幸”。

当然很多人因为各种限制如电路板尺寸等,并没有严格按照厂家规格书建议去布局旁路电容,也没有出现过任何问题,但稍微谨慎一点可能会更好,也不费事。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?