最近在淘宝看到一款红外摄像头模块,准备使用其参加竞赛,且提供Verilog源码,在此记录零学习FPGA过程。

入门第一步,先点亮开发板的LED灯。模块总体思路是,输入50MHZ的时钟,经过PLL分频得到10MHZ的时钟,传入到时钟分频模块里变成1KHZ的时钟,将1Khz的时钟传入到LED驱动模块。因此LED驱动模块的精度为1ms。

1. 时钟分频模块的实现

//计数器计数到分频的二分之一,时钟翻转;例如8分频,计数到(4 - 1)即可

always@(posedge i_clk,posedge i_rst)

begin

if(i_rst)

r_cnt <= 'd0;

else if(r_cnt == (P_CLK_DIV_CNT >> 1) - 1)

r_cnt <= 'd0;

else

r_cnt <= r_cnt + 1'b1;

end

always@(posedge i_clk,posedge i_rst)

begin

if(i_rst)

ro_clk_div <= 0;

else if(r_cnt == (P_CLK_DIV_CNT >> 1) - 1)

ro_clk_div <= ~ro_clk_div;

else

ro_clk_div <= ro_clk_div;

end 2.LED驱动的实现

//在1Khz的时钟频率下,计数到1000 - 1就到1s

always@(posedge w_clk_1khz,posedge i_rst)

begin

if(i_rst)

r_cnt <= 'd0;

else if(r_cnt == P_LED_COUNT - 1)

r_cnt <= 'd0;

else

r_cnt <= r_cnt + 1;

end

always@(posedge w_clk_1khz,posedge i_rst)

begin

if(i_rst)

ro_led <= 'd0;

else if(r_cnt == P_LED_COUNT - 1)

ro_led <= ~ro_led;

else

ro_led <= ro_led;

end 3.顶层模块实现

CLK_LED_10MHZ CLK_LED_10MHZ_u0

(

.clk_in1(i_clk) ,

.clk_out1(w_clk_10mhz) ,

.locked(w_locked)

);

LED_Driver#(

.P_LED_NUMBER (1 ),

.P_LED_COUNT (1000 ),

.P_LED_ON (1 )

)LED_Driver_u0(

.i_clk (w_clk_10mhz),

.i_rst (w_locked),

.o_led (o_led)

);

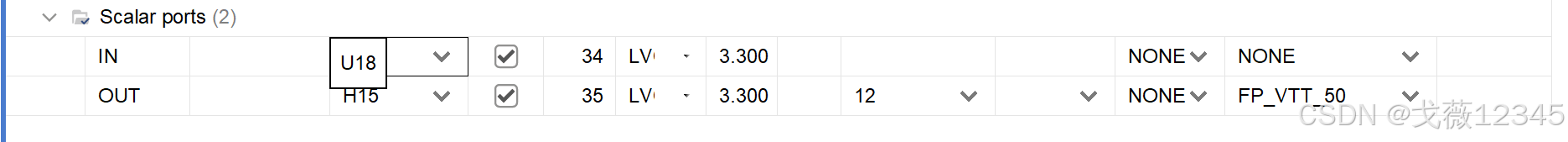

4.管脚分配

使用的是正点原子的领航者,按照原理图分配管脚如下,具体资源百度即可。

5. 总结

LED翻转使用了时钟分频模块,听说在后续学习中会经常用到,因此要打好基础。

下一节更新uart的驱动;

489

489

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?