目录

004——FSM有限状态机(Moore 型、Mealy 型)

005——CDC跨时钟域处理【打两拍】【握手】【异步FIFO】【脉冲展宽】【指示信号】

CDC(Clock Domain Conversion)跨时钟域:

007——存储器问题【SRAM】【DRAM】【SDRAM】【Flash】【EPROM】【EEPROM】

008——FPGA时序分析之关键路径(Critical Path)

009——CDC跨时钟域处理及相应的时序约束【set_clock_groups】【set_max_delay】

011——DFT(Design for Test)可测性设计

013——FIFO深度计算【字节跳动】【大疆】【简便计算公式】

001——什么是STA静态时序分析,有什么作用?

STA静态时序分析(Static Timing Analysis)

(1) 静态时序分析是一种验证数字集成电路时序是否合格的验证方法;

(2) 静态时序分析的前提是同步逻辑设计(重要!),不能分析异步电路;

(3) 静态时序分析工具计算路径延迟的总和,并比较相对于预定义时钟的延迟;

(4) 静态时序分析仅关注时序间的相对关系,而不是评估逻辑功能;

(5) 静态时序分析对所有的时序路径进行错误分析,不需要使用测试向量激活某个路径(与时序仿真的不同点),分析速度比时序仿真工具快几个数量级,克服了动态时序验证的缺陷,适合大规模的电路设计验证,在同步逻辑情况下,能够达到100%的时序路径覆盖;

(6) 静态时序分析的目的是找到隐藏的时序问题,根据时序分析结果优化逻辑或者约束条件,使设计达到时序闭合(Timing Closure);

(7) 静态时序分析能够识别的时序故障:建立时间(Setup)/保持时间(Hold)/恢复时间(Recovery)/移除时间(Removal)检查;最小跳变和最大跳变;时钟脉冲宽度、时钟畸变(Skew、Jitter);总线竞争;不受约束的逻辑通道;关键路径;约束冲突等;

具有代表性的STA工具:

综合工具(DC),布局布线工具(ICC2),时序分析工具(PrimeTime),Xilinx的Vivado中集成了综合、布局布线和时序分析。

代表性企业:Synopsys 。

静态时序分析STA:

(1)setup time

建立时间:时钟沿到来之前,数据必须保持稳定的最短时间,对应的是数据路径的最大延时;

与寄存器的时钟有关。

(2)hold time

保持时间:时钟沿到来之后,数据必须保持稳定的最短时间,对应的是数据路径的最小延时;

与寄存器的时钟有关。

------------------- 分割线 -----------------------------------

建立时间或者保持时间不满足导致数据采样出错,亚稳态现象。

--------------------------------------------------------------------

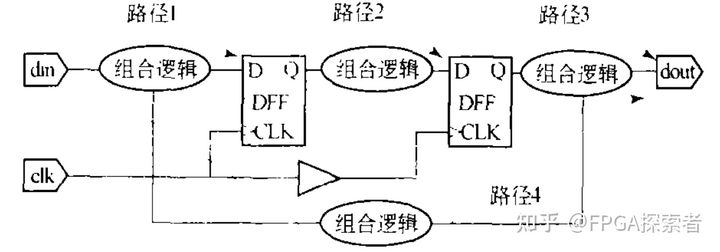

(3)STA 的时序路径

STA 四种时序路径:

路径1:输入端口到寄存器的数据输入 D,

路径2:内部寄存器的时钟输入端到下一个寄存器的数据输入 D,

路径3:内部寄存器的时钟输入端到输出端口;

路径4:输入端口到输出端口。

每条时序路径包含 1 个起点和 1 个终点,

起点只能是设计的基本输入端口或内部寄存器的时钟输入端,

终点只能是内部寄存器的数据输入端或设计的基本输出端口。

对于路径3,分析根据寄存器的Tco延迟和组合路径延迟等分析setup和hold是否满足。

对于路径1和3,可以加入 input delay 和 output delay 来分析,来满足寄存器的建立/保持时间要求。

(4)recovery time

复位的恢复时间:时钟有效沿来临之前,异步复位已经撤销的最小时间(复位已经无效的最小时间,对应于数据的恢复);

即在时钟有效沿来临之前,复位就要撤销,数据就要开始恢复的正常状态的时间。

与寄存器的复位有关。

(5)removal time

复位的移除时间:时钟有效沿来临之后,异步复位需要保持有效的最小时间,类似时钟的 hold。

002——FPGA设计的面积优化和速度优化

(2021乐鑫科技,多选)以下方法哪些是进行面积优化( )。

A: 串行化

B: 资源共享

C: 流水线设计

D: 寄存器配平

E: 逻辑优化

F: 关键路径优化

答案:ABE

解析:

速度优化,提高运行速度:

(1)流水线设计(也是属于关键路径的优化,在关键路径的组合逻辑中插入寄存器);

(2)寄存器配平(重定时);

(3)关键路径优化(减少关键路径上的组合逻辑延时);

(4)消除代码优先级(if_else嵌套、case);

(5)并行化(加法树、乘法树,消除符号运算的优先级);

面积优化,提高资源利用率以降低功耗要求:

(1)串行化;

(2)资源共享;

(3)逻辑优化;

003——FSM有限状态机、三段式状态机

(单选)状态机的编码风格包括一段式、两段式和三段式,下列描述正确的是()

A、一段式寄存器输出,易产生毛刺,不利于时序约束;

B、二段式组合逻辑输出,不产生毛刺,有利于时序约束;

C、三段式寄存器输出,不产生毛刺,有利于时序约束;

D、所有描述风格都是寄存器输出,易产生毛刺,有利于时序约束。

答案:C

解析:

(1)一段式:一个always块,既描述状态转移,又描述状态的输入输出,当前状态用寄存器输出;

(2)二段式:两个always块,时序逻辑与组合逻辑分开,一个always块采用同步时序描述状态转移;另一个always块采用组合逻辑判断状态转移条件,描述状态转移规律以及输出,当前状态用组合逻辑输出,可能出现竞争冒险,产生毛刺,而且不利于约束,不利于综合器和布局布线器实现高性能的设计;

(3)三段式:三个always块,一个always模块采用同步时序描述状态转移;一个always采用组合逻辑判断状态转移条件,描述状态转移规律;第三个always块使用同步时序描述状态输出,寄存器输出。

三段式与二段式相比,关键在于根据状态转移规律,在上一状态根据输入条件判断出当前状态的输出,从而在不插入额外时钟节拍的前提下,实现了寄存器输出。

004——FSM有限状态机(Moore 型、Mealy 型)

(单选)实现同一功能的 Mealy 型同步时序电路比 Moore 型同步时序电路所需要的 ______。

A.状态数目更多

B.状态数目更少

C.触发器更多

D.触发器更少

答案:B

解析:

(1)Mealy型:输出信号不仅取决于当前状态,还取决于输入;

(2)Moore型:输出信号只取决于当前状态;

Mealy型比Moore型输出超前一个时钟周期,Moore型比Mealy多一个状态。

实现相同的功能时,Mealy型比Moore型能节省一个状态(大部分情况下能够节省一个触发器资源,其余情况下使用的资源相同,视状态数和状态编码方式决定),Mealy型比Moore型输出超前一个时钟周期。

005——CDC跨时钟域处理【打两拍】【握手】【异步FIFO】【脉冲展宽】【指示信号】

1.(大疆2020数字芯片)下列关于多bit数据跨时钟域的处理思路,错误的有()

A. 发送方给出数据,接收方用本地时钟同步两拍再使用;

B. 发送方把数据写到异步fifo,接收方从异步fifo里读出;

C. 对于连续变化的信号,发送方转为格雷码发送,接收方收到后再转为二进制;

D. 发送方给出数据,发送方给出握手请求,接收方收到后回复,发送方撤销数据。

答案:A

解析:多bit跨时钟域不能简单使用打两拍,打拍后可能数据错乱;

CDC(Clock Domain Conversion)跨时钟域:

分单bit和多bit传输,其中:

单bit(慢时钟域到快时钟域):用快时钟打两拍,直接采一拍大概率也是没问题的,两拍的主要目的是消除亚稳态;

单bit(快时钟域到慢时钟域):握手、异步FIFO、异步双口RAM;快时钟域的信号脉宽较窄,慢时钟域不一定能采到,可以通过握手机制让窄脉冲展宽,慢时钟域采集到信号后再“告诉”快时钟域已经采集到信号,确保能采集到;

多bit:异步FIFO、异步双口RAM、握手、格雷码;

2. 关于异步处理,以下说法正确的是:

A、静态配置信号可以不做异步处理

B、异步FIFO采用格雷码的原因是为了提高电路速度

C、异步处理需要考虑发送和接收时钟之间的频率关系

D、单比特信号打两拍后可以避免亚稳态的发生

答案:AC

解析:

A. 静态不变,直接采,不会出现亚稳态,因为不会在采集时钟的边沿处发生变化;

B. 异步 FIFO 中确实采用了格雷码,但是目的是为了跨时钟传输,不是为了提高电路速度;

将多 bit 的自然二进制读写地址转成格雷码,相邻数据仅有 1 bit 的不同,可以使用“打两拍”的二级同步器进行读写地址传输;

C. 异步处理需要考虑两个时钟的频率,比如前面提到的

| 单bit(慢时钟域到快时钟域): | 快的一定能采到慢的,用快时钟打两拍; |

|---|---|

| 单bit(快时钟域到慢时钟域): | 快时钟域的信号脉宽较窄,慢时钟域不一定能采到,可以通过握手机制让窄脉冲展宽,慢时钟域采集到信号后再“告诉”快时钟域已经采集到信号,确保能采集到; |

D. 这里的说法有几个问题

(1)像 C 里提到的,快到慢就没办法只使用“打两拍”;

(2)慢到快的单比特信号打两拍,仅仅是降低了亚稳态发生的概率,但是没有消除亚稳态;

亚稳态无法消除,只能降低发生的概率,二级同步不够的时候可以使用三级甚至四级,具体相关的参数是 MTBF 平均无故障时间(Mean Time Between Failure),可以去查阅一下相关的。

本文详细介绍了FPGA设计中的关键概念和技术,包括静态时序分析(STA)的作用、典型工具及其关注的时序路径,如建立时间和保持时间。讨论了FPGA设计的面积优化和速度优化策略,如流水线设计、寄存器平衡和逻辑复制。此外,阐述了有限状态机(FSM)的Moore型和Mealy型以及跨时钟域处理(CDC)的重要性和处理方法,如异步FIFO、握手协议等。还涵盖了数据定点无损量化、存储器类型(SRAM、DRAM等)以及DFT(Design for Test)的可测性设计。最后,探讨了FPGA设计流程和常用的综合仿真工具。

本文详细介绍了FPGA设计中的关键概念和技术,包括静态时序分析(STA)的作用、典型工具及其关注的时序路径,如建立时间和保持时间。讨论了FPGA设计的面积优化和速度优化策略,如流水线设计、寄存器平衡和逻辑复制。此外,阐述了有限状态机(FSM)的Moore型和Mealy型以及跨时钟域处理(CDC)的重要性和处理方法,如异步FIFO、握手协议等。还涵盖了数据定点无损量化、存储器类型(SRAM、DRAM等)以及DFT(Design for Test)的可测性设计。最后,探讨了FPGA设计流程和常用的综合仿真工具。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+