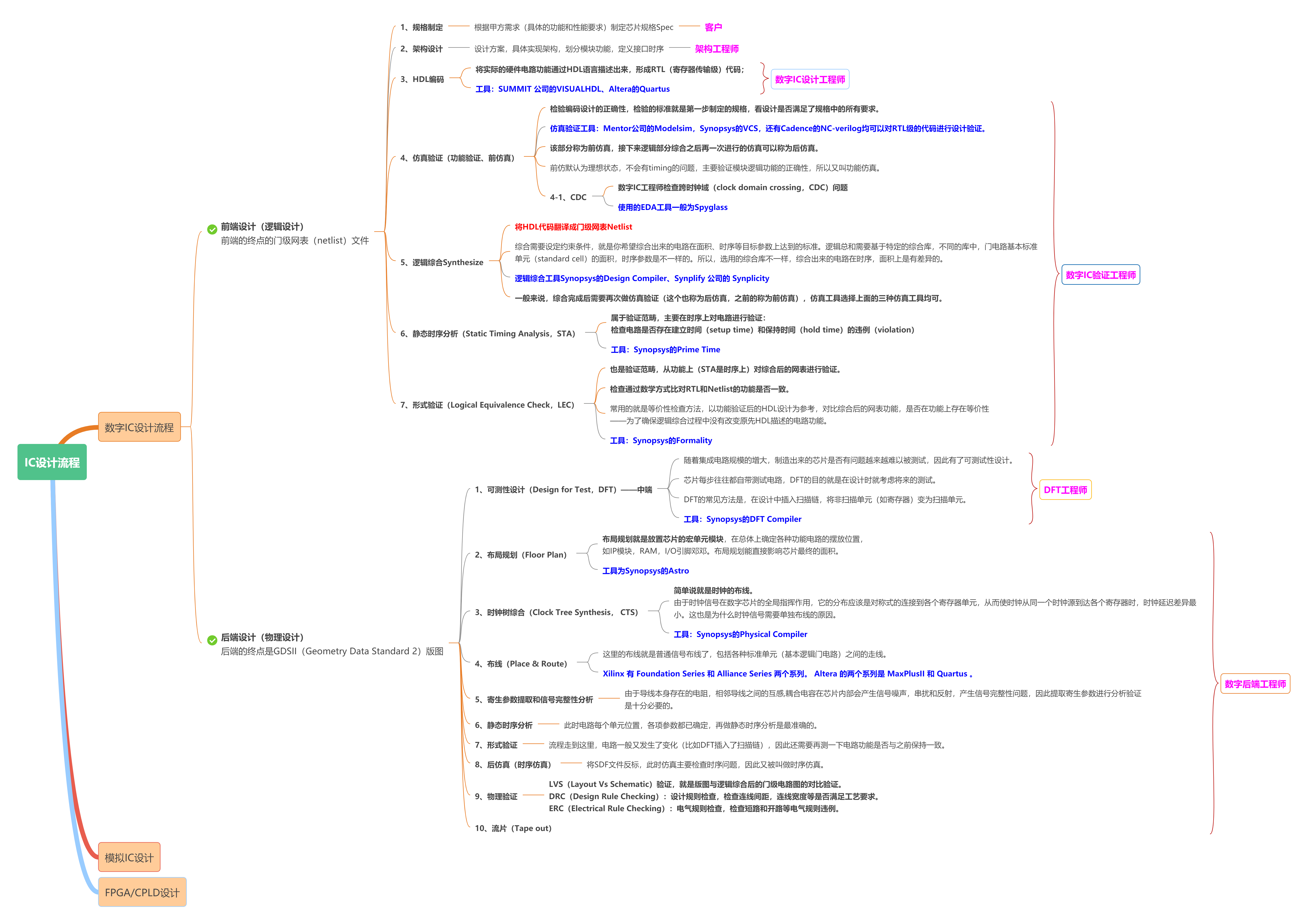

IC设计流程图全览

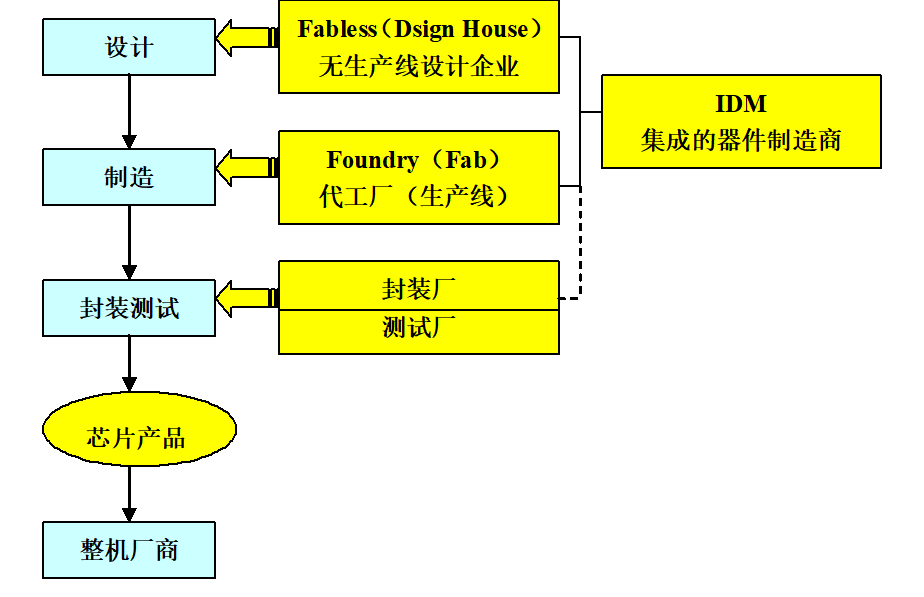

一颗芯片的诞生经历了设计、制造和测试(分别对应集成电路产业链的设计业、制造业和封测业),而每一步都包含了复杂的步骤和流程,如图0-1所示。

图0-1 集成电路产业链 现在,我们重点介绍芯片设计的全流程以及每个流程需要用到的设计工具和需要参与的工作人员。

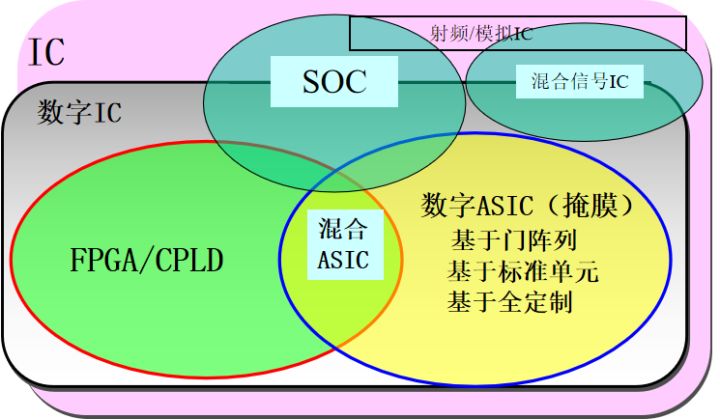

一、IC设计分类

首先对IC设计的分类做个介绍,如图1-1所示。

如图1-1所示,IC设计可以粗分为数字IC设计和射频/模拟IC设计;数字IC设计又可分为ASIC设计和FPGA/CPLD设计;此外还有一部分IC设计采用数模混合设计,如:SOC设计和数模混合信号IC设计。

关于数字IC中的ASIC与FPGA/CPLD的区别:

- ASIC(Application Specific Integrated Circuit,专用集成电路):需制作掩模,设计时间长,硬件不能升级;芯片面积小,性能可以得到较好的优化;适合芯片需求量大的场合:片量用于平摊昂贵的光罩掩模制版费,降低单片生产成本。

- FPGA/CPLD(Field Programmable Gate Array,现场可编程门阵列 / Complex Programmable Logic Device,复杂可编程逻辑器件):不需要后端设计/制作掩模,可编程;开发门槛较低,设计时间较短,可方便和快速地升级优化硬件;芯片面积大,性能不够优化 ;适合芯片需求量小的场合:不用支付昂贵的光罩掩模制版费。作为数字ASIC设计流程中的必要步骤:ASIC设计中前端设计的FPGA

本文详细介绍了集成电路(IC)的设计流程,包括数字IC和模拟IC的设计分类,以及数字IC中的ASIC和FPGA/CPLD的区别。重点阐述了数字IC设计的前端设计、功能验证和后端实现,涉及到的主要EDA工具如Synopsys、Cadence和Mentor的产品。此外,还提到了FPGA/CPLD设计流程和模拟IC设计的相关工具。整个流程中,设计人员需要考虑功能性能、成本、使用寿命和上市时间等因素,确保芯片设计的成功。

本文详细介绍了集成电路(IC)的设计流程,包括数字IC和模拟IC的设计分类,以及数字IC中的ASIC和FPGA/CPLD的区别。重点阐述了数字IC设计的前端设计、功能验证和后端实现,涉及到的主要EDA工具如Synopsys、Cadence和Mentor的产品。此外,还提到了FPGA/CPLD设计流程和模拟IC设计的相关工具。整个流程中,设计人员需要考虑功能性能、成本、使用寿命和上市时间等因素,确保芯片设计的成功。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6793

6793

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?