概述

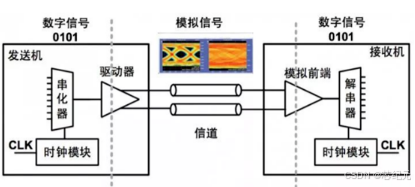

SerDes是英文SERializer(串行器)/DESerializer(解串器)的简称。它是一种主流的时分多路复用(TDM)、点对点(P2P)的串行通信技术。即在发送端多路低速并行信号被转换成高速串行信号,经过传输媒体(光缆或铜线),最后在接收端高速串行信号重新转换成低速并行信号。这种点对点的串行通信技术充分利用传输媒体的信道容量,减少所需的传输信道和器件引脚数目,提升信号的传输速度,从而大大降低通信成本。

结构

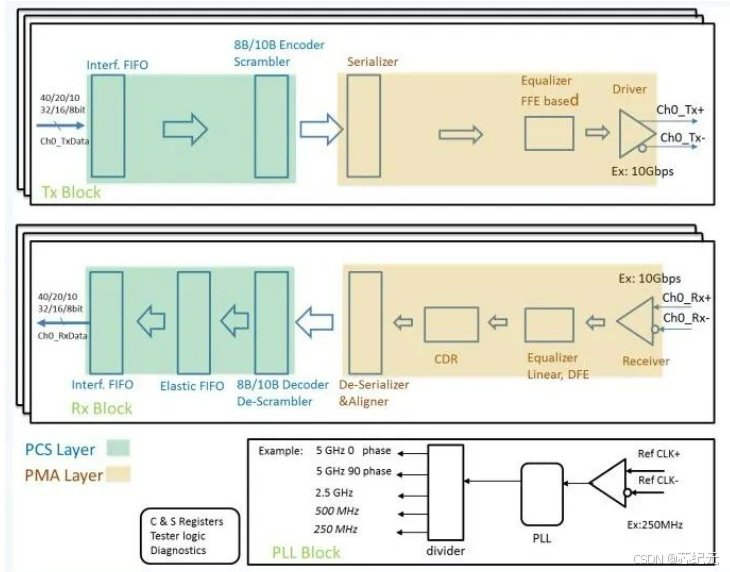

一个典型SerDes收发机由发送通道和接收通道组成:编码器、串行器、发送器以及时钟产生电路组成发送通道;解码器、解串器、接收器以及时钟恢复电路组成接收通道。顾名思义,编码器和解码器完成编码和解码功能。串行器和解串器负责从并行到串行和从串行到并行的转换。串行器需要时钟产生电路,时钟发生电路通常由锁相环(PLL)来实现。解串器需要时钟和数据恢复电路(CDR),时钟恢复电路通常也由锁相环来实现。发送器和接收器完成差分信号的发送和接收,其中LVDS和CML是最常用的两种差分信号标准。另外还有一些辅助电路也是必不可少的,例如环路(loopback)测试、内置误码率测试等等。

SerDes芯片的设计需要模拟和数字两方面即混合信号的设计经验。例如锁相环的设计,其中压控振荡器属于模拟电路,而检相器和分频器属于数字电路。SerDes芯片普遍采用低成本、低功耗的CMOS工艺,但CMOS工艺往往达不到高速混合信号的速度要求,因此设计人员必须采用特殊的高频宽带电路设计技术来提高电路速度和带宽。另外,模拟和数字电路共存于同一硅片上,容易产生电源同步噪声及信号串扰等问题,因此保持信号的完整性是混合信号设计人员面临的一项挑战。

SerDes技术主要用来实现ISO模型的物理层,SERDES通常被称之为物理层(PHY)器件。

从物理层来说,SerDes主要由物理介质相关子层( Physical Media Dependent,PMD)、物理媒介适配层(Physical Media Attachment,PMA)和物理编码子层( Physical Coding Sublayer,PCS )所组成,且收发器的 TX发送端和RX接收端功能独立。

各物理层的作用:

1.PCS层,负责数据流的编码/解码,是标准的可综合CMOS数字逻辑,可以通过逻辑综合实现 软硬综合实现。

2.PMA层,是数模混合CML/CMOS电路,负责负责串化/解串化,是理解SerDes区别于并行接口的关键。

3.PMD层,一般用光模块代替实现光电/电光转换。

应用

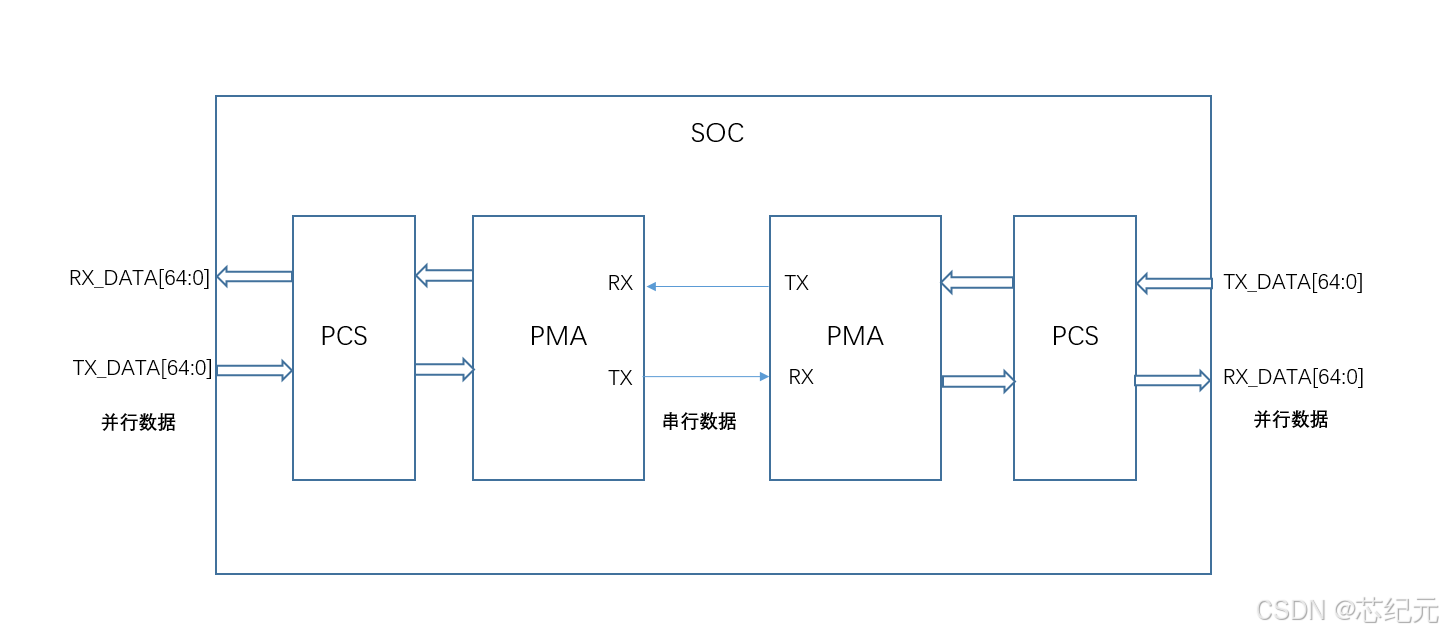

如下图所示,SOC在使用SerDes时一般会使用两个,从整体来看,信号是并入并出,但是信号实际上在内部先并转串再串转并。

优缺点

优点:

- 点对点的串行通信减少所需的传输信道和器件引脚数目,从而大大降低通信成本。

- 采用差分信号传输,增强了链路的抗干扰能力,只要一对差分线即可完成数据收发。

- 采用时钟和数据恢复技术(CDR)代替同时传输数据和时钟,解决了限制数据传输速率的信号时钟Skew问题。

缺点:高速串行接口模拟部分设计复杂度高,调试难度大。

总结

目前,商用基于SerDes架构的通信协议最高可实现单通道112Gbps的速率,在未来高带宽、低成本的应用领域会 越来越广泛。

1320

1320

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?