正文

大家好,我是bug菌~

随着半导体、芯片的快速发展,嵌入式平台越来越趋向于廉价、高性能的方向发展,外设接口丰富度和高性能愈来愈突出,那么今天bug菌跟大家介绍一下一种高速串行扩展总线-PCIe,相信不久的将来大家会用到此接口。

1

什么是PCIe

PCIe英文名:Peripheral Component Interconnect Express,它是一种高速串行计算机扩展总线标准,旨在取代传统的并行PCI和AGP总线。它提供点对点的连接,高带宽和低延迟,是现代计算机系统中常见的接口,并广泛用于连接各种外部设备,如显卡、网卡、存储设备等。

比如说你的平台上SD卡不再满足项目需求,考虑挂个固态硬盘,PCIe接口的高带宽和低延迟特性使其成为高性能固态硬盘的理想选择。比如NVMe SSD,NVMe(Non-Volatile Memory Express)是专为PCIe接口设计的高性能固态硬盘协议,直接使用PCIe总线进行数据传输,具有极高的读写速度和低延迟。

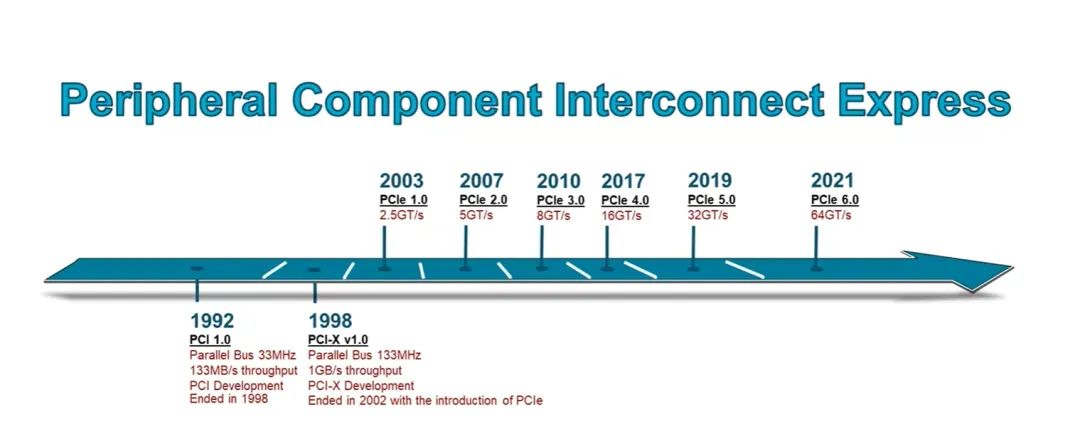

上图是TI整理的PCIe接口发展路线,可以了解到PCIe继承与PCI,并且初期的PCIe1.0的每条通道的传输速率为2.5 GT/s(注意单位是:每秒传输2.5亿次信号,GT/s实际上是指每秒内在PCIe总线上发生的数据传输次数),然后每个时间阶段几乎翻倍的增加,不过目前在嵌入式主流高端系统平台PCIe3.0接口的较多,再往上就是更加数据密集型应用和高性能计算需求的系统了。

2

PCIe与PCI的异同

虽然PCI主要用于早期的计算机系统,但是面对PCIe的普及,进行一下对比能够更加突出PCIe的进步与优秀。

PCI使用并行总线架构,通过多个并行数据线同时传输数据,并且所有连接到同一总线的设备共享总带宽,这会导致带宽瓶颈,尤其是在多设备同时工作的情况下,大家都知道并行通信比较依赖时钟同步,对信号完整性提出了比较严苛的要求,所以PCI基本也就是MB/s的水平,并行通信的物理限制,带宽提升空间有限。

然而PCIe采用点对点的串行通信方式,通过高频率的串行链路进行数据传输。每个设备都有自己的专用通道,我们称之为Lane,以后接触这个也是接口性能指标,不需要与其他设备共享带宽。数据传输不依赖于全系统的时钟同步,而是通过8b/10b编码和独立时钟恢复技术实现高速传输,比如PCIe 3.0提高到1 GB/s,通过增加通道数(如x1、x4、x8、x16等),可以进一步提高总带宽。

PCIe支持高级电源管理(如Active State Power Management, ASPM),可以动态调整功耗,提高能效,更重要的是支持热插拔,维护也比较方便。

3

PCIe链路拓扑

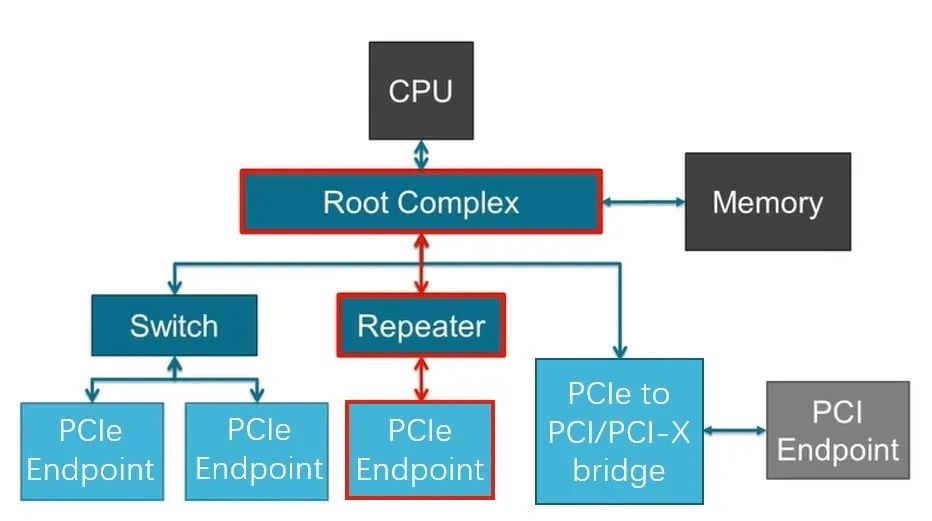

PCIe使用树型拓扑结构,这种结构有助于管理和优化数据流动,并提供灵活的连接选项和高带宽的数据传输能力,一般由根复合体(Root Complex),中继器(Repeater),终端设备(Endpoint)等类型的PCIe设备组成。

关于PCIe树型拓扑结构中常见设备的简要描述:

根复合体(Root Complex):

根复合体是CPU和PCIe总线连接的接口,也是PCIe总线的起点和管理者,通常集成在主板的芯片组或处理器中。它负责初始化PCIe总线、分配带宽、管理数据流量,并提供与主机处理器或芯片组的接口,负责存储器域到PCIe总线域的地址转换。

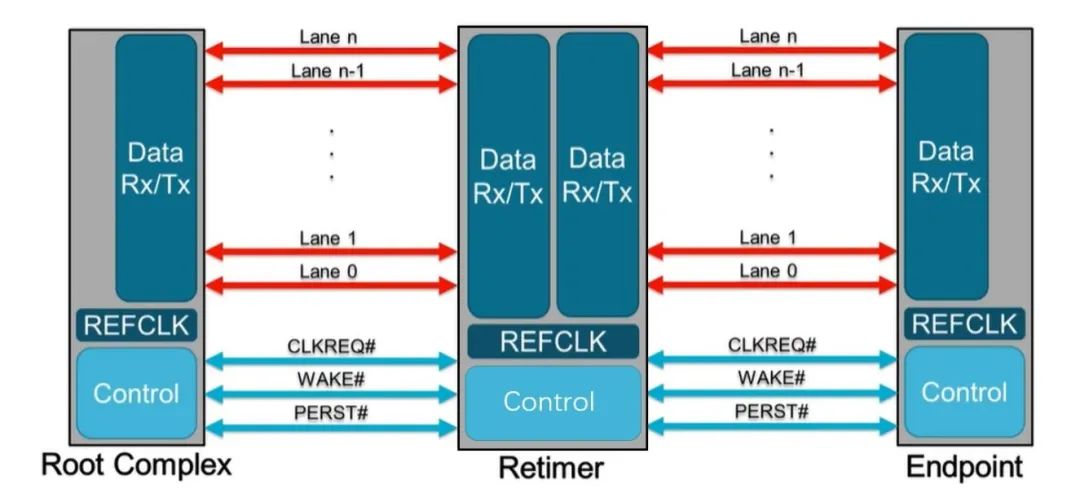

中继器(Repeater):

中继器在PCIe拓扑中起到信号放大和延长传输距离的作用。它们能够增强PCIe信号以便跨越更长的物理距离,同时确保数据的可靠传输。

终端设备(Endpoint):

终端设备是PCIe链路的终点,包括各种外围设备如显卡、存储控制器SSD、网卡等。每个终端设备连接到PCIe总线的一个或多个通道(Lanes),通过这些通道进行数据传输。

交换机(Switch):

交换机允许多个PCIe设备通过单个根复合体连接到主板上的PCIe总线,提供额外的端口和带宽管理功能。它们可以在多个设备之间实现数据的交换和路由,有效地扩展PCIe总线的连接能力和灵活性。

4

PCIe通信大致过程

PCIe协议确实定义了三层结构,分别是物理层、数据链路层和事务层。

物理层:

功能:物理层负责电气接口和信号传输,确保数据能够在设备之间物理传输。

组成:包括发送器和接收器、电气规范、线路编码(如8b/10b编码)、时钟恢复等。

任务:处理电气特性、介质访问控制、链路初始化和维护。

数据链路层:

功能:数据链路层负责数据包的可靠传输,包括差错检测和纠正、流量控制等。

组成:包括数据包组装和解包、序列号管理、ACK/NACK机制、链路层控制包(DLLP)的处理。

任务:确保数据传输的完整性和顺序,通过错误检测(如CRC校验)和重传机制来保证数据的可靠性。

事务层:

功能:事务层负责高层协议数据包的创建和解释,管理和处理端到端的事务,如读写请求、配置事务等。

组成:包括事务层包(TLP)的生成和解析、地址映射、路由选择、事务管理。

任务:处理来自CPU或其他主设备的命令,将其转换为适当的PCIe事务,并将响应返回。

这样去描述PCIe通信还是比较抽象,其实可以把它简化为如下通信过程:

链路初始化:

PCIe链路初始化过程包括电气初始化、链路训练和状态检测、链路激活和确认、配置空间访问和设备枚举,以及高级配置和优化,这里就不详细展开了,比较复杂,感兴趣的朋友再去研究。

发送端(PCIe发起器)和接收端(PCIe终端)进行物理层的握手协商,包括速率、信号编码方式等参数的确定。握手完成后,链路将进入已建立状态,准备进行数据传输。

数据传输准备:

PCIe数据传输准备阶段包括数据缓冲、数据编码和解码、数据打包和解包、数据传输协议、时钟同步、错误检测和纠正,以及传输开始和结束标志等步骤。

发送端将待传输的数据封装成事务层包(Transaction Layer Packet,TLP),并加上错误检测和流量控制信息。发送端生成数据链路层包(Data Link Layer Packet,DLLP),用于发送链路层控制信息,如序列号管理、流量控制等。

数据传输:

发送端将封装好的TLP和DLLP通过物理层进行传输,经过链路的中转和路由选择,最终到达接收端。

接收端对接收到的数据进行解包和校验,确认数据的完整性,并返回ACK(确认)或NACK(否认)给发送端。

错误处理与重传:

如果接收端检测到数据传输中的错误(如CRC校验失败),将向发送端发送NACK信号。发送端在接收到NACK后,将重传有错误的数据包,直到接收端无法检测到错误为止。

事务完成与响应:

接收端在成功接收到数据后,对其进行处理,执行相应的操作(如读写内存、执行配置等)。接收端生成响应数据,并封装成TLP发送回发送端,用于确认和结果的反馈。

链路关闭:

在数据传输结束后,发送端和接收端可以选择关闭链路,释放相关资源。

这是一个简化的PCIe通信过程,实际的通信过程还涉及更多的细节和协议规范,这里就不过多介绍了。

最后

好了,今天就跟大家分享这么多了,如果你觉得有所收获,一定记得点个赞~

bug菌唯一、永久、免费分享嵌入式技术知识平台~

推荐专辑 点击蓝色字体即可跳转

☞ MCU进阶专辑

☞ “bug说”专辑

☞ 专辑|手撕C语言

☞ 专辑|经验分享

2876

2876

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?