Exams/2013 q2bfsm

思路:

在进行101验证时使用寄存器存储10且此时为1即为101序列,可切换状态

在进行2bit中是否存在1时可使用计数(因只计数2拍,故只用了1bit记0 1 )当计数到1时判断上一时刻(y_reg)内和当前时刻是否有1 ,若有则到输出1状态,若无则到输出0状态。

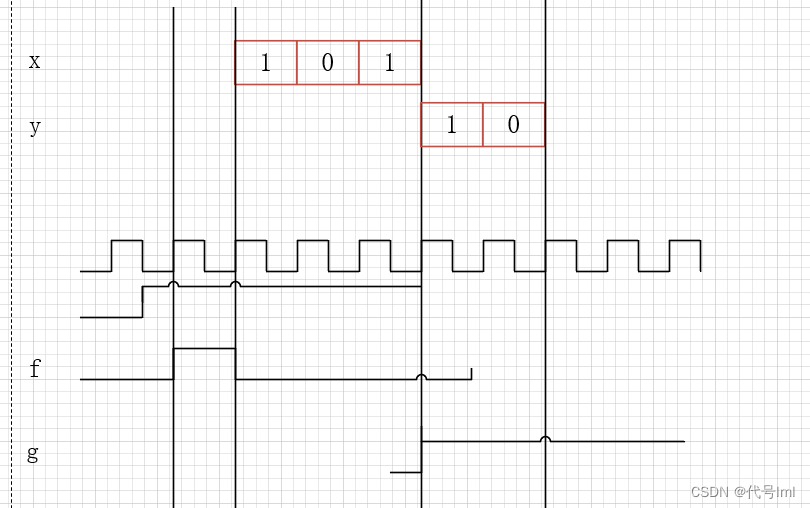

一个简单的随手画的波形图,供参考

module top_module (

input clk,

input resetn, // active-low synchronous reset

input x,

input y,

output f,

output g

);

localparam [2:0]A = 0,B = 1, C = 2 , D = 3,E = 4,F = 5;

reg [2:0]CS , NS;

always@(posedge clk)begin

if(!resetn)

CS <= A;

else

CS <= NS;

end

always@(*)begin

case(CS)

A : NS = B;

B : NS = C;

C : NS = (x_reg[1:0] ==2'b10 && x == 1)?D:C;

D : NS = y_cnt?((y_reg ||y)?E:F):D;

E : NS = E;

F : NS = F;

endcase

end

reg [1:0]x_reg;

always@(posedge clk)begin

if(CS != C)

x_reg <= 2'b0;

else

x_reg <= {x_reg[0],x};

end

reg y_reg;

reg y_cnt;

always@(posedge clk)begin

if(CS!= D)begin

y_reg <= 0;

y_cnt <= 0;

end

else begin

y_reg <= y;

y_cnt <= 1;

end

end

assign f= (CS == B);

assign g = (CS == D)||(CS == E);

endmodule

这篇博客详细介绍了如何利用寄存器存储和状态转换来实现101序列验证,并通过计数器检测2位序列中的1。通过案例展示了在时序逻辑设计中,如何结合状态机和计数器技术来控制输出信号。

这篇博客详细介绍了如何利用寄存器存储和状态转换来实现101序列验证,并通过计数器检测2位序列中的1。通过案例展示了在时序逻辑设计中,如何结合状态机和计数器技术来控制输出信号。

700

700

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?