1 continue

- 只能用于循环语句

- 结束本次循环,继续下一次循环

module continue_loop();

initial begin

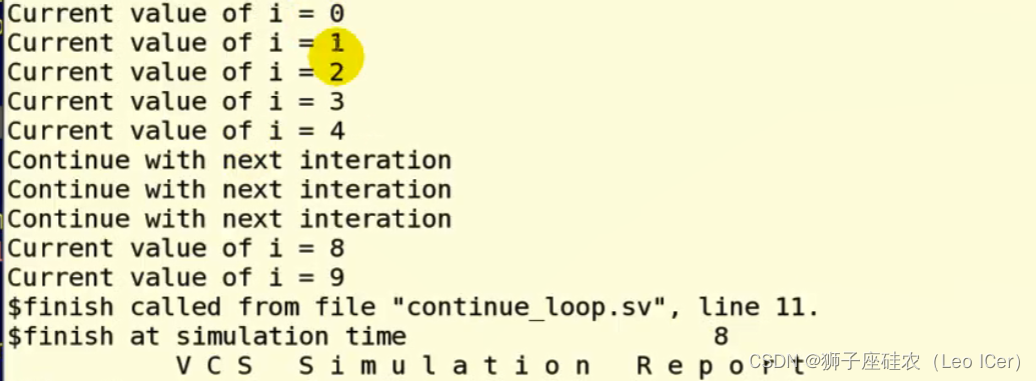

for(int i=0; i<10; i++) begin

if((i>=5)&&(i<8)) begin

$display ("Continue with next interaction");

continue;

end

#1 $display ("Current value of i =%g",i);

end

#1 $finish;

end

endmodule

仿真命令:vcs -R -sverilog continue_loop.sv

当i的值在(i>=5)&&(i<8)范围内,执行continue,则会执行 if((i>=5)&&(i<8)) begin~~end循环。

2 break

- 只能用于循环语句

- 破坏循环,跳出循环,不能在执行循环语句

仿真结果:

3 return

- 可以用于循环语句

- 结束循环

- 也可以用于task和function

- 结束task和function

- 结束task和function

339

339

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?