不管了,不学完这个不睡觉!!!

TIM定时器中断

原理 :对输入的时钟进行计数,并在计数值达到设定值时触发中断

计数器:记录时钟周期,达到设定值后产生溢出。

时钟源与预分频器:设定计时频率,控制定时器的速度。

自动重载寄存器(ARR):设定计数器的最大值。

工作模式:支持计时、PWM生成、输入捕获和输出比较等功能。

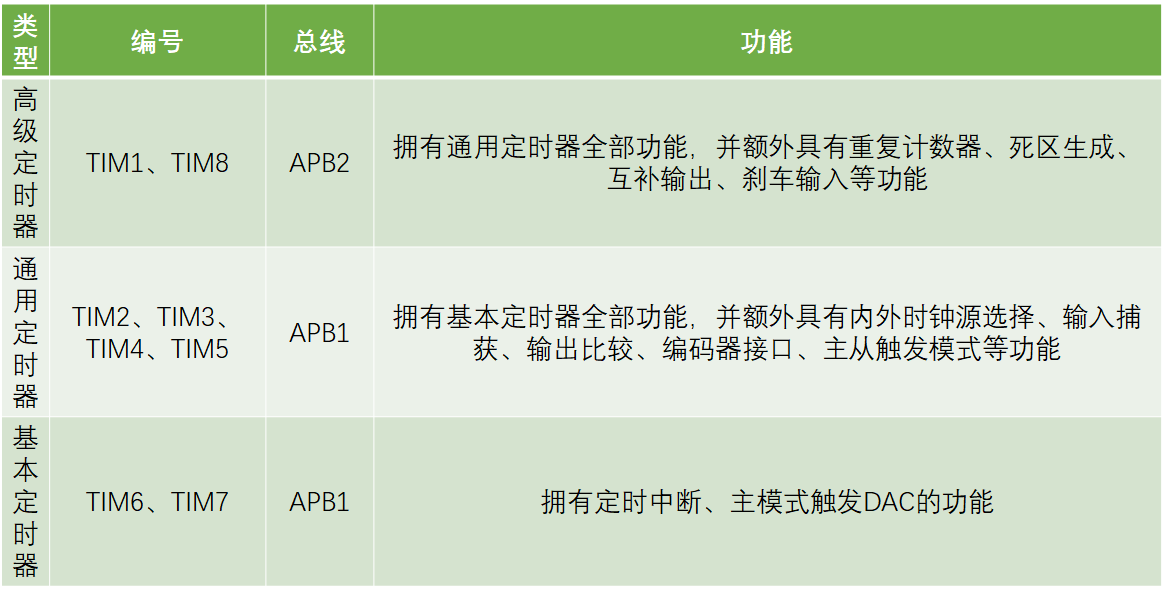

1. 分为了高级定时器、通用定时器、基本定时器三种类型

STM32F103C8T6有TIM1~TM4。总线的时钟设置要注意。

**

(三种定时器框图看不懂)

#=======================================================================#

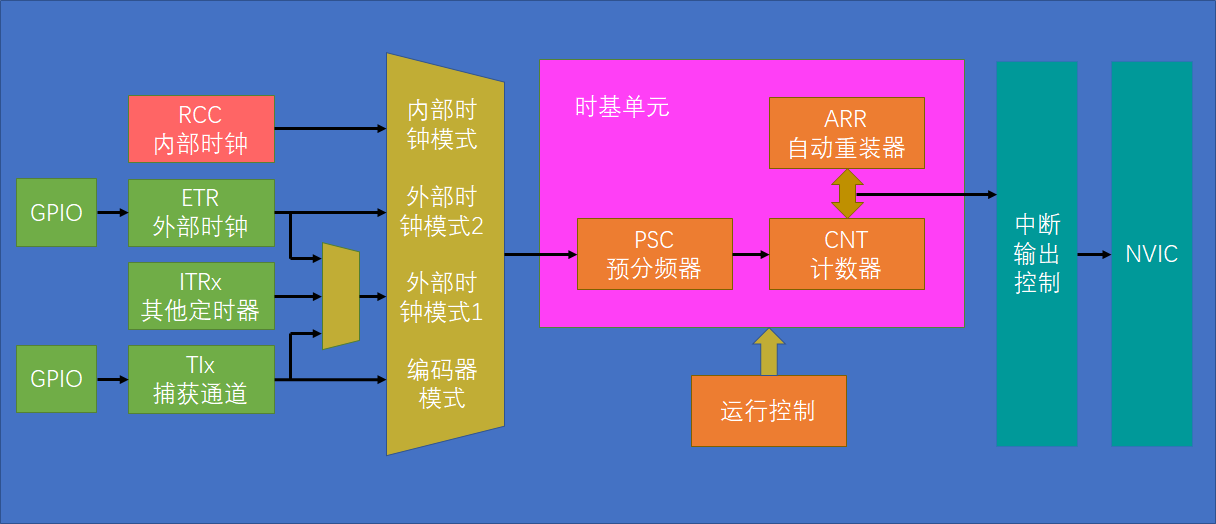

2. 定时中断基本结构

PSC:将输入时钟信号按设定比例分频,降低定时器的计数频率。

CNT:是定时器内部计数过程的核心。它根据预分频器输出的时钟信号进行计数,达到设定的最大值后产生溢出事件。计数器可设置为向上计数、向下计数或中心对称计数

计数器无预装时序:计数器直接从 0 开始计数,且没有使用ARR预设计数值的情形。这种情况下,计数器的工作是基于简单的增计数或减计数,不依赖于预设的计数值。

计数器有预装时序:计数器的计数值通过ARR进行预设。

ARR:是定时器或计数器中的一个寄存器,用于设置计数器的最大值。当计数器的值达到ARR值时,它会自动重载并重新开始计数。

#=======================================================================#

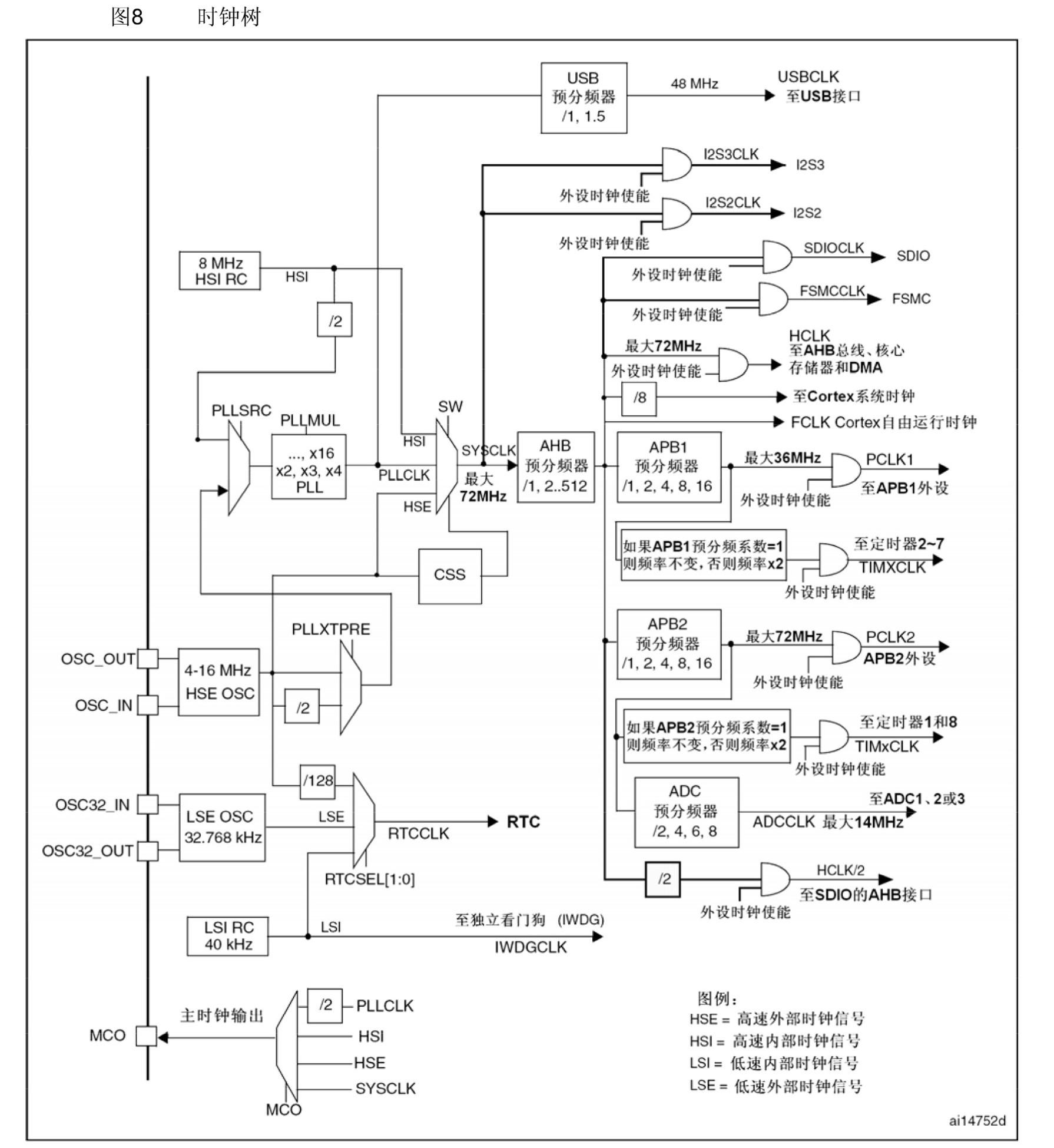

3. RCC时钟树

这里也没太明白,先学代码实践一下看看。。。难啊,,,

以中间的**AHB分频器**为界,左侧是时钟的"产生电路",右侧是时钟的"分频电路",产生电路通过晶振作为振荡源来给为整个STM32芯片提供时钟源,分频电路根据输出到不同位置的外设来选择自己的时钟

时钟产生电路,默认的系统时钟SYSCLK是72MHz,由内部高速RC/外部高速石英/外部低速(专供32.768KHz给RTC实时时钟提供)/内部低速RC(看门狗时钟)振荡器组成,其中系统选择的72MHz是通过内部的8MHz时钟进入外部晶振时钟驱动的"PLL锁相环"进行倍频后得到的,也就意味着当"外部时钟失灵"将导致定时器中断误差让系统将会以更慢的原8MHz内部时钟运行

时钟输出电路,AHB总线控制系统时钟的分频系数(1为不分频),AHB1总线时钟36MHz(分频系数为2),为保证定时器内部基准时钟同步,AHB1另开线路为定时器2~7外设提供72MHz倍频时钟(定时器1/8为AHB2连接),函数RCC_APB2/1PeriphClockCmd通过与门的外设时钟使能来打开时钟

944

944

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?