超低电压能量高效混合全加器电路设计

摘要

近年来,超低电压(ULV)操作在实现最小能耗方面变得越来越重要。

本章旨在降低全加器电路在近阈值区域工作时的能耗。提出了一种新的混合全加器电路,该电路结合了CMOS逻辑和传输门(TG)逻辑,并采用动态阈值MOS(DTMOS)方案。DTMOS是一种体偏置方案,通过动态调节晶体管的阈值电压来提升超低电压操作下的性能。计算了能量、功耗、延迟和能效积(EDP)等性能指标,并与传统CMOS全加器进行了比较。仿真采用 Cadence 90纳米技术,在0.2伏特的超低电压(亚阈值区域)下进行。结果表明,与静态CMOS结构相比,所提出的采用DTMOS方案的混合全加器电路在延迟上节省超过26%,能耗降低15%,能效积(EDP)减少38%。

关键词 CMOS · DTMOS · 能量消耗 · 传输门 · ULV 操作

1 引言

随着技术的进步以及对移动电话、笔记本电脑和微传感器网络等便携式电池供电应用和能量受限应用的需求不断增长,其能耗问题日益突出。数字电路正变得越来越重要[1]。研究表明,功耗会随着电源电压缩放而直接降低,且在亚阈值区域(电源电压—VDD低于晶体管阈值电压—VT)下运行数字电路被认为是实现超低功耗(ULP)消耗并保持可接受性能的最有效解决方案。MOS晶体管的亚阈值电流由公式(1)给出。

$$

I_{sub} = I_0 e^{(V_{GS} - V_T)/nV_{th}} \quad (1)

$$

and

$$

I_0 = \mu_0 C_{ox} \frac{W}{L} (n - 1)V_{th}^2 \quad (2)

$$

其中

- $V_T$:阈值电压

- $V_{th}$:热电压 (KT/q)

- $V_{GS}$:栅源电压

- $n$:亚阈值斜率因子 $(1 + C_{dep}/C_{ox})$

- $W$:有效沟道宽度

- $L$:沟道长度

- $\mu_0$:零偏载流子迁移率

- $C_{dep}$:耗尽层电容

- $C_{ox}$:氧化层电容

算术运算在许多VLSI应用中起着关键作用。加法、减法、乘法和累加是最常用的算术运算,其中1位全加器是所有这些实现的基本单元。因此,提升1位全加器单元的性能对于增强整体系统性能至关重要。

本研究提出了一种新的混合全加器电路,旨在亚阈值区域工作,以实现高效的能量运算应用。本章其余部分组织如下:第2节介绍所提出的全加器电路的设计方法;第3节展示仿真结果及对比讨论;最后,第4节给出一些结论。

2 提出的混合设计

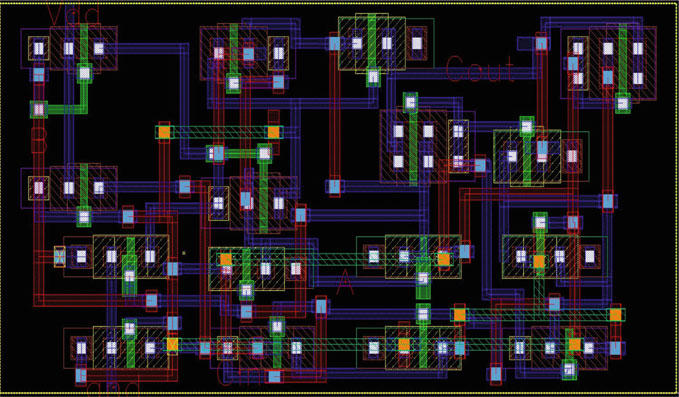

所提出的混合全加器电路采用静态CMOS逻辑[3]和传输门(TG)逻辑[4]结合动态阈值(DTMOS)方案[5]设计,如图1所示。该设计结构类似于文献[6]中提出的混合全加器(Hybrid-FA)。它由两个相同的XNOR逻辑门和传输门组成,分别用于生成和输出与进位输出(Cout)。

由于求和模块是功耗的主要来源,XNOR门电路采用电平恢复晶体管(M5和M6)来确保完全输出摆幅,并使用最少的晶体管数量以降低电路功耗。利用传输门生成Cout可确保完整的逻辑摆幅。由于进位输入(Cin)仅通过单个传输门(M15和M16)传播,因此传播延迟得以降低。

为了进一步提高混合加法器设计在亚阈值区域工作的能量效率,采用了DTMOS方案(将晶体管体端连接到栅极输入)。DTMOS方案是一种超低电压、面积高效的体偏置方案,其中器件的阈值电压(VT)随栅极电压的变化而动态变化。描述体偏置对阈值电压影响的基本方程为[7]

$$

V_T = V_{T0} + \gamma \left( \sqrt{2\phi_B - V_{SB}} - \sqrt{2\phi_B} \right) \quad (3)

$$

参数 $\gamma$ 是体效应系数,$\phi_B$ 是平带电压,$V_{SB}$ 是源极到体偏置电压,$V_{T0}$ 是零衬底/体偏置时的阈值电压。由公式(3)可知,采用DTMOS方案时,漏电流将减少(当 $V_G = V_B = 0$;$V_T$ 较高时),速度将提升(当 $V_G = V_B = 1$;$V_T$ 较低时)。

3 结果与比较讨论

对所提出的混合全加器电路进行了仿真,并将其结果与传统CMOS(C-CMOS)和动态阈值CMOS(DT-CMOS)全加器设计进行了比较。所有仿真均采用 Cadence 90 nm工艺技术进行,电源电压为200毫伏,工作频率为20千赫兹。

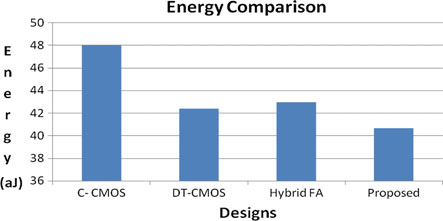

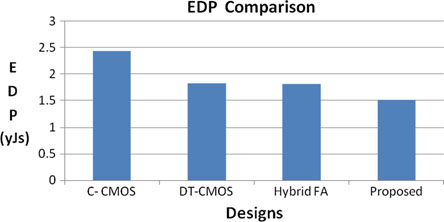

仿真得到的性能指标——功耗、延迟、能量和能效积(EDP)——如表1所示。通过比较可以明显看出,所提出的设计比其他设计消耗更少的能量和能效积。

所提出设计的布局如图2所示。该设计的面积为 28.7 μm²,与 C-CMOS (30.8 μm²) 和 DT-CMOS (34.6 μm²) 相比极低,仅比混合全加器(Hybrid FA)(25.84 μm²) 大 11%[6]。

表1 不同全加器电路的性能指标比较

| 设计 | 平均功耗(pW) | 延迟 (ns) | 能量 (aJ) | 能效积(EDP)(yJs) |

|---|---|---|---|---|

| C-CMOS | 943.4 | 50.9 | 48.019 | 2.44 |

| DT-CMOS | 1023.4 | 43.22 | 42.379 | 1.827 |

| 混合全加器(Hybrid FA) | 1018.2 | 42.23 | 42.99 | 1.811 |

| 本文提出的 | 1094.3 | 37.175 | 40.683 | 1.512 |

不同全加器的PDP和能效积(EDP)对比曲线分别如图3和图4所示。可以看出,所提出的电路在PDP和能效积(EDP)方面实现了显著节省,相比混合全加器(Hybrid FA)分别节省了5%以上和16%以上,相比DT-CMOS分别节省了4%和16%,相比C-CMOS分别节省了15%和38%。这些节省得益于所提出电路中较短的进位传播路径以及采用了DTMOS方案,从而降低了整体传播延迟。

4 结论

本章设计了一种新的混合全加器电路,该电路采用CMOS逻辑和传输门(TG)逻辑,并结合动态阈值MOS(DTMOS)技术,工作在亚阈值区域以实现最小能量消耗。电路仿真采用Cadence 90 nm工艺技术,电源电压为0.2伏特。仿真结果表明,与C-CMOS、DT-CMOS和混合-FA等其他设计相比,所提出的电路在仅占用28.7 μm²面积的情况下,实现了超过15%的延迟节省、4%的能量节省以及16%的能效积(EDP)节省。

因此,所提出的全加器电路可作为许多为面积和能量高效的算术应用而设计的亚阈值加法器的替代方案之一。

828

828

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?