目录

一、实验一

1、实验要求

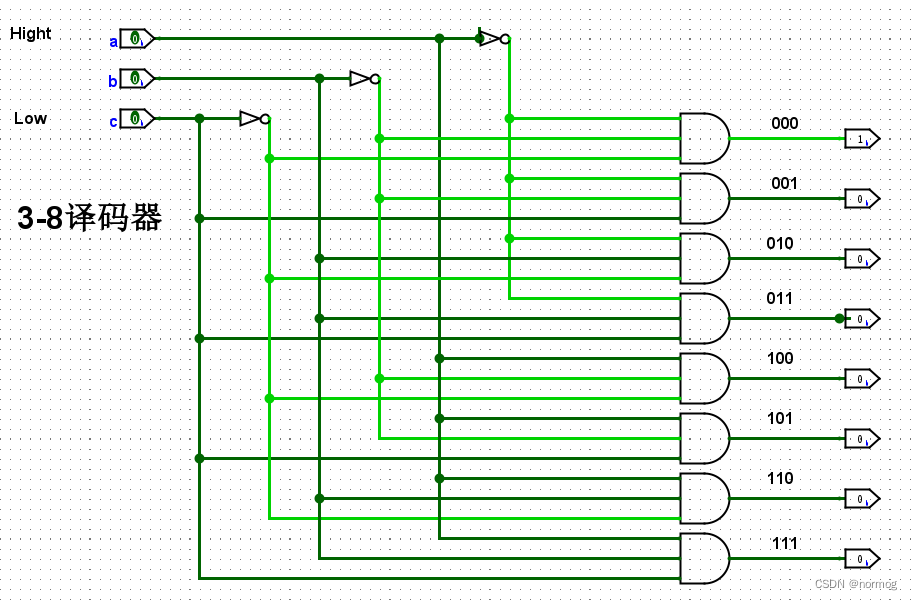

安装配置Quartus和ModelSim软件后,首先使用Logsim绘制一个3-8译码器电路图,列出3-8译码器的逻辑真值表。

然后采用Verilog编程(if-else或者case)设计一个3-8译码器,生成RTL原理电路图;

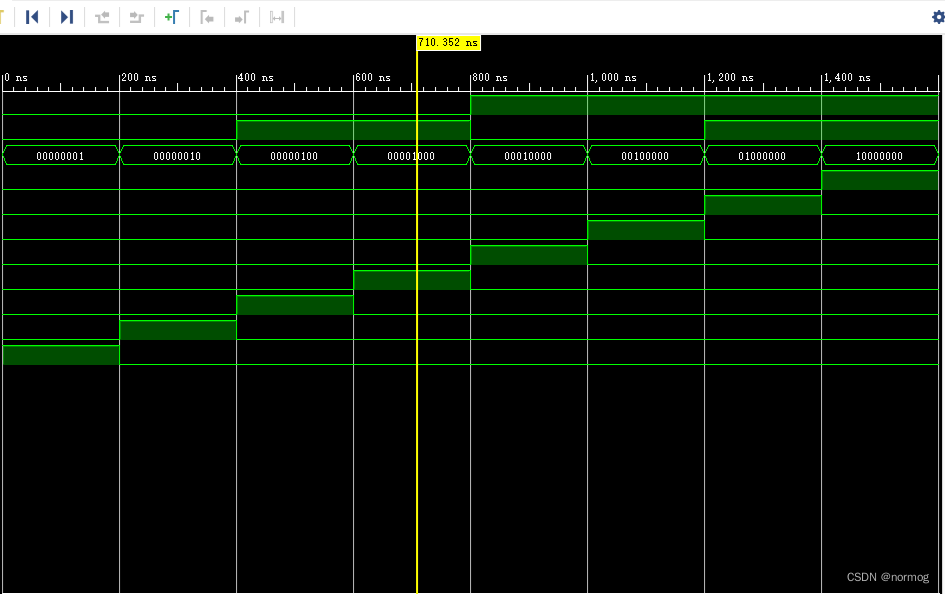

编写一个仿真测试文件,对3-8译码器进行仿真测试,输出测试波形图和Transcript结果。

2、实验

Logsim绘制一个3-8译码器电路图

3-8译码器的逻辑真值表

| A | B | C | Out |

|---|---|---|---|

| 0 | 0 | 0 | 10000000 |

| 0 | 0 | 1 | 01000000 |

| 0 | 1 | 0 | 00100000 |

| 0 | 1 | 1 | 00010000 |

| 1 | 0 | 0 | 00001000 |

| 1 | 0 | 1 | 00000100 |

| 1 | 1 | 0 | 00000010 |

| 1 | 1 | 1 | 00000001 |

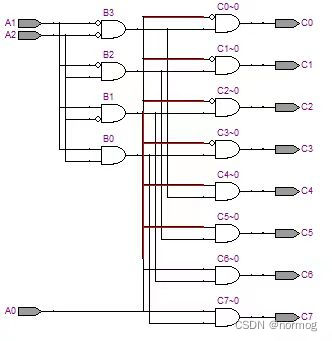

Verilog编程设计一个3-8译码器

代码

module if_38 (in_data,out_data);

input wire [2:0] in_data;

output reg [7:0] out_data;

always @(*)

begin

if (in_data==3'b000) out_data<=8'b1111_1110;

else if (in_data==3'b001) out_data<=8'b1111_1101;

else if (in_data==3'b010) out_data<=8'b1111_1011;

else if (in_data==3'b011) out_data<=8'b1111_0111;

else if (in_data==3'b100) out_data<=8'b1110_1111;

else if (in_data==3'b101) out_data<=8'b1101_1111;

else if (in_data==3'b110) out_data<=8'b1011_1111;

else out_data<=8'b0111_1111;

end

endmodule

RTL原理电路图

#### 波形图

#### 波形图

3、问题讨论

1)Verilog 综合生成的3-8译码器电路原理图与原始设计电路存在什么差异? 仿真测试生成的结果是否与真值表一致?

差异为:比例和布局,生成的电路可能使用不同的逻辑门实现方式,或者使用其他组合逻辑元件;时钟和时序,可能导致原始设计中的某些特定时序特征在综合后的电路中丧失或改变;

当进行仿真测试时,可以通过比较仿真结果与真值表来判断其一致性。通常情况下,如果综合工具正确地处理了设计并保持等效性,那么仿真测试生成的结果应该与真值表一致。但是,需要注意的是,在仿真中可能会考虑到一些因素(如时钟延迟和电路噪声),从而导致微小的差异。这些差异通常是合理的,并不一定是综合过程中引起的问题

2) Verilog代码设计的3-8译码器模块的输出信号 为何要定义为 reg类型而不用默认wire(导线)类型?改成wire型是否可以? (即是否可以把 output reg [7:0] out 改为 output [7:0] out) 修改后会出现什么错误?为什么会出错?

reg 关键字通常用于表示需要存储数据的信号。它可以用于描述状态变量、寄存器和存储器等。reg 类型的信号在被赋值后会保持其值,直到新的赋值操作为止。因此,在使用 reg 类型时,我们可以随时读取该信号,并且根据需要对其进行更新或修改。

相反,wire 关键字通常用于连接不同模块之间的信号,它们代表了一种无存储能力的连续传输信号。wire 类型的信号只能通过连接和连线(如 assign 语句)来设置其值,不能直接通过赋值语句进行设置。

二、实验二

1、实验要求

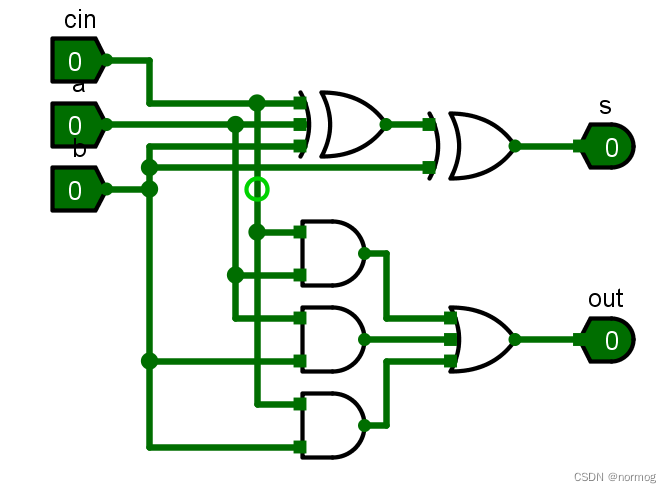

在logsim中完成的 “1位全加器”和“4位全加器”逻辑门电路

1)然后用Verilog的门级描述方式写一个“1位全加器”, 生成RTL电路,与Logsim的“1位全加器”进行对比。

2)采用Verilog模块调用子模块的方式,用4个上面的“1位全加器”级联方式,构成一个“4位全加器”(即串行全加器),生成RTL电路,与Logsim的“4位全加器”电路进行对比;

3)采用Verilog的行为级方式重新完成上面的1)和2)。

4)采用Verilog设计一个8位全加器模块。

2、实验

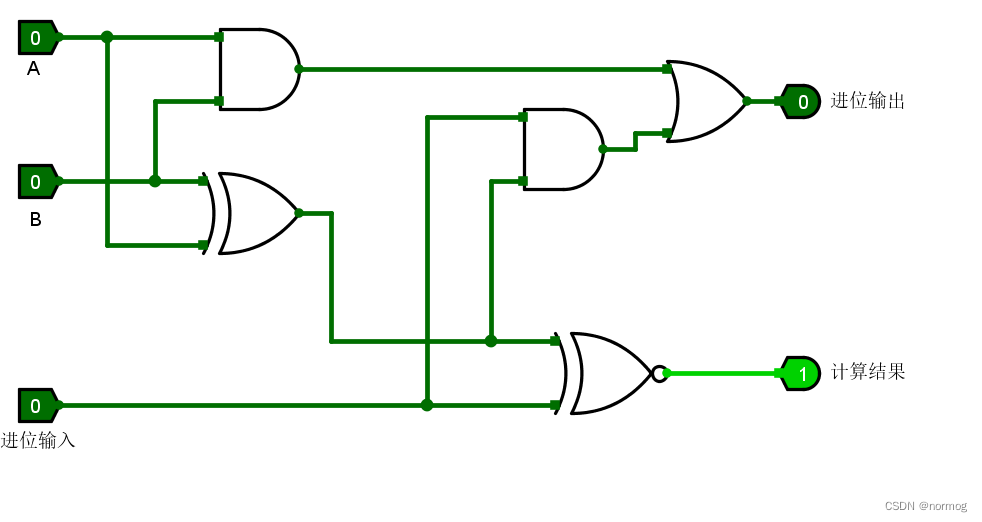

logsim中1位全加器

logsim中4位全加器

Verilog中采用门级描述方式1位全加器

代码

module add_1_m (a,b,cin,cout,sum);

input a,b;

input cin;

output cout;

output sum;

wire [2:0] w;

and

a1(w[0],a,cin),

a2(w[1],a,b),

a3(w[2],b,cin);

xor a4(sum,a,b,cin);

or a5(cout,w[0],w[1],w[2]);

endmodule

Verilog中调用子模块的方式4位全加器

//use add_1_m connect to add_4

module add_4_m (a,b,cin,cout,sum);

input [3:0] a,b;

input cin;

output cout;

output [3:0] sum;

wire [3:1] c;

add_1_m u1 (a[0],b[0],cin,c[1],sum[0]);

add_1_m u2 (a[1],b[1],c[1],c[2],sum[1]);

add_1_m u3 (a[2],b[2],c[2],c[3],sum[2]);

add_1_m u4 (a[3],b[3],c[3],cout,sum[3]);

endmodule

Verilog中8位全加器

module add(a,b,cin,cout,dout);

input [7:0] a,b;

input cin;

output {7:0};

output cout;

assign {cout,dout}=a+b+cin;

endmodule

本文介绍了使用Verilog语言设计3-8译码器和全加器的实验过程,包括电路图绘制、逻辑真值表、Verilog编程实现以及问题讨论。实验涉及从基础的逻辑门电路到多级全加器的设计和仿真验证。

本文介绍了使用Verilog语言设计3-8译码器和全加器的实验过程,包括电路图绘制、逻辑真值表、Verilog编程实现以及问题讨论。实验涉及从基础的逻辑门电路到多级全加器的设计和仿真验证。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?