前言

ARM 是单片机从业者,绕不开的一门技能,是从业向更深层次进阶的平台。本文章介绍ARM的构成、分布、调用,认真阅读后对此有清晰的认识,扫盲ARM概念。

一、ARM内核与架构

1.1 ARM芯片组成

arm 体系中,一般讲到的芯片由两大部分组成:arm的内核、外设

-

arm内核:

其内核主要由:寄存器、指令集、总线、存储器映射规则、中断逻辑主调试组件 构成。ARM公司只设计内核,授权给芯片厂商使用生产芯片,所以ARM只设计不生产。

-

外设:

包括计时器、A/D转换器、存储器、I2C、UART、SPI、ROM等。外设由芯片厂商自行设计并与ARM内核衔接配套。不同芯片厂商设计的外设不同,因此构成了数量和规则庞大的ARM芯片。

1.2 ARM指令集与架构

-

ARM指令集介绍

指令集的设计是处理器结构中最重要的部分,Instruction Set Architecture 简称 ISA

指令集是用来操作cpu的。

假如:一个32位的cpu,指令集就是一个32位的0、1的序列,不同的排序代表不同的指令,cpu 来解析、执行这些指令。比如:寻址、运算、异常处理。

-

ARM处理器架构

ARM公司2004年推出ARMv7内核架构(ARM11之前的处理器称经典处理器 使用ARM+数字方式命名)之后,使用以Cortex命名方式。分为3个系列:Cortex-A、Cortex-R、Cortex-M

Cortex-A系列(A:Application 应用)

面向性能要求高的系统应用:支持高计算要求、运行丰富操作系统、交互媒体和图形体验场景如:智能手机、平板电脑、汽车娱乐系统、数字电视、智能本、电子阅读器 等信息化产品

Cortex-R系列(R:Real-time实时)

面向实时应用的高性能内核,针对实时操作系统。汽车制动系统、大容量存储控制器 等嵌入式应用。

Cortex-M系统(M:MCU &FPGA)

面向各类嵌入式应用的微控制器内核

Cortex-SC系列(SC:SecurCore)

三大系列之外,另一个主打安全的Cortex-SC 应用于政府安全芯片。

总结:Cortex-A 系列是用于移动领域的CPU,Cortex-R和Corext-M系列是用于实时控制领域的MCU。Cortex-M比ARM7的架构高了3代,性能也有较大的提升,分为M0、M3、M4 和超低耗的M0+。

-

拓展

ARM公司只设计处理器架构,并不生产CPU。

STM32就是属于ARM公司授权Cortex-M内核给ST公司的一款处理器

Atmel(爱特梅尔)、ST、NXP(恩智浦)、TI(德州仪器)、IMB 持有ARM的授权

二、ARM处理器与寄存器

2.1ARM处理器模式

ARM 处理器共有7种运行模式,分为用户(usr)、快速中断(fiq)、外部中断、特权(svc)、中止、未定义指令中止(und)、系统模式(sys)

普通模式:

1、用户模式(usr、User Mode)正常的程序执行状态

2、特权模式:

快速中断模式(flq、FastInterrupt Mode)用于高速数据传输或通道处理。当触发快速中断时进入此模式。

外部中断模式(irq、Interrupt Mode)用于通用的中断处理,当触发外部中断时进入此模式。特权模式(svc、Supervisor Mode)操作系统使用此模式,在系统使用的保护模式,在系统复位或中断指令SW时进入。

中止模式(abt、Abort Mode)当数据或指令预取中止进进入该模式,可用于虚拟存储及存储保护。

未定义指令中止模式(und、Undefined Mode)当未定义的指令进入该模式,可用于支持硬件协处理器的仿真。

3、系统模式(sys、System Mode):运行具有特权的操作系统任务。

在特权模式下程序可以访问 所有的系统资源。非特权模式和特权模式之间的区别在于有些操作只能在特权模式下才能被允许,直接改为模式和中断使能等。用户模式如果需要访问硬件,必须切换到特权模式下,才允许访问硬件。

2.2ARM寄存器

-

ARM共有37个寄存器,32位的长度

1)31个通用寄存器,包括程序计数器在内

2)6个状态寄存器,1个当前状态寄存器,5个备份状态寄存器

-

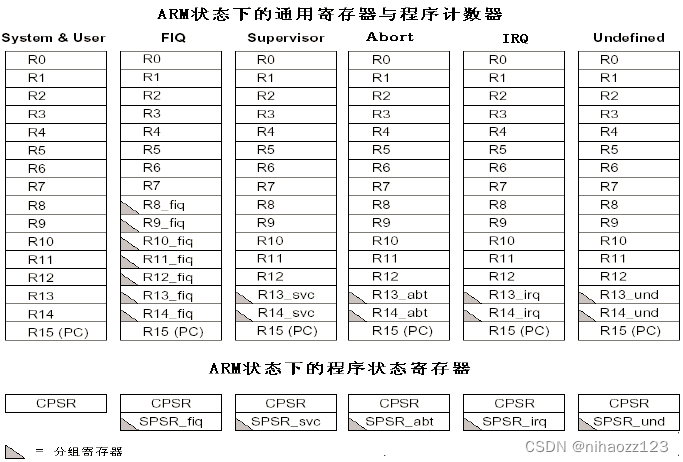

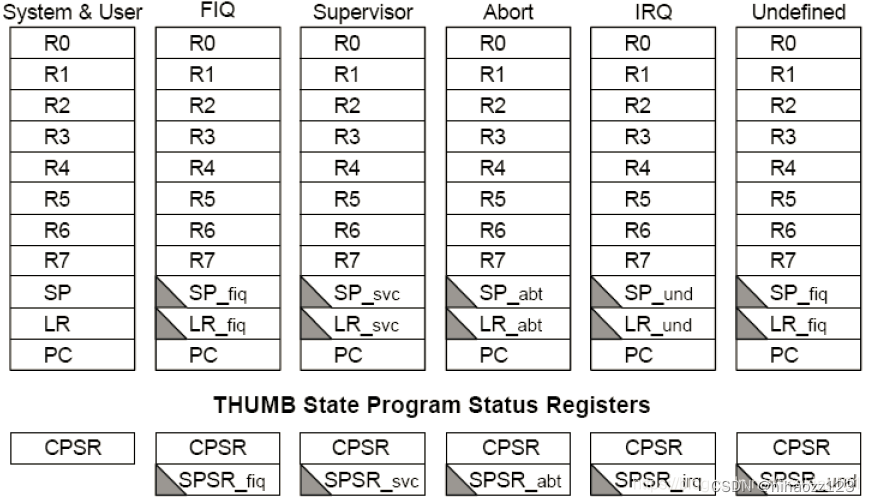

ARM各工作模式下的寄存器

Thumb状态下的寄存器

1、未分组寄存器R0~R7,共8个。在所有的运行模式下都使用同一个物理寄存器,它们未被系统用作特殊的用途。

2、分组寄存器R8~R12,R13~R14

1)R8~R12(总共10个)

每次访问的物理寄存器与处理当前的运行模式有关,

R8~R12:每个寄存器对应两个不同的物理寄存器当使用fiq模式时,访问寄存器R8_fiq~R12_fiq,当使用fiq模式以外的其它模式时,访问寄存器R8_usr~R12_usr。其中FIQ模式有单独一组R8~R12,共5个;

FIQ(快速中断模式)时访问寄存器R8_fiq~R12_fiq,另外6种模式一共R8~R12,共5个;(当使用除FIQ模式以外其他模式时,访问寄存器R8~R12)。

2)R13~R14(总共12个)

其中USR和SYS模式 共用一组R13~R14共2个,

另外5种模式下各有独自的一组R13~R14,并采用以下记号来区分不同的物理地址,分别为fiq、irq、svc、abt、und。共10个。(mode为以下几种之一:usr、fiq、irq、svc、abt、und)

1)R13在ARM指令常用作堆栈指针SP。由于每一种模式都有自己的R13,所以我们在自己初始化的时候一般要初始化每种模式下的R13,使其指向该运行模式下的栈空间。

2)R14称为子程序连接寄存器LR(Link Register),即在调用子程序的时候,可以将当前程序地址存入LR寄存器,这样就方便了函数的返回。它有两个特殊功能,一种是每一种模式下都 可以保存函数的返回地址,通常LR会配合BL和BLX来使用;另外就是异常处理后的返回地址,如中断

3、PC指针(R15)

R15用作程序计数器(PC),对应一个物理地址,由于ARM体系结构采用了多级流水线功能,对于ARM指令集而言,PC总是指向当前指令的下两条指令的地址,可以通过向PC赋值,来控制程序跳转,即PC的值 为当前指令的地址值加8个字节。

4、SPSR(5个备份状态寄存器)

SPSR(备份的程序寄存器或者叫影子寄存器)

SPSR除usr、sys外,对应用于异常保护的CPSR的备份,异常时,保存CPSR,异常退出时,将该值恢复到CPSR,以保证程序的正常运行,每一种异常运行模式(除usr和sys)有种自的物理寄存器。

1192

1192

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?