基于多参数非对称FinFET的超低泄漏与高性能逻辑电路设计

苏林德拉·M·乔杜里和尼拉杰·K·贾,普林斯顿大学

近年来,多栅场效应晶体管已经开始取代传统的平面MOSFET,以跟上深亚微米技术中摩尔定律的发展步伐。在不同类型的多栅晶体管中,由于制造成本低、卓越性能、更低的漏电以及设计灵活性,FinFET已成为半导体行业的首选。FinFET的背栅和前栅可以短接或保持独立,从而形成两种工作模式:短接栅(SG)和独立栅(IG)。

对于给定的工作模式,FinFET的物理参数可以是对称的或非对称的。本文首次分析了多参数非对称的SG-FinFET,并展示了其在同时实现超低泄漏和高性能逻辑门与电路方面的潜力。本研究局限于SG器件,因为IG-FinFET(无论是对称还是非对称)存在严重的导通电流退化问题,使其不适合用于高性能设计。我们首先全面比较了所有可行的单参数和多参数对称/非对称SG-FinFET。在所有这些FinFET中,传统SG(本质上为对称)、非对称功函数短接栅(AWSG)和非对称功函数凹陷短接栅(AWUSG)FinFET表现出最大的应用前景。我们对这些器件在栅长(LG)、鳍片厚度(TSI)、栅氧化层厚度(TOX)、栅极未对准(LUN)以及栅极功函数(ϕG)的工艺变异下,以及电源电压(VDD)变化下的特性进行了表征,并进一步开展了在不同温度下的门级漏电/延迟分析。尽管AWSG-FinFET的漏电功耗非常低,但其性能相对于SG-FinFET有所退化。类似地,我们的研究表明,其他任何单参数非对称FinFET都无法提供良好的低功耗与高性能设计组合。我们发现,基于AWUSG-FinFET的逻辑门/电路比基于传统SG-FinFET的逻辑门/电路速度更快,且漏电功耗和面积更小。在满足相同延迟约束的前提下,在温度T= 348K下观察到总功耗最大(平均)降低了53.4%(30.2%),AWUSG电路的面积相比SG电路减少了14.2%(13.5%)。在T= 373K时,总功耗最大(平均)降低达到68.6%(46.9%)。

1. 引言

鳍式场效应晶体管最近已被大多数领先的半导体公司在22纳米技术节点及更先进节点上采用,成为多栅晶体管替代方案中最可行的选择[Nowak et al. 2004]。在深亚微米技术节点上,鳍式场效应晶体管因其对沟道的更强控制能力而备受青睐,从而实现低漏电、卓越性能、由于与原有制造工艺的无缝过渡所带来的低成本,以及设计灵活性。鳍式场效应晶体管还提供多种具有独特特性的器件选择,为新型电路设计开辟了新的研究机会。

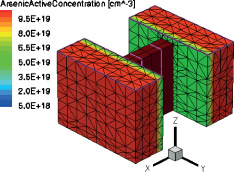

体硅和绝缘体上硅(SOI)鳍式场效应晶体管均被使用。在本研究中,我们聚焦于SOI鳍式场效应晶体管(图1)。此类FinFET具有包裹在位于绝缘基底上的薄硅鳍周围的金属栅极。当顶部使用厚间隔材料时,其作用类似于由前栅和背栅共同控制的双栅器件。当未使用顶部间隔层时,器件也可从顶部进行控制,从而成为三栅器件(英特尔所采用的结构)。由于FinFET的沟道要么未掺杂,要么轻度掺杂,因此在体硅CMOS中备受关注的随机掺杂涨落效应得以缓解。

在单栅鳍式场效应晶体管中,前栅和背栅在顶部相连(如图1所示),而在独立栅鳍式场效应晶体管中,顶部部分被蚀刻掉,从而形成独立的前栅和后栅。单栅鳍式场效应晶体管具有更高的导通电流(ION),而独立栅鳍式场效应晶体管的关断电流(IOFF)则低得多,但其导通电流性能非常差(ION)。独立栅鳍式场效应晶体管的背栅可以通过施加正(反)向偏置来动态改变其导通电流与关断电流之比(ION/IOFF)。然而,其导通电流(ION)仍远低于单栅鳍式场效应晶体管的导通电流(ION)。

鳍式场效应晶体管(FinFET)还可以根据其单栅或独立栅工作模式分为对称或非对称类型。在同一FinFET中可能取不同值的一些参数包括LUN, ϕG,和源/漏掺杂(NSD)。这些器件被称为非对称器件。在对称FinFET中,这些参数具有相同的值。我们可以进一步将非对称FinFET分为单参数非对称或多参数非对称。在单参数非对称器件中,只有一个参数取不同值,而在多参数非对称器件中,多个参数取不同数值。迄今为止,研究人员主要探索了仅有一个参数为非对称的FinFET,例如AWSG、非对称掺杂单栅(ADSG)和非对称覆盖不足单栅(AUSG)。基于AWSG FinFET的逻辑门相对于对称单栅器件在漏电‐延迟谱上表现更优,在逻辑电路、触发器、锁存器和静态随机存取存储器的功耗/性能优化方面显示出良好的前景。然而,ADSG和AUSG FinFET仅在SRAM单元设计背景下被研究过。

鳍式场效应晶体管提供了多种选择,涵盖单栅/独立栅操作模式以及不对称的单参数和多参数器件。它们提供了截然不同的ION/IOFF组合。然而,除非需要动态调节阈值电压(Vth),或通过向独立的前栅和后栅输入不同信号来实现或操作,否则在导通电流ION以及由此决定的电路性能方面,任何涉及独立栅鳍式场效应晶体管的前述组合都将远逊于相应的单栅鳍式场效应晶体管组合。因此,本文仅对涉及单栅鳍式场效应晶体管的各种组合进行表征。对于半导体行业而言,寻找兼具高导通电流和极低漏电流的场效应晶体管至关重要。我们证明,前述某些组合能够实现这一可能性。

本文的主要贡献如下:

— 我们对所有可能的对称和非对称单栅鳍式场效应晶体管进行表征,并直接比较它们在ION/IOFF方面的相对性能。尽管一些单参数非对称器件已被研究在静态随机存取存储器的背景下,我们首次引入了多参数非对称鳍式场效应晶体管的概念及其重要性。

— 传统SG FinFET(本质上是对称的)虽然能够提供高的导通电流,但代价是漏电流较高。此外,AWSG FinFET的导通电流大约降低了30%,但在漏电流方面具有两个数量级的优势。理想istically,我们希望使用的晶体管在导通电流方面优于SG FinFET,同时在漏电流方面与AWSG FinFET相当。我们证明了AWUSG正是这样一种FinFET。

— 我们全面表征了SG、AWSG、AUSG和AWUSG FinFET(在各种FinFET参数组合中,这些FinFET表现突出)对LG、TSI、TOX、LUN、ϕG, VDD以及T等参数变化的敏感性。此外,我们还检验了这些器件在LG、TSI、TOX、LUN、ϕG,以及VDD工艺变异影响下的鲁棒性。随后,我们对由这些器件构成的逻辑门进行漏电‐延迟分析,以确定它们在不同温度下漏电‐延迟谱中的相对位置。

— 最后,我们将SG与AWUSG FinFET逻辑电路实现进行比较,以证明在相同延迟约束下,后者可实现显著的面积/功耗降低。

本文其余部分组织如下。在第2节中,我们回顾了相关工作。在第3节中,我们详细描述了不同类型的鳍式场效应晶体管,并对各种对称/非对称FinFET进行了表征。在第4节中,我们分析了由单参数和新型多参数非对称鳍式场效应晶体管构成的逻辑门。在第5节中,我们论证了AWUSG器件在优化电路功耗、面积和性能方面的潜力。最后,在第6节中,我们进行总结。

2. 相关工作

多栅晶体管的潜力早已被研究界和半导体行业所认可。任何新器件的引入通常都需要在制造、器件建模、仿真技术、电路设计和架构实现等领域引起重视[Bhattacharya 和 Jha 2014]。研究人员已经制造出多种类型的鳍式场效应晶体管,包括在单栅(SG)和独立栅(IG)模式下工作的器件。尽管迄今为止主要关注对称器件,但AWSG FinFET的潜力已在工业界通过制造[Kedzierski 等人 2001]以及研究人员的表征工作[Bhoj 和 Jha 2013]得到认可。此外,研究人员还制造并展示了非对称未掺杂单栅金属氧化物半导体场效应晶体管(AUSG MOSFETs)的卓越性能[加尼等人 2001;Horiuchi 等人 1994]。

由于鳍式场效应晶体管具有非平面结构,器件物理和建模技术的恰当应用至关重要。鳍式场效应晶体管的三维特性也使其器件仿真非常CPU密集型,因此在精度和效率之间取得平衡是当前的一个挑战。为解决这一问题,在Chaudhuri和Jha [2014a],中,我们提出了一种基于LUN调整的方法,该方法弥合了工艺变异下三维与二维器件仿真之间的精度差距,从而在几乎不损失精度的情况下显著提高了FinFET器件仿真的效率。

LG、TSI、TOX和ϕG被视为在工艺变异下确定器件行为的关键参数[Xiong 和 Bokor 2003;Mishra 等人 2010]。已开发出一种基于响应面的方法来建模FinFET逻辑门中的漏电/延迟[Chaudhuri 等人 2012]。Wang 等人[2013]研究了工艺引起变异与统计变异之间的相互作用,并进一步探讨了其对SRAM稳定性的影响[2014]。各类FinFET的潜力促使研究人员探索其在电路层面的影响,以获得功耗‐性能‐稳定性优势。因此,已在FinFET电路中探索了基于SG/IG操作模式的漏电‐延迟权衡[Chiang 等人 2005;Kumar 等人 2004;Tawfik 和 Kursun 2007;Mishra 等人 2009]。在 Mishra 等人[2009],、Ouyang 和 Xie[2008],、Swahn 和 Hassoun[2006],以及 Muttreja 等人[2007],的研究中,栅极尺寸调整和多电源/阈值电压方法已被证明在功耗优化方面是有效的。

Ananthan 和 Roy[2006], 、Choi 等人[2007],以及 Gu 等人[2008]探讨了温度对器件/门漏电流(ILEAK)的影响。为获得更好的漏电/性能特性,已有研究探索了多阈值FinFET的概念[Gaynor 和 Hassoun 2014],但存在某些限制。最近,与使用多阈值FinFET(在集成电路中不同晶体管使用不同的栅极功函数)的概念正交,AWSG FinFET(在同一FinFET中使用两种不同栅极功函数)被认定为一种超低漏电器件。它们能够实现极低功耗设计,但性能有所损失。Bhoj 和 Jha[2013]研究了基于AWSG FinFET的逻辑门、锁存器和触发器的漏电‐延迟谱。研究表明,在相同延迟约束下,与基于SG FinFET的电路相比,基于AWSG FinFET并在更高电源电压下运行的电路消耗更少的总功耗[Chaudhuri 和 Jha 2014b]。在 Bhoj 和 Jha[2014],的研究中,基于AWSG的SRAM存储单元在直流指标和动态写入能力方面表现出竞争力。Goel 等人[2011]和 Moradi 等人[2011]提出了ADSG和AUSG FinFET,并在鲁棒SRAM设计背景下进行了分析。Choi 等人[2003]研究了栅致漏极漏电(GIDL)对各种对称与非对称FinFET的影响。结果表明,在低于VDD< 1.1V下运行的数字电路中,该影响可以忽略不计。Woo 等人 [2002]研究了ADSG FinFET的电学特性。

在本研究中,我们首次提出多种多参数非对称鳍式场效应晶体管。我们进一步对这些新型器件与现有的FinFET器件选项进行了比较、分析和表征。在此表征过程中,AWUSG鳍式场效应晶体管从ION和IOFF的角度展现出最具吸引力的特性。随后,我们从面积/延迟/功耗的角度展示了AWUSG鳍式场效应晶体管在逻辑门和电路层面的优势。

3. 对称与非对称鳍式场效应晶体管

在本节中,我们研究了多种在单栅模式下工作的对称与非对称鳍式场效应晶体管,并对其进行直接比较,以探索它们在优化漏电流和性能方面的潜力。我们采用基于Python的集成仿真平台(Bhoj和Jha [2013]),该平台连接了Sentaurus TCAD 结构编辑器(SE)、器件模拟器、SVisual和MATLAB,以简化这些工具之间的数据流 [Synopsys 2011]。在我们的器件级表征中,通过三维器件仿真对典型的单栅n型鳍式场效应晶体管(如图2所示)进行仿真。在逻辑门级

| 参数(单位) | 值 |

|---|---|

| LGF,LGB(nm) | 20 |

| 温度OXF,温度OXB(纳米) | 1 |

| 温度 SI (nm) | 11 |

| HFIN(纳米) | 40 |

| HGF,HGB(nm) | 24 |

| LUN(纳米) | 10 |

| FP(纳米) | 60 |

| NBODY(cm −3) | 1015 |

| ϕG(eV) | nFET:4.4,pFET:4.8 |

| NSD(cm −3) | 1020 |

| VDD(V) | 0.9 |

采用混合模式分析,我们对三维n/p‐FinFET的二维截面(如图3所示)进行仿真,以显著提高仿真效率。该分析基于流体动力学器件仿真,考虑了禁带变窄模型、载流子迁移率的Philips统一模型,以及肖克利‐里德‐霍尔和带间隧穿模型,以准确捕捉载流子复合效应[Synopsys2011]。

表I显示了在22纳米技术节点下对称SG n/pFinFET的典型物理参数值,这些数值基于晶圆厂数据进行校准[Guillorn 等人,2008;Wu 等人,2010;Yamashita 等人 2011]。在我们之前的成果[Chaudhuri 和 Jha 2014a],中,我们展示了漏极电流IDS随栅极电压VGS变化的曲线,与文献中报道的数据一致。参考图3,工艺参数包括前(后)物理栅极长度LGF(LGB)、鳍片厚度(TSI)、前(后)栅氧化层厚度TOXF(TOXB)、前(后)栅极厚度HGF(HGB),以及LUN。WNEFF和WPEFF分别表示nFinFET和pFinFET的有效宽度,对于SG FinFET(无论是对称还是非对称),其定义为2nHFIN(其中n为FinFET中的鳍片数量,HFIN为鳍片高度)。这些有效宽度同时考虑了前表面和后表面的反型沟道。

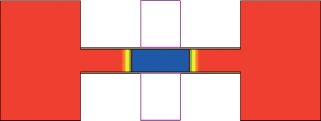

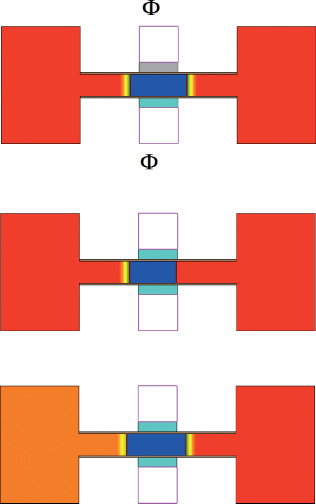

在各种物理参数中,ϕG, LUN和NSD可能在同一FinFET内取不同值,从而产生不同的非对称FinFET。因此,对于非对称FinFET,我们将这些参数称为前/后栅功函数(ϕGF/ϕGB)、源/漏栅未对准(LUNS/LUND)以及源/漏掺杂(NS/ND)。仅有一个物理参数为非对称的FinFET被归类为单参数非对称。此类器件的示例包括AWSG、AUSG和ADSG FinFET,如图4所示。另一方面,多个物理参数为非对称的FinFET被归类为多参数非对称。一些示例如下:非对称栅功函数/栅未对准SG(AWUSG)、非对称栅功函数/掺杂SG(AWDSG)、非对称栅未对准/掺杂SG(AUDSG)以及非对称栅功函数/栅未对准/掺杂SG(AWUDSG)FinFET,如图5所示。可以调节栅极材料的功函数,该功函数决定了器件的Vth。对于对称SG FinFET(即传统的FinFET),nFinFET(pFinFET)选择4.4电子伏特(4.8电子伏特)作为功函数,以实现高性能逻辑电路。在包含非对称功函数的FinFET中,前栅和背栅分别对应不同的功函数。表II显示了基于Bhoj和Jha [2013],、Goel等 [2011],、Moradi等 [2011],、Ghani等 [2001],、Horiuchi等 [1994],以及Woo等 [2002]所进行优化的这些非对称参数的典型取值。然而需要注意的是,非对称参数具体取值的选择与本研究关注的FinFET非对称性分析是正交的。正如我们将在后文看到的,非对称结构的优势在于

| 参数(单位) | 值 |

|---|---|

| ϕ GF(eV) | 4.4 |

| ϕ GB(eV) | 4.8 |

| LUNS(纳米) | 0 |

| LUND(纳米) | 10 |

| NS(cm − 3 ) | 1020 |

| ND(cm − 3 ) | 1019 |

即使参数值在一定范围内变化,非对称FinFET的特性仍得以保持。

AWSG FinFET 最初由 IBM 研究人员[Kedzierski 等人 2001]制造并研究。他们制造了对称和非对称器件以建立其制造工艺的相似性。对称器件的制造是在65纳米绝缘体上硅晶圆上进行的,顶部覆盖有50纳米氧化物硬掩模。使用光学光刻和硬掩模修整来定义鳍层。采用高倾斜角度注入包含多个晶圆扭曲的扩展区域。另一方面,非对称器件的制造是在120纳米晶圆以及90纳米氧化物硬掩模上完成的。鳍片的定义采用了与对称器件相同的方法。同样,也采用了类似的技术来注入扩展区域和多晶栅极。由于对称和非对称器件在制造工艺上存在显著相似性,因此如有需要,可实现向非对称FinFET的无缝过渡。研究人员还制造并研究了AUSG平面MOSFET [堀内等人 1994;Ghani 等人 2001]。这类非对称器件只需遵循传统平面CMOS制造步骤即可实现制造。

3.1. 单参数非对称FinFET

在本节中,我们首先根据器件物理原理分析传统的对称SG FinFET,以更好地理解其ION/IOFF特性。然后,研究多种单参数非对称FinFET——AWSG、AUSG和ADSG,以寻找一种相较于对称SG FinFET具有更高ION但显著降低IOFF的FinFET。我们采用优化收敛性的精细网格进行流体动力学混合模式三维器件仿真,以考虑温度效应。由于沟道未掺杂,并且因使用了相对较厚的高‐κ介质氧化层导致栅极漏电可忽略不计,因此忽略栅极隧穿效应。

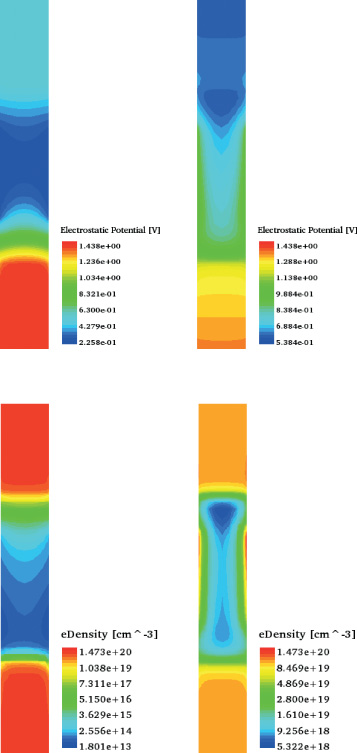

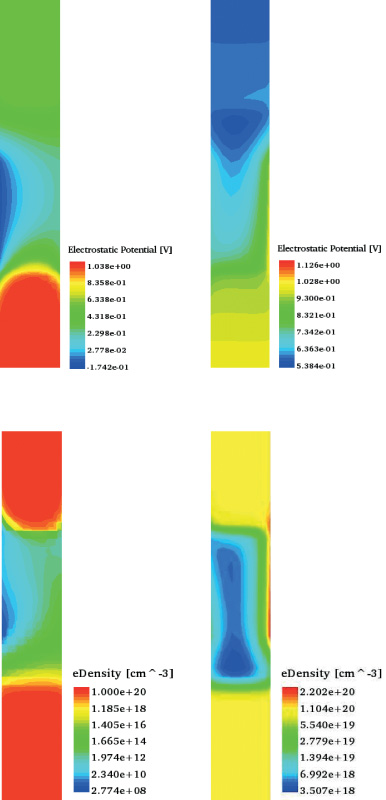

图6显示了单栅n型鳍式场效应晶体管(SG nFinFET)在关态(VDS= 0.9V,VGS= 0V)和开态(VDS= 0.9V,VGS= 0.9V)时鳍区内的静电势分布和电子密度。图6(b)清楚地显示出前栅和背栅附近严重的能带弯曲,这有助于形成明显的反型区,如图6(d)所示,从而产生较高的导通电流。相反,在图6(a)中,我们观察到两个栅极相邻区域存在较高的势垒,使得泄漏路径的空间非常有限。然而,势垒在靠近鳍中心处显著降低,导致出现显著的泄漏路径,并引起较高的关态漏电流。我们测得SG nFinFET(pFinFET)的导通电流为146.16μA(76.81μA),关态漏电流为1.83nA(0.11nA)。

在Bhoj和Jha [2013],中,AWSG FinFET以及逻辑门/锁存器/触发器被深入研究,展现出优异的亚阈值特性和超低泄漏。本文重新探讨了此类器件的特性及相关物理机制,以更深入理解其在实现极低IOFF和足够高ION方面所面临的局限性。AWSG FinFET通过在正面和背面采用选择性注入来调节栅极功函数而制造而成,因此其栅极两侧具有两个不同的功函数[Bhoj和Jha 2013]。为了降低制造成本,在AWSG n/pFinFET的两侧均使用相同的两个功函数。因此,在我们的实验中,假设AWSG n/pFinFET的栅极功函数分别为4.4电子伏特和4.8电子伏特,源/漏掺杂决定导通状态下的多数载流子。使用非对称功函数可实现非常陡峭的亚阈值斜率[Bhoj和Jha 2013],从而导致极低的IOFF,但代价是ION略有下降。图7显示了AWSG FinFET在关断和导通状态下鳍区的静电势和电子密度。从图7(b)可以看出,其能带弯曲情况与单栅鳍式场效应晶体管类似,但在靠近栅极处形成的反型层(如图7(d)所示)程度略轻,这导致ION性能有所下降。另一方面,由于在鳍区(甚至鳍中心)不存在显著的泄漏路径(如图7(c)所示),AWSG栅极表现出优异的关态特性。我们获得的ION降低了28.1%(34.7%),为105.12μA(50.16μA),IOFF降低了97.8%(97.3%),为0.04nA(0.003nA)

相对于SG nFinFET(pFinFET),AWSG nFinFET(pFinFET)的ION性能下降。因此,尽管AWSG FinFET非常适用于超低泄漏设计,但由于其性能退化,不太适合高性能设计。

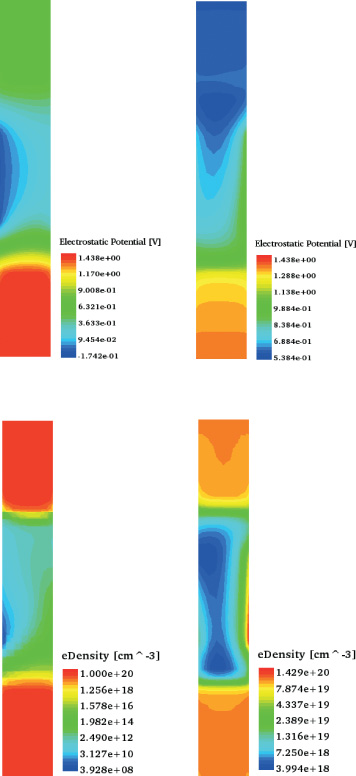

接下来,我们探讨在Goel等人[2011]和Moradi等人[2011]中提出的AUSG和ADSG FinFET。AUSG FinFET在一侧具有栅极重叠,另一侧为未对准。它们可以使用标准FinFET制造工艺步骤进行制造。然而,为了在漏极侧引入未对准,需要额外的非对称间隔层形成或倾斜离子注入步骤。非对称间隔层可以通过在源极侧加掩模的情况下,在漏极侧沉积间隔层材料来形成。此外,可以使用反应离子刻蚀[去除间隔层材料(Goel等 2011])。由于这种非对称性,对这些器件进行适当的偏置非常重要,从而导致n/p‐FinFET产生不同的工作配置。对于漏极侧未对准的nFinFET(pFinFET),保持VDS> 0(VDS< 0)可获得相对于单栅鳍式场效应晶体管更高的ION,同时IOFF[仅有轻微增加(Goel等)。

2011]。最近,Goud 等人对在 7纳米节点 使用此类鳍式场效应晶体管实现的静态随机存取存储器进行了深入研究 [Goud et al. 2015]。图8(b) 显示了显著的能带弯曲,这导致鳍区出现强反型,如 图 8(d) 所示。图8(a) 和 (c) 显示了关态下鳍区的静电势和电子密度,它们显示出在鳍中心存在显著的泄漏路径。因此,该器件不适合用于低功耗设计。与单栅nFinFET(pFinFET)相比,AUSG nFinFET(pFinFET)的导通电流高出 24.9%(49.0%),达到 182.55μA(114.43μA),关态漏电流高出 122.4%(127.3%),达到 4.07nA(0.25nA)。这一观察结果表明,如果能在不过分牺牲导通电流的前提下降低其关态漏电流,则该器件有望与单栅鳍式场效应晶体管相竞争。

在Moradi等人[2011],中提出了一种ADSG FinFET,该器件在两侧采用不对称掺杂。表II显示了此类FinFET常用的掺杂浓度值。对于具有较高掺杂的nFinFET(pFinFET),保持VDS > 0(VDS < 0)

关态和(b)O N-状态。电子 on密度在ADSG nFinFET鳍区的(c)关态和(d)开态)

关态和(b)O N-状态。电子 on密度在ADSG nFinFET鳍区的(c)关态和(d)开态)

位于源极侧可获得更好的结果,因此此处采用该方式。图9(d)显示,在开态下,相对于单栅鳍式场效应晶体管,鳍区中的反型较弱,因此ION显著更低。然而,关态电子密度与单栅鳍式场效应晶体管大致相同,这解释了两者相近的IOFF值。与单栅nFinFET(pFinFET)相比,ADSG nFinFET(pFinFET)的ION降低了37.1%(32.1%),分别为91.98μA(52.19μA),IOFF降低了26.8%(27.3%),分别为1.34nA(0.08nA)。由于ION显著降低,ADSG FinFET在高性能设计中竞争力较弱。此外,尽管ADSG FinFET在ION方面与AWSG FinFET具有可比性,但在IOFF方面则完全不具备竞争力。

在图10和图11中,我们比较了n型和p型单参数非对称FinFET与SG FinFET的IDS随VGS变化的特性。表III总结了所有这些FinFET的IOFF/ION结果( 1×后缀表示这些FinFET仅有一个鳍)。我们观察到,AUSG(AWSG)FinFET在IDS(IGS)方面优于SG

| 类型 | IOFF(纳安) | %变化 | ION(μA) | %变化 |

|---|---|---|---|---|

| n型鳍式场效应晶体管1× |

SG

AWSG AUSG ADSG |

1.83

0.04 4.07 1.34 |

-

−97.8 122.4 −26.8 |

146.16

105.12 182.55 91.98 |

| pFinFET1× |

SG

AWSG AUSG ADSG |

0.11

0.003 0.25 0.08 |

-

−97.3 127.3 −27.3 |

76.81

50.16 114.43 52.19 |

| FinFET。ION(IOFF)因此,如果我们能够将AUSG FinFET的ION优势与AWSG FinFET的IOFF优势结合起来,就可以在采用新型FinFET构建的电路中同时实现高性能和低功耗。这促使我们探索多参数非对称FinFET。 |

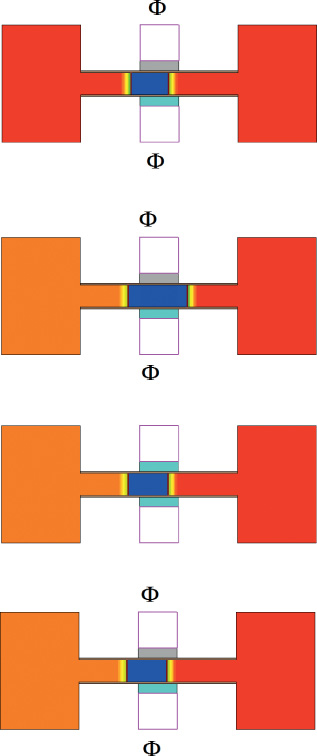

3.2. 多参数非对称鳍式场效应晶体管

到目前为止,我们已经考虑了LUN, ϕG,和NSD中的非对称性。如果我们将这些非对称性组合在一个FinFET中,就会形成多参数非对称鳍式场效应晶体管(例如AWDSG、AWUSG、AUDSG和AWUDSG)。在表IV中,我们报告了所有此类n/pFinFETs的IOFF /ION结果,并将其与单栅鳍式场效应晶体管进行比较。在图12和图13中,我们比较了所有这些FinFETs的IDS随VGS变化的特性。我们观察到AWUSG、AWDSG和AWUDSG n/pFinFETs的IOFF非常低。然而,只有AWUSG FinFETs

| 类型 | IOFF(纳安) | %变化 | ION(μA) | %变化 |

|---|---|---|---|---|

| n型鳍式场效应晶体管1× |

SG

AWDSG AWUSG AUDSG AWUDSG |

1.83

0.03 0.11 3.44 0.07 |

-

−98.4 −94.0 88.0 −96.2 |

146.16

77.88 144.76 99.62 89.79 |

| pFinFET1× |

SG

AWDSG AWUSG AUDSG AWUDSG |

0.11

0.001 0.01 0.22 0.004 |

-

−99.1 −90.9 100.00 −96.4 |

76.81

40.62 85.72 60.82 52.20 |

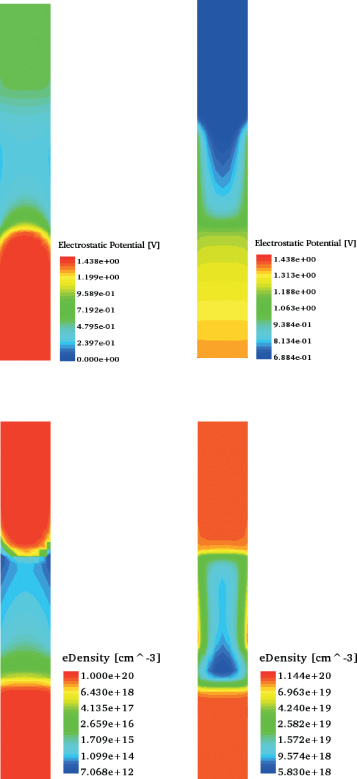

与单栅鳍式场效应晶体管相比具有竞争力的ION。AWUSG nFinFET(pFinFET)的ION与单栅nFinFET(pFinFET)相近(高出11.6%),但IOFF却低了94.0%(90.9%)。因此,这表明该鳍式场效应晶体管可同时实现高性能和超低漏电功耗(从而实现整体低功耗)。这一观察结果也可以通过理解AWSG和AUSG FinFET的定性特性来解释。我们此前讨论过,栅极功函数的不平衡如何导致AWSG FinFET中的IOFF非常低。同样,我们也看到AUSG FinFET中不相等的未对准如何有效增加沟道区域在导通时的载流子供应

关态和(b) 开态。AWUSG nFinFET鳍区内的电子密度:(c) 关态和(d) 开态)

开态,这意味着非常高的ION。因此,当我们将这两个特性结合到AWUSG鳍式场效应晶体管中时,便能兼得两者的优势。我们在图14中展示了AWUSG nFinFET在鳍区的静电势和电子密度分布。图14(b)显示了在开态下存在强烈的能带弯曲,与单栅n型鳍式场效应晶体管类似,这导致栅极附近出现强反型,如图14(d)所示。这解释了此类器件的ION具有竞争力的原因。与单栅鳍式场效应晶体管相比。此外,图14(c)显示在关态下没有显著的泄漏路径。其电子密度分布与AWSG FinFET相似。因此,AWUSG鳍式场效应晶体管结合了单栅鳍式场效应晶体管更高导通电流和AWSG FinFET更低关态电流的优点。

| 类型 | Vthn(V) | Vthp(V) | SSn(mV/每十倍频) | SSp(mV/每十倍频) |

|---|---|---|---|---|

| SG | 0.27 | −0.34 | 68 | 69 |

| AWSG | 0.42 | −0.52 | 69 | 70 |

| AUSG | 0.27 | −0.34 | 71 | 72 |

| ADSG | 0.27 | −0.32 | 68 | 66 |

| AWUSG | 0.34 | −0.42 | 66 | 68 |

| AWDSG | 0.39 | −0.42 | 63 | 64 |

| AUDSG | 0.26 | −0.31 | 70 | 68 |

| AWUDSG | 0.33 | −0.40 | 61 | 63 |

在表五中,我们列出了所有单/多参数非对称FinFET以及单栅鳍式场效应晶体管的Vth和亚阈值斜率(SS)。所有鳍式场效应晶体管均具有良好的亚阈值特性。然而,n/p型AWSG和AWUSG鳍式场效应晶体管的Vth值相对较高,这解释了它们非常低的IOFF值。我们通过回归分析获得这些器件的SS。在亚阈值区每隔10mV探测一次特性曲线,然后进行线性拟合。该线性拟合的斜率即为器件的SS。

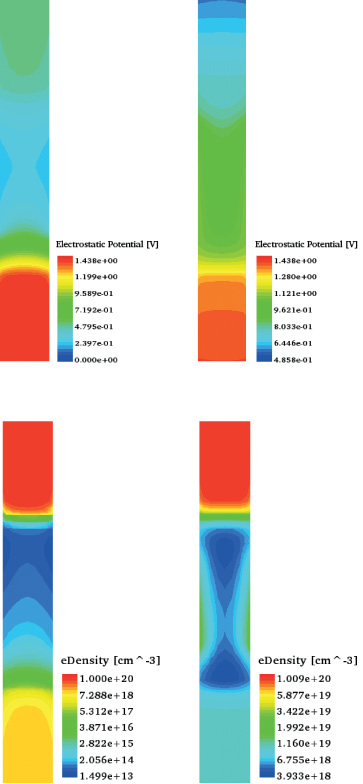

3.3. 对各种参数变化的敏感性

在上一节中,我们识别了介绍了几种优势器件:AWSG(最佳IOFF)、AUSG(最佳ION)和AWUSG(兼顾两者优点)。在本节中,我们研究这些n型鳍式场效应晶体管相对于各种参数变化的IOFF/ION敏感性:LG、TSI、TOX、LUN、ϕG,和VDD(pFinFET表现出类似的敏感性)。为了比较,我们也包含了单栅n型鳍式场效应晶体管。图15显示了IOFF对LG、TSI、TOX、LUN、ϕG,和VDD变化的敏感性。我们观察到,随着LG、LUN和ϕG的增加,IOFF显著下降;随着TSI的增加,IOFF显著上升;而对TOX和VOX的变化相对不敏感。此外,显然IOFF对ϕG和TSI的变化最为敏感。在图15(e)中,x轴表示不同类型的晶体管对应的ϕG值集合。对于单栅鳍式场效应晶体管,x轴上的数值1至5分别表示4.38 eV、4.39 eV、4.40 eV、4.41 eV和4.42 eV;而对于其他非对称FinFET,它们表示一对ϕG值:4.38/4.78 eV、4.39/4.79 eV、4.40/4.80 eV、4.41/4.81 eV和4.42/4.82 eV。我们假设前栅和背栅功函数基于相同的工艺流程,因此它们在同一方向上变化。

在图16中,我们展示了ION相对于各个参数变化的灵敏度。可以看出,ION随LG和LUN的增加而线性减小,但随TSI和VDD的增加大致呈线性增加。ION对TOX和ϕG的变化不敏感。我们还观察到,在IOFF变化的情况下,SG和AUSG聚集在一起,AWSG和AWUSG也是如此。然而,在ION变化的情况下,SG和AWUSG则更为接近。这是非常理想的,因为它表明AWUSG鳍式场效应晶体管在广泛的参数值范围内兼具AWSG FinFET的IOFF特性和SG FinFETs的ION特性。

LG,(b) TSI,(c) TOX,(d) LUN,(e) ϕG,,以及 (f) VDD)

G长度,(b) SI温度,(c) OX温度,(d) UN长度,(e) ϕG,以及(f) DD电压)

3.4. 对温度变化的敏感性

IOFF随着温度T的升高,鳍式场效应晶体管的指数增长。图17显示了这一趋势。然而,在较高温度下,AWSG和AWUSG鳍式场效应晶体管相较于单栅鳍式场效应晶体管和AUSG FinFET仍保持其相对优势。ION随T的变化不大。例如,在较宽的T(300–373K)变化范围内,所有考虑的器件类型中ION的变化均在10%以内。

3.5. 工艺变异的影响

LG,TSI,TOX,LUN,ϕG,以及VDD已被证明是最容易受到工艺变异影响的参数[Xiong 和 Bokor 2003;Mishra 等人 2010]。在本节中,我们分析了SG/AWSG/AUSG/AWUSG nFinFET1×在这些参数组合变化下的鲁棒性。我们采用基于Sobol序列的拟蒙特卡洛模拟[Singhee 和 Rutenbar 2007],,该方法相较于蒙特卡洛模拟,仅需几个数量级更少的样本即可达到相似的精度,用于此分析。因此,我们使用量子蒙特卡罗模拟生成100个样本变异情况,每个参数具有 3 ∗ σ/μ= 10%的变化,并使用这些值进行三维流体动力学器件仿真。我们在图18中展示了在这种变异下的IOFF和ION分布。可以看出,与其他鳍式场效应晶体管相比,AWUSG鳍式场效应晶体管具有合理的ION/IOFF分布范围。

IOFF在工艺变异下的SG/AWSG/AUSG/AWUSG nFinFET的导通电流分布,(b) ION分布工艺变异下SG/AWSG/AUSG/AWUSG nFinFET的特性)

4. 鳍式场效应晶体管逻辑门

在本节中,我们研究了基于上一节所述FinFET构建的逻辑门的漏电‐延迟特性。我们重点关注尺寸为 1/2×的逻辑门。表VI和表VII显示了在300K温度下, 1×和2×逻辑门在所有输入向量下的平均泄漏电流(ILEAK)。正如预期,从表VIII、表IX、表X和表XI可以看出,基于AWSG和AWUSG FinFET的1/2×逻辑门在这方面保持了其优势,即使在不同温度下也是如此。在表XII和表XIII中,我们比较了1/2×逻辑门的延迟。我们观察到AWUSG反相器1×(2×)、与非门1×(2×)和或非门1×(2×)的延迟分别降低了15.0%(14.5%)、4.2%(4.8%)和12.4%(12.5%)。

| 类型 | 反相器(nA) | %变化 | 与非门(nA) | %变化 | 或非门 (nA) | %变化 |

|---|---|---|---|---|---|---|

| SG | 1.03 | − | 1.15 | − | 1.18 | − |

| AWSG | 0.02 | −98.1 | 0.03 | −97.4 | 0.03 | −97.5 |

| AUSG | 2.84 | 175.7 | 3.10 | 169.6 | 2.53 | 114.4 |

| AWUSG | 0.06 | − 94.2 | 0.06 | − 94.8 | 0.06 | − 94.9 |

表VI. 1×逻辑门在T= 300K下的ILEAK比较

| 类型 | 反相器 (nA) | %变化 | 与非门 (nA) | %变化 | 或非门 (nA) | %变化 |

|---|---|---|---|---|---|---|

| SG | 2.05 | − | 2.30 | − | 2.35 | − |

| AWSG | 0.04 | −98.1 | 0.06 | −97.4 | 0.06 | −97.5 |

| AUSG | 5.67 | 176.6 | 6.20 | 169.6 | 5.06 | 115.3 |

| AWUSG | 0.12 | −94.2 | 0.12 | −94.8 | 0.12 | −94.9 |

表七。ILEAK在T= 300K时逻辑门的比较 2×

| 类型 | 反相器 (nA) | %变化 | 与非门 (nA) | %变化 | 或非门 (nA) | %变化 |

|---|---|---|---|---|---|---|

| SG | 7.02 | − | 7.75 | − | 8.40 | − |

| AWSG | 0.21 | −97.0 | 0.23 | −97.0 | 0.28 | −96.7 |

| AUSG | 16.51 | 135.2 | 17.93 | 131.4 | 17.93 | 113.5 |

| AWUSG | 0.51 | −92.7 | 0.56 | −92.8 | 0.62 | −92.6 |

表八。在{T}K下逻辑门的ILEAK比较

| 类型 | 反相器 (nA) | %变化 | 与非门 (nA) | %变化 | 或非门 (nA) | %变化 |

|---|---|---|---|---|---|---|

| SG | 14.04 | − | 15.49 | − | 16.80 | − |

| AWSG | 0.42 | −97.0 | 0.46 | −97.0 | 0.56 | −96.7 |

| AUSG | 33.03 | 135.3 | 35.85 | 131.4 | 35.85 | 113.4 |

| AWUSG | 1.01 | −92.8 | 1.12 | −92.8 | 1.24 | −92.6 |

表IX。 2×逻辑门在T= 348K下的ILEAK比较

| 类型 | 反相器 (nA) | %变化 | 与非门 (nA) | %变化 | 或非门 (nA) | %变化 |

|---|---|---|---|---|---|---|

| SG | 15.81 | − | 17.29 | − | 19.32 | − |

| AWSG | 0.56 | −96.5 | 0.61 | −96.5 | 0.74 | −96.2 |

| AUSG | 34.69 | 119.4 | 37.50 | 116.9 | 38.29 | 98.2 |

| AWUSG | 1.31 | −91.7 | 1.42 | −91.8 | 1.58 | −91.8 |

表 X. ILEAK在 T= 373K 下 1× 逻辑门 的比较

| 类型 | 反相器 (nA) | %变化 | 与非门 (nA) | %变化 | 或非门 (nA) | %变化 |

|---|---|---|---|---|---|---|

| SG | 31.62 | − | 34.57 | − | 38.64 | − |

| AWSG | 1.12 | −96.5 | 1.22 | −96.5 | 1.47 | −96.2 |

| AUSG | 69.37 | 119.4 | 75.00 | 117.0 | 76.58 | 98.2 |

| AWUSG | 2.62 | −91.7 | 2.83 | −91.8 | 3.15 | −91.8 |

表XI。在T= 373K时 2×逻辑门的ILEAK比较

| 类型 | 反相器(皮秒) | %变化 | 与非门(皮秒) | %变化 | 或非门(皮秒) | %变化 |

|---|---|---|---|---|---|---|

| SG | 5.54 | − | 9.57 | − | 6.36 | − |

| AWSG | 7.09 | 28.0 | 12.88 | 34.6 | 8.27 | 30.0 |

| AUSG | 3.71 | −33.0 | 7.22 | −24.6 | 4.63 | −27.2 |

| AWUSG | 4.71 | −15.0 | 9.17 | −4.2 | 5.57 | −12.4 |

表十二。逻辑门延迟(tD)比较

| 类型 | 反相器(皮秒) | %变化 | 与非门(皮秒) | %变化 | 或非门(皮秒) | %变化 |

|---|---|---|---|---|---|---|

| SG | 2.76 | − | 4.79 | − | 3.19 | − |

| AWSG | 3.53 | 27.9 | 6.43 | 34.2 | 4.14 | 29.8 |

| AUSG | 1.86 | −32.6 | 3.60 | −24.8 | 2.30 | −27.9 |

| AWUSG | 2.36 | − 14.5 | 4.56 | −4.8 | 2.79 | − 12.5 |

表十三. 逻辑门延迟(tD)比较 2×

与相应的单栅FinFET逻辑门相比,这些门分别具有更低的延迟和显著降低的漏电流。 1× (2×)反相器、与非门和或非门中的所有n型鳍式场效应晶体管分别包含1(2)、1(2)和1 (2)个鳍片,而所有p型鳍式场效应晶体管则分别包含2(4)、1(2)和4(8)个鳍片。选择这些配置是为了补偿空穴和电子迁移率之间的差异,并实现相近的上升/下降延迟。这解释了为什么与非门的延迟高于或非门的延迟。注意,一个 2×与非门仅有8个鳍片(而一个1×或非门有10个鳍片)。因此, 2×与非门在占用更小面积的同时比 1×或非门更快。

5. FinFET 逻辑电路

在本节中,我们评估AWUSG鳍式场效应晶体管相对于单栅鳍式场效应晶体管的电路级影响。由于基于AWUSG鳍式场效应晶体管的逻辑门速度更快,我们首先获得基于 1×逻辑门(反相器/NAND/NOR)的最快可能的电路实现。

| 基准电路 | 关键路径延迟 (ps) |

|---|---|

|

c432

c499 c880 c1355 c2670 c3540 c5315 c7552 |

660

773 608 764 648 1161 782 809 |

表十四. 采用AWUSGFinFETs的ISCAS’85基准电路最快实现的关键 路径延迟

| 基准电路 | 关键路径延迟 (ps) |

|---|---|

|

s510

s641 s713 s820 s832 s1238 s1423 s1488 s5378 s15850 s35932 s38584 |

116

284 300 134 163 480 315 213 444 980 222 869 |

表十五。基于AWUSG鳍式场效应晶体管的 ISCAS’89基准电路最快实现的关键路径延迟

使用AWUSG鳍式场效应晶体管构建(因此这些实现也占用最小面积)。表十四和表十五分别显示了ISCAS’85和ISCAS’89基准电路实现的关键路径延迟。接下来,我们将这些关键路径延迟设置为使用Synopsys设计编译器[Synopsys2011]进行综合的时序约束,该综合基于包含 1×和 2×单栅FinFET逻辑门(反相器/NAND/NOR)的SG库。需要注意的是,由于单栅FinFET逻辑门速度较慢,仅使用 1×逻辑门将不足以满足时序约束。

表十六显示了ISCAS’85基准电路的结果。PD表示动态功耗,PL348、PT348、PL373和PT373分别表示在348K下的泄漏功耗、在348K下的总功耗、在373K下的泄漏功耗以及在373K下的总功耗。尽管SG实现在所有情况下均满足时序约束,但AWUSG实现平均减少了12.0%的面积。更重要的是,AWUSG实现还分别平均降低了25.6%(41.8%)在348K(373K)下的总功耗。

我们在表十七中报告了ISCAS’89基准电路的结果。AWUSG实现平均减少了14.5%的面积,同时分别平均降低了38.2%(50.4%)在348K (373K)下的总功耗。由于延迟在FinFET电路中对温度不敏感,我们忽略此效应。无论如何,由于温度升高会导致SG和AWUSG电路的延迟发生类似的微小增加,因此在比较分析中无需考虑这一现象。

我们可以将此类库部署到更高级别的架构级仿真工具中,例如FinCANON [Lee和Jha 2014]以及McPAT‐PVT [Tang等 2015],以实现完整的

| Benchmarks | Type | VDD(V) | PD(μW) | PL348(μW) | PL373(μW) | PT348(μW) | % Reduction | PT373(μW) | % Reduction | tD(ps) | Area | % Reduction |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| c432 | SG | 0.9 | 10.04 | 6.04 | 12.82 | 16.08 | - | 22.86 | - | 659.1 | 3445 | - |

| AWUSG | 0.9 | 11.29 | 0.34 | 0.80 | 11.63 | 27.7 | 12.09 | 47.1 | 660 | 3509 | -1.9 | |

| c499 | SG | 0.9 | 67.13 | 14.73 | 31.29 | 81.86 | - | 98.42 | - | 769.8 | 8710 | - |

| AWUSG | 0.9 | 71.65 | 0.77 | 1.83 | 72.42 | 11.5 | 73.48 | 25.3 | 773 | 8183 | 6.1 | |

| c880 | SG | 0.9 | 21.49 | 13.29 | 28.24 | 34.78 | - | 49.73 | - | 606.5 | 7960 | - |

| AWUSG | 0.9 | 22.83 | 0.65 | 1.54 | 23.48 | 32.5 | 24.37 | 51.0 | 608 | 6782 | 14.8 | |

| c1355 | SG | 0.9 | 80.40 | 16.67 | 35.42 | 97.07 | - | 115.82 | - | 763.6 | 9826 | - |

| AWUSG | 0.9 | 72.92 | 0.75 | 1.78 | 73.67 | 24.1 | 74.70 | 35.5 | 764 | 8016 | 18.4 | |

| c2670 | SG | 0.9 | 46.35 | 19.94 | 42.38 | 66.29 | - | 88.73 | - | 646.8 | 11988 | - |

| AWUSG | 0.9 | 48.98 | 1.12 | 2.65 | 50.10 | 24.4 | 51.63 | 41.8 | 648 | 11384 | 5.0 | |

| c3540 | SG | 0.9 | 82.42 | 38.34 | 81.54 | 120.76 | - | 163.96 | - | 1161.0 | 22678 | - |

| AWUSG | 0.9 | 78.94 | 1.78 | 4.23 | 80.72 | 33.2 | 83.17 | 49.3 | 1161 | 18346 | 19.1 | |

| c5315 | SG | 0.9 | 129.07 | 52.17 | 110.90 | 181.24 | - | 239.97 | - | 781.8 | 31105 | - |

| AWUSG | 0.9 | 122.17 | 2.49 | 5.89 | 124.66 | 31.2 | 128.06 | 46.6 | 782 | 25552 | 17.9 | |

| c7552 | SG | 0.9 | 193.31 | 75.53 | 160.51 | 268.84 | - | 353.82 | - | 808.9 | 43309 | - |

| AWUSG | 0.9 | 212.13 | 3.58 | 8.50 | 215.71 | 19.8 | 220.63 | 37.6 | 809 | 35970 | 17.0 |

Table XVI. SG vs. AWUSG Implementations at Different Temperatures for ISCAS’85 Benchmarks

| Benchmarks | Type | VDD(V) | PD(μW) | PL348(μW) | PL373(μW) | PT348(μW) | % Reduction | PT373(μW) | % Reduction | tD(ps) | Area | % Reduction |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| s510 | SG | 0.9 | 18.85 | 6.27 | 13.37 | 25.12 | - | 32.22 | - | 115.5 | 4273 | - |

| AWUSG | 0.9 | 25.22 | 0.32 | 0.76 | 25.54 | 25.98 | 19.4 | 116 | 3700 | 13.4 | ||

| s641 | SG | 0.9 | 6.29 | 6.96 | 14.78 | 13.25 | - | 21.07 | - | 283.0 | 4109 | - |

| AWUSG | 0.9 | 5.85 | 0.32 | 0.76 | 6.17 | 53.4 | 6.61 | 68.6 | 284 | 3525 | 14.2 | |

| s713 | SG | 0.9 | 6.09 | 6.36 | 13.53 | 12.45 | - | 19.62 | - | 299.8 | 3838 | - |

| AWUSG | 0.9 | 5.74 | 0.30 | 0.72 | 6.04 | 51.5 | 6.46 | 67.1 | 300 | 3355 | 12.6 | |

| s820 | SG | 0.9 | 12.42 | 8.25 | 17.58 | 20.67 | - | 30.00 | - | 133.6 | 5454 | - |

| AWUSG | 0.9 | 15.08 | 0.36 | 0.86 | 15.44 | 25.3 | 15.94 | 46.9 | 134 | 4177 | 23.4 | |

| s832 | SG | 0.9 | 10.81 | 7.79 | 16.59 | 18.60 | - | 27.40 | - | 162.4 | 5072 | - |

| AWUSG | 0.9 | 12.15 | 0.37 | 0.88 | 12.52 | 32.7 | 13.03 | 52.5 | 163 | 4184 | 17.5 | |

| s1238 | SG | 0.9 | 18.95 | 16.45 | 35.03 | 35.40 | - | 53.98 | - | 479.7 | 10502 | - |

| AWUSG | 0.9 | 20.78 | 0.87 | 2.05 | 21.65 | 38.8 | 22.83 | 57.7 | 480 | 9416 | 10.3 | |

| s1423 | SG | 0.9 | 23.60 | 16.42 | 34.93 | 40.02 | - | 58.53 | - | 314.8 | 10284 | - |

| AWUSG | 0.9 | 22.64 | 0.76 | 1.79 | 23.40 | 41.6 | 24.43 | 58.3 | 315 | 8688 | 15.5 | |

| s1488 | SG | 0.9 | 90.79 | 22.54 | 47.98 | 113.33 | - | 138.77 | - | 212.9 | 14325 | - |

| AWUSG | 0.9 | 97.31 | 1.03 | 2.44 | 98.34 | 13.2 | 99.75 | 28.1 | 213 | 11271 | 21.3 | |

| s5378 | SG | 0.9 | 40.86 |

138

138

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?