文章目录

前言

门控时钟是降低数字电路功耗的一个重要手段,在ASIC设计中,设计工具都可以根据使用者的设置自动的完成门控时钟的添加。本文简单描述了门控时钟的概念,并给出了使用DC进行门控时钟添加的操作说明,是初学ASIC设计的学习笔记分享。

1. 门控时钟简介

数字电路的工作动态功耗主要是由于寄存器翻转带来的,为了降低芯片内部功耗,门控时钟的方案应用而生。作为低功耗设计的一种方法,门控时钟是指在数据无效时将寄存器的时钟关闭,以此来降低动态功耗。

由于门控时钟会在时钟路径上增加逻辑,使用门控时钟会影响时序分析。

2. 门控时钟的实现方式

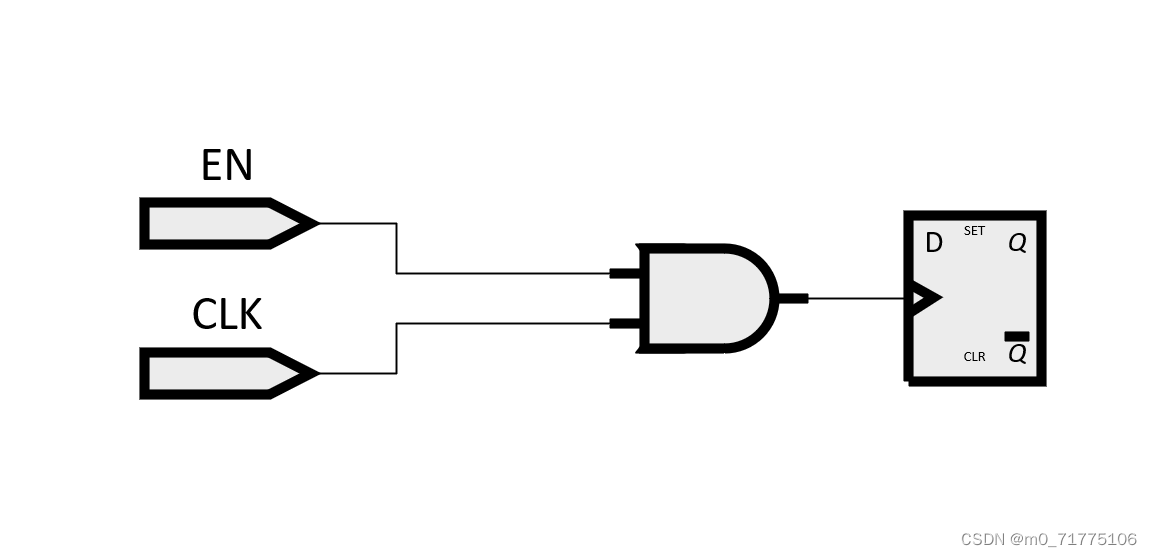

2.1 逻辑门控

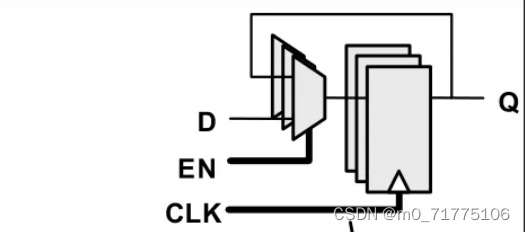

2.2 锁存门控

逻辑门控不可避免会由于EN信号的不稳定导致时钟出现毛刺,为了解决这个问题,可以考虑将EN使用CLK进行锁存,让EN只有在CLK为低的时候锁存,为高的时候保持不变,这就是锁存门控时钟。

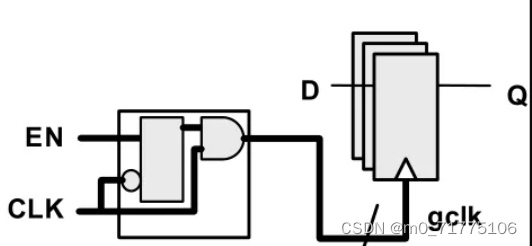

2.3 寄存门控

锁存门控仍然存在如下问题:

- 如果在电路中锁存器与与门相隔很远,到达锁存器的时钟与到达与门的时钟有较大的延迟差别,则仍会出现毛刺;

- 如果在电路中,时钟使能信号距离锁存器很近,可能会不满足锁存器的建立时间,会造成锁存器输出出现亚稳态。

具体分析可以参见后附参考文档。

为了解决锁存门控的问题,可以采用寄存门控,即将锁存器改为寄存器,使用CLK对EN信号进行寄存操作,也就是使用CLK的沿触发而不是电平触发来控制EN信号。

2.4 门控时钟结构的选择

在实际的ASIC设计中,一般采用的是集成门控,也就是说是由厂家工艺库中提供的标准单元。一般该标准单元是锁存门控形式,这是由于在厂家的设计当中,线延时是可控和不变的,而且可以通过挑选锁存器和增加延时,总是能满足锁存器的建立时间,这样通过工艺厂预先把门控时钟做出标准单元,可以解决锁存门控电路的问题,同时也避免采用面积更大的寄存门控结构。

3. 使用DC工具添加门控时钟

实际ASIC设计中,门控时钟不需要开发者自己写代码实现,完全可以通过对综合工具进行相应配置,让工具完成对电路添加合适的门控时钟。

3.1 门控时钟的自动添加

门控时钟的使能信号是在其所控制的寄存器的输入输出不变的情况下关闭,因此可以由工具进行这样的判断,并自动添加时钟的门控电路,换言之,可以将对输入信号的enable控制改变为对时钟的控制。具体的,考虑如下一段代码:

always@ {posedge clk)

if(valid) begin

dout <= din;

end

end

没有加入门控时钟时,该段代码综合出来的电路为:

加上门控时钟后,该段代码综合出来的电路为:

由上面的图可以看出,插入门控时钟单元后,原有电路中的MUX就不需要了,如果数据位宽是多bit的,插入clock_gating后,电路面积可能反而会减少;但如果数据是单bit信号,那么节省的功耗就比较少。

因此,工具可以根据位宽来决定是否增加门控时钟。如果位宽很小,那么插入的clock_gating面积比原来的MUX有可能大很多,但节省的功耗又很少,性价比不高;只有当位宽超过了一定的bit数后,才有必要插入clock_gating。这个门限在DC综合时可以由-minimum_bitwidth进行设置。

3.2 使用DC添加门控时钟

DC中添加门控时钟有两种方式:

- 使用insert_clock_gating命令

- 在compile_ultra命令中添加-gate_clock开关

不管使用哪种方式,都首先需要通过set_clock_gating_style命令来配置相应的门控时钟参数。

3.3 使用set_clock_gating_style命令的配置

在dc_shell中输入man set_clock_gating_style可以查看具体的配置说明,这里列出其中几个主要的配置:

- -global:可以使门控时钟穿越层次结构。如果不用选项“-global",在每个模块里都会产生一个门控时钟单元;

- -minimum_bitwidth:用于设置进行时钟门控的寄存器阵列的最小宽度。对于宽度小于该设置的寄存器阵列,不进行时钟门控;然而当电路由有公共使能时,会对电路进行分解进行集体门控;

-max_fanout:设置一个门控单元所驱动的最大负载数目,定义CG单元最大扇出的一个目的是减少CG后面的时钟延迟,门控时钟单元的扇出越大,它到达寄存器的延迟越长;此外,还有用来约束重新平衡; - -num_stages:用于设置一个多级门控的级数。在有些设计中,顶层的门控信号会分解成不同的子门控信号。在缺省情况下,仅对跟寄存器阵列相连的门控制信号生成门控逻辑;

- -sequential_cell,该选项设置采用何种门控时钟风格:

- -sequential_cell latch:基于锁存器的离散门控单元,该配置为默认值;

- -sequential_cell none:采用不适用锁存器的门控单元;

- -positive_edg_logic:简写为-positive或-pos,设置在RTL代码中用上升沿锁存的寄存器(也就是上升沿沿触发的寄存器)采用何种门控逻辑,如-pos “or”表示对于上升沿触发的寄存器,采用或门逻辑进行门控,-pos "integrated"表示对于上升沿触发的寄存器采用集成门控单元进行门控;

- -negative_edg_logic:简写为-negative或-neg,设置在RTL代码中用下降沿锁存的寄存器(也就是下降沿触发的寄存器)采用何种门控逻辑;

- -control_point和-control_signal:这两个开关和DFT有关,用于设置该门控单元在DFT时是否可控,DFT控制信号是scan-enable还是test-mode,以及DFT控制信号与EN信号的组合逻辑是放在门逻辑中的锁存器之前还是之后。通常,将DFT控制信号与EN信号进行或操作,这样在DFT时,可以控制该门控逻辑;

- -observation_point:该开关和DFT有关,用于设置是否要插入观测逻辑,以便在DFT时能看到门控逻辑内部的信号;

-setup:设置建立时间约束;

-hold:设置保持时间约束;

-observation_logic_depth:设置观察电路中异或门的数目。

通常的设置参数如下:

set_clock_gating_style "integrated" -max_fanout 30 -minimum_bitwidth 4

insert_clock_gating -global

propagate_constraints -gate_clock

参考文献

- 芯片设计进阶之路——门控时钟,https://zhuanlan.zhihu.com/p/139363948

- Verilog设计(一):时钟门控,https://blog.youkuaiyun.com/qq_26652069/article/details/95458771

- 【转载】门控时钟的一些基本概念,https://blog.youkuaiyun.com/dinsh3100/article/details/124360952

2440

2440

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?