SystemVerilog中的inside是一个非常重要的操作符,它属于集合操作符的一种,主要用于检查一个表达式的值是否位于一个指定的值集合或范围内。这种操作符的使用可以使得编码更为高效和简洁。以下是inside在SystemVerilog中的一些常见使用方法:

inside操作符的基本语法格式为:

expression inside { range_list }

1 随机约束

在约束块中,可以使用inside来指定随机变量的取值范围。例如:

rand int src;

constraint c_dist { src inside {0, 1, 2, 3}; };

constraint c {

// inclusive

src_port inside { [8'h0:8'hA],8'h14,8'h18 };

// exclusive

! (des_port inside { [8'h4:8'hFF] });

}

2 条件判断

可以将inside用作if、while、for语句的判断条件,用于判断某个变量的取值是否满足合法的取值列表。例如:

logic[2:0] a;

if (a inside {3'b001, 3'b010, 3'b100})

// 等价于 if ((a == 3'b001) || (a == 3'b010) || (a == 3'b100))

Inverted inside

Inverted inside

class ABC;

rand bit [3:0] m_var;

// Inverted inside: Constrain m_var to be outside 3 to 7

constraint c_var { !(m_var inside {[3:7]}); }

endclass

module tb;

initial begin

ABC abc = new();

repeat (5) begin

abc.randomize();

$display("abc.m_var = %0d", abc.m_var);

end

end

endmodule

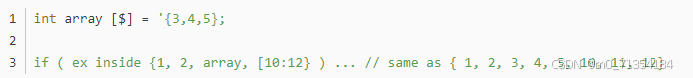

3 与数组结合使用

inside操作符右边的取值列表可以是一个数组。例如:

int d_array[0:1023];

if (13 inside d_array)

4 使用z或x表示无关条件

inside操作符可以使用z或x(x还可以用?表示)来表示无关条件。例如:

logic[2:0] a;

if (a inside {3'b1?1})

// 如果 a 含有 3'b101、3'b111、3'b1x1、3'b1z1 值,结果都为真

5 在case语句中使用

在case语句的选择分支中,可以使用inside来表示满足某个特定范围取值的分支。例如:

logic[2:0] sel;

case (sel)

inside {3'b001, 3'b010}: // 当 sel 为 3'b001 或 3'b010 时执行

// 执行相应的代码

default:

// 其他情况执行的代码

endcase

6 条件赋值(三元运算符)

利用inside是否满足取值列表的性质,可以取代===操作符,用于条件赋值。例如:

logic flag;

flag = (value inside {1, 2, 3})? 1 : 0;

// 如果 value 的值在 1、2、3 中,flag 被赋值为 1,否则为 0

module tb;

bit [3:0] m_data;

bit flag;

initial begin

for (int i = 0; i < 10; i++) begin

m_data = $random;

// Used in a ternary operator

flag = m_data inside {[4:9]} ? 1 : 0;

// Used with "if-else" operators

if (m_data inside {[4:9]})

$display ("m_data=%0d INSIDE [4:9], flag=%0d", m_data, flag);

else

$display ("m_data=%0d outside [4:9], flag=%0d", m_data, flag);

end

end

endmodule

7 inside的返回值

在 SystemVerilog 的case语句中,inside操作符用于检查一个表达式的值是否在一个指定的值集合内。它的返回值是一个布尔值(1'b0或1'b1)。

inside操作符会将左边expression的值与右边open_range_list里的值逐一比较,如果找到匹配的值,返回1,反之返回0。

可以用在while循环中,或if循环中

int a;

int b;

int c;

int q[$] = '{7,8,9,67};

if(a inside{1,2,3,4,q,[12:18]}) c= 56;

else c = 9;

while(a inside {2,3,4,[4,9],array}) begin

end

1023

1023

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?