DDS信号发生器原理

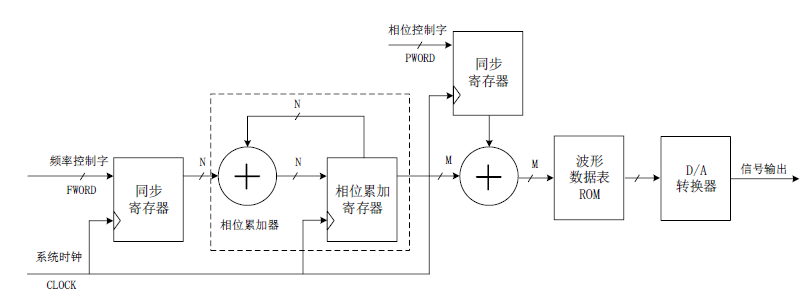

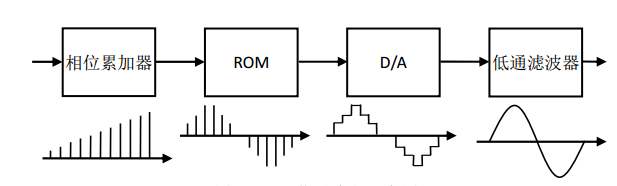

DDS主要由相位累加器、相位调制器、波形数据表以及D/A转换器构成。其中相位累加器由N位加法器与N位寄存器构成。每个时钟周期的时钟上升沿,加法器就将频率控制字与累加寄存器输出的相位数据相加,相加的结果又反馈至累加寄存器的数据输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。即在每一个时钟脉冲输入时,相位累加器便把频率控制字累加一次。

相位累加器输出的数据就是合成信号的相位。相位累加器的溢出频率,就是DDS输出的信号频率,相位累加器输出的数据,作为波形存储器的相位采样地址,这样就可以把存储在波形存储器里的波形采样值经查表找出,完成相位到幅度的转换。

波形存储器的输出数据送到 D/A 转换器,由 D/A 转换器将数字信号转换成模拟信号输出。

AD9767模块介绍

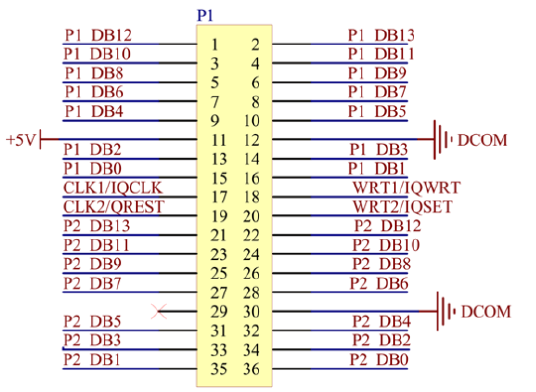

有两个通道,每个通道的数据分辨率为14位,转换速率最高可达到125Mbps,输出电压范围为+/-5V。

ACM9767模块是一款高性能高速双通道 DAC 模块。 模块具有单电源 5V 供电输入,双通道数字转模拟信号输出,每个通道数据分辨率为 14 位, 输出电压范围为+-5V, 且转换速率高达125Msps,非常适合诸如信号发生器、数字调制通信系统的开发等应用。

设计要求

- 做一个双通道的信号发生器

- 能够简单的调整每个通道的频率输出

- 能够提哦啊正每个通道的输出相位

- 能够控制输出的波形形式(sine,方波,三角波等)

设计代码

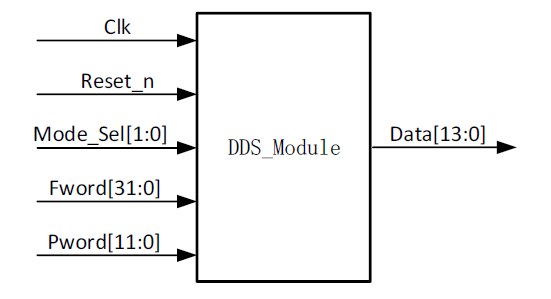

DDS 模块

module DDS_Module(

Clk,

Reset_n,

Mode_Sel,

Fword,

Pword,

Data

);

input Clk;

input Reset_n;

input [1:0]Mode_Sel; //模式切换

input [31:0]Fword;

input [11:0]Pword;

output reg[13:0]Data;

//频率控制字同步寄存器

reg [31:0]Fword_r;

always@(posedge Clk)

Fword_r <= Fword;

//相位控制字同步寄存器

reg [11:0]Pword_r;

always@(posedge Clk)

Pword_r <= Pword;

//相位累加器

reg [31:0]Freq_ACC;

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

Freq_ACC <= 0;

else

Freq_ACC <= Fword_r + Freq_ACC;

//波形数据表地址

wire [11:0]Rom_Addr;

assign Rom_Addr = Freq_ACC[31:20] + Pword_r;

wire [13:0]Data_sine,Data_square,Data_triangular;

//调用底层模块ROM表(由ip核生成的三种波形:sine,方波,三角波)

rom_sine rom_sine(

.clka(Clk),

.addra(Rom_Addr),

.douta(Data_sine)

);

rom_square rom_square(

.clka(Clk),

.addra(Rom_Addr),

.douta(Data_square)

);

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4370

4370

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?