BLE基带调制模块是采用的GFSK调制。

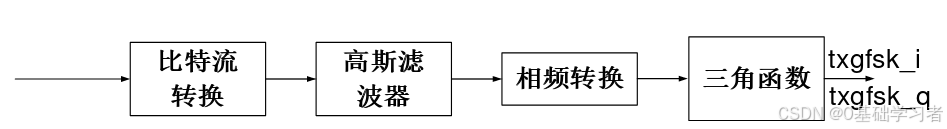

BLE调制模块结构

BLE调制模块共分为四个模块,包括比特流转换模块、高斯滤波 器模块、相频转换模块、三角函数模块。由基带产生的tx_data是1Mbps的二进制比特流,也是调制信号,经过比特流转换模块把RZ码转换成NRZ码,再经过高斯滤波器, 得到频带较窄的脉冲信号,经过相频转换模块得到相位信息。通过三角函数模块,实现 相位到幅度地映射,输出两路正交的信号。

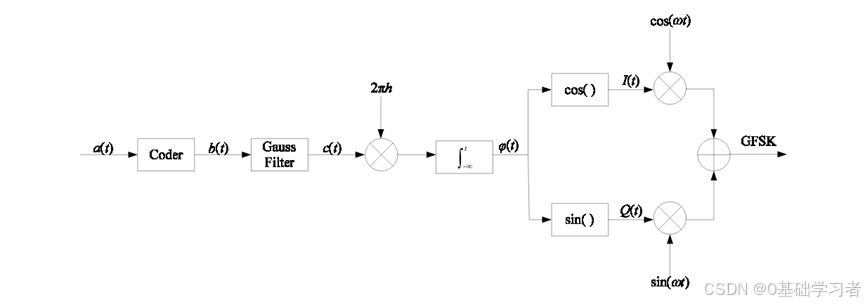

GFSK调制信号处理流程图

各个模块的作用:

-

比特流转换模块:这个模块的主要功能是将基带产生的tx_data二进制比特流从RZ(Return to Zero,返回零)码转换成NRZ(Non-Return to Zero,非返回零)码。在RZ编码中,每一个比特的有效信息是由信号的存在与否来表示,而每个比特结束时信号必须返回到零。相比之下,NRZ编码中的信号不需要在每个比特结束时返回到零,这样可以使数据传输更加高效。

-

高斯滤波器模块:该模块通过高斯滤波器处理NRZ信号,产生频带较窄的脉冲信号。高斯滤波器能够平滑信号的边缘,减少带宽占用,并且在一定程度上抑制高频噪声,这对于无线信号传输非常重要。

-

相频转换模块:这个模块接收通过高斯滤波器处理后的信号,用来获取信号的相位信息。相位信息是进行相位调制(如PSK)的关键,通过改变信号的相位来传递信息。

-

三角函数模块:在获取到相位信息后,三角函数模块用于将相位信息转换成幅度信息,实现从相位到幅度的映射。这样,最终输出的是两路正交的信号(I路和Q路),它们可以用于构造复信号,进一步用于调制。

比特流转换模块

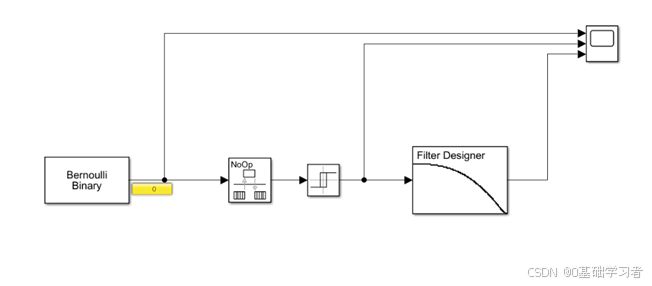

比特流转换电路以及高斯滤波器在simulink中的实现

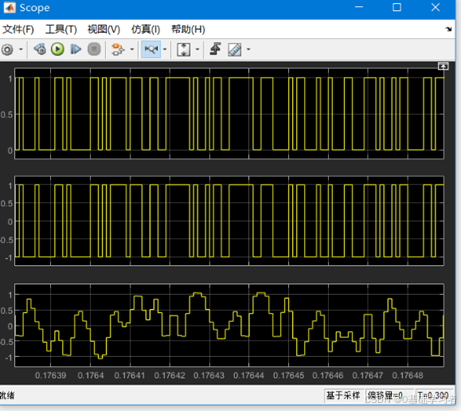

由于基带输出的信息序列是1Mbps的RZ码,所以第一个图是1Mbps的输入RZ码,第二个图是由RZ码转换来的NRZ码,第三个图是经过高斯滤波器后的波形。

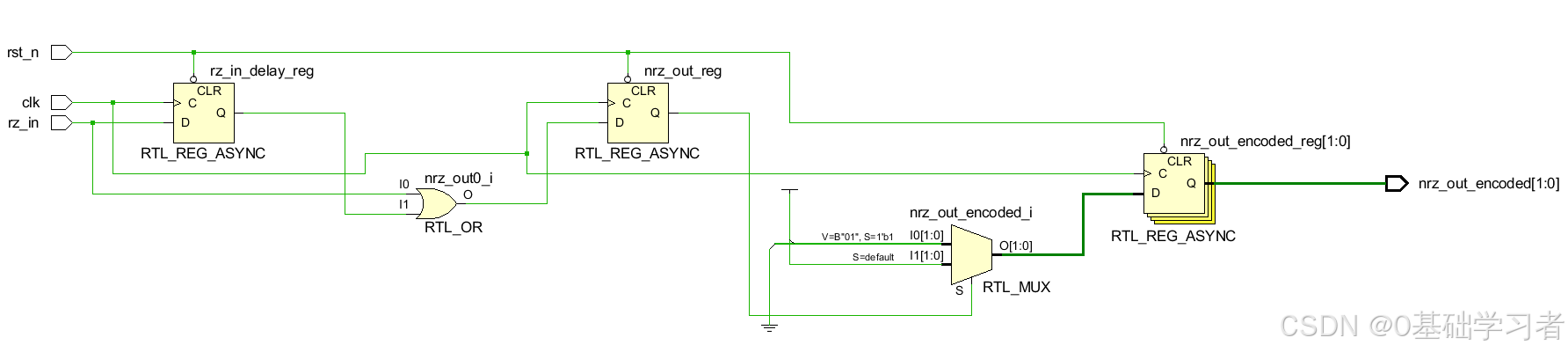

利用verilog来实现

在这个比特流转换电路里面,输入信号是由基带产生的tx_data是1Mbps的二进制比特流,也是调制信号,经过比特流转换模块把RZ码转换成NRZ码。由于数字电路中仅有0和1,因此要对NRZ码进行再编码,所以我用00、01、11分别表示0,1,-1。

module RZ_to_NRZ_Reencoded(

input clk,

input rst_n,

input rz_in, // RZ编码输入

output reg [1:0] nrz_out_encoded // 再编码的NRZ输出

);reg nrz_out; // NRZ中间信号

reg rz_in_delay; // 用于延迟RZ输入信号的寄存器// RZ到NRZ的转换逻辑

always @(posedge clk or negedge rst_n)begin

if (!rst_n)begin

nrz_out <= 0;

rz_in_delay <= 0;

endelse

begin

rz_in_delay <= rz_in;

nrz_out <= rz_in | rz_in_delay;

end

end// NRZ到再编码的逻辑

always @(posedge clk or negedge rst_n)begin

if (!rst_n) begin

nrz_out_encoded <= 2'b00; // 默认为'0'(00)

endelse if (nrz_out == 1) begin

nrz_out_encoded <= 2'b00; // NRZ '1' 即(01)

endelse begin

nrz_out_encoded <= 2'b11; // NRZ '-1' 即(11)

end

endendmodule

rz_in_delay <= rz_in;

这行代码的作用是将当前时钟周期的rz_in输入值存储到rz_in_delay寄存器中。rz_in_delay用作延迟寄存器,它在下一个时钟周期保留了rz_in的前一个状态。这样,rz_in_delay总是比rz_in延迟一个时钟周期的数据。

nrz_out <= rz_in | rz_in_delay;

这行代码是逻辑或操作,它将当前的rz_in输入和延迟后的rz_in_delay输入进行逻辑或运算。这个操作的目的是从RZ编码转换到NRZ编码。让我们来看一下这样做的逻辑基础:

- 在RZ编码中,一个逻辑

1通常表示为一个周期内前半部分为高电平(1),后半部分为低电平(0)。逻辑0则表示整个周期为低电平(0)。 - 为了转换成NRZ编码,我们需要保持逻辑

1的状态在整个周期内都为高电平。即,如果在当前或前一个时钟周期内rz_in是高(1),那么nrz_out也应为高(1)来表示NRZ中的连续高电平状态。

通过这种方式,如果rz_in在当前周期或前一周期为高(即使它是RZ编码中的短暂高电平),nrz_out将在当前周期输出高电平,从而有效地将RZ编码的短暂高电平转换为NRZ编码的持续高电平。这样的转换对于数据传输和信号处理非常关键,因为NRZ编码通常在通信系统中更为常用,其稳定的信号状态有助于降低误差率和提高数据传输效率。

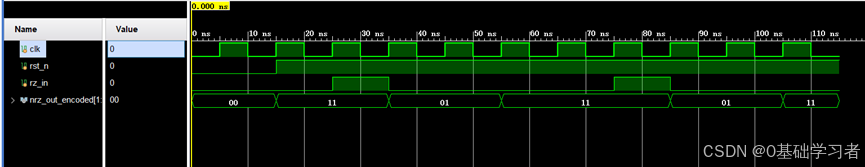

测试模块:比特流转换及再编码仿真

module test_RZ_to_NRZ_Reencoded; reg clk; reg rst_n; reg rz_in; wire [1:0] nrz_out_encoded; // 实例化比特流转换及再编码模块 RZ_to_NRZ_Reencoded converter ( .clk(clk), .rst_n(rst_n), .rz_in(rz_in), .nrz_out_encoded(nrz_out_encoded) ); always #5 clk = ~clk; initial begin clk = 0; rst_n = 0; rz_in = 0; #15 rst_n = 1; #10 rz_in = 1; #10 rz_in = 0; #20 rz_in = 0; #20 rz_in = 1; #10 rz_in = 0; #30 $stop; end endmodule

测试验证的结果和理论相符。NRZ码进行再编码,用01、11、00分别表示1,-1,0。

957

957

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?