在反馈路径中使用分频器使得锁相环(PLL)能够执行倍频。

- 当采用可编程分频器时,PLL成为频率合成器,为无线系统中的不同信道生成多个频率。

- 在数字系统中,具有固定或可变分频比的PLL充当时钟乘法器单元。

分频器是频率合成器低功耗设计的重要模块。

根据工作原理,分频器可以分为三种类型:

- 整数分频器(数字)

- 小数分频器(混合模式)

- 注入锁定分频器(模拟)

| 整数分频器 | 输出信号的周期是输入信号的周期的整数倍 后跟可编程计数器 |

| 分数分频器 | 输出信号的平均周期可以是输入信号周期的非整数倍 1.使用多相输入并执行相位选择 2. 基于过采样数字调制的 |

| 注入锁定分频器 | 使用再生电路的谐波锁定特性来执行分频 |

1. 带预分频器的分频

由于分频器是频率合成器中功耗最大的模块,可编程分频器的设计并不基于直接使用同步计数器。

为了降低功耗,设计了基于预分频方法的可编程分频器,以减少同步触发器的数目。

DMD是一种分频器,它提供两种分频模式,通常具有连续的分频值。

1.1 分频原理

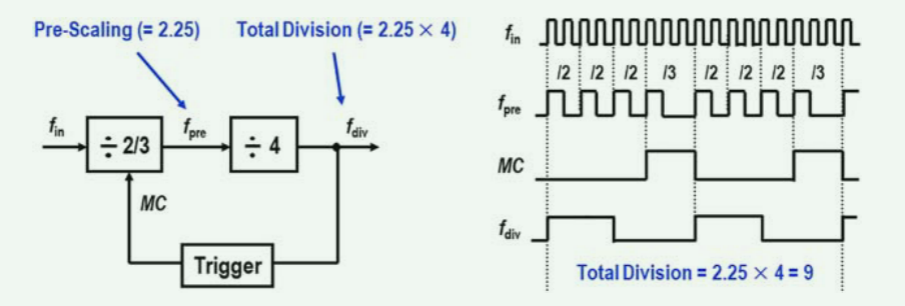

如图,使用2/3预分频器和4分频分频器(DIV4)设计9分频分频器。

- 9的分频比是2.25的预分频系数与4的乘积的乘积,即9=2.25×4。

- 2/3的预分频器每四个时钟周期3个二分频,1个三分频,有效分频比

。

- 2/3预分频器的模数控制(MC)信号来自触发电路,该触发电路由DIV4电路启用。

注意,DIV9电路的输出时钟f0总是具有恒定的时钟周期,因为在2/3预分频器的输出fpre处产生的分数时钟周期乘以具有反比的后续除法器。

如果用可编程计数器和可编程触发电路分别取代固定的4分频电路和触发电路,则可以实现各种分频值。

1.2 为什么预分配实现低功耗

为什么具有反馈的基于预分频器的计数器比一般的可编程计数器实现更低的功耗?

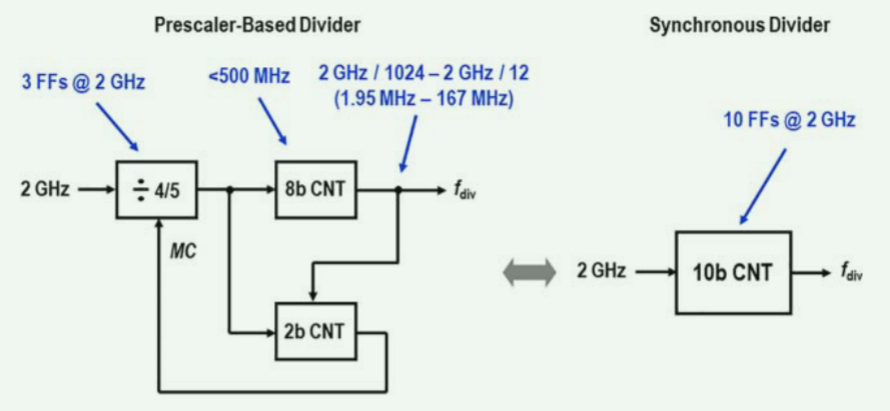

- 基于预分频器的计数器由一个4/5预分频器

- 一个8位计数器

- 一个2位计数器组成,

- 在2 GHz下执行10位可编程分频

8位主计数器在4/5预分频器之后提供各种分频比,2位辅助计数器为4/5预分频器产生MC信号。

在这种拓扑结构中,只有三个D型触发器(DFF)工作在2GHz,另外两个同步计数器工作在<500 MHz。

如果使用10位同步计数器,则至少10个DFF必须以2GHz工作,从而消耗巨大的功率。

基于预分频器的计数器还具有降低开关噪声的优点。

由于4/5预分频器仅需要三个DFF,可考虑将带偏置电流的电流模式逻辑(CML)电路用于DFF,以避免轨到轨摆幅,从而最大限度地降低VCO的反冲噪声。

在实践中,4/5预分频器不能离VCO太远,以最大限度地降低布局中金属连接造成的寄生电容。

两个8位和4位低频同步计数器可采用标准CMOS逻辑实现,并远离VCO放置。

example 具有多个预分频器的固定分频

预分配有助于节能。

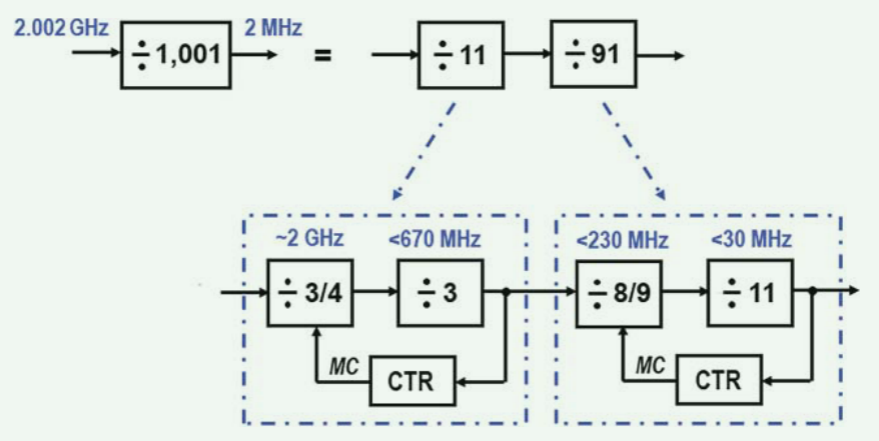

- 一个2 GHz分频器,分频比固定为1001

- 由于1,001是11乘以91,

- 首先使用两个分频器,其固定分频比为11和91

- 11分频器被设计为具有3/4预分频器,其周期性序列{3,4,4,3,4,4,.}的3分频器

- 3/4预分频器产生11/3的平均分频比,

- 随后的3分频器产生11分频输出时钟。

- 对于基于预分频器的分频器拓扑,只有三个DFF工作在2 GHz,

- 3分频分频器工作在<670 MHz

- 91分频分频器可以用一个8/9预分频器和一个11分频器实现:91 = 8×8+3× 9。

- 8/9预分频器将在每11个时钟周期

- 8个8分频

- 3个9分频。

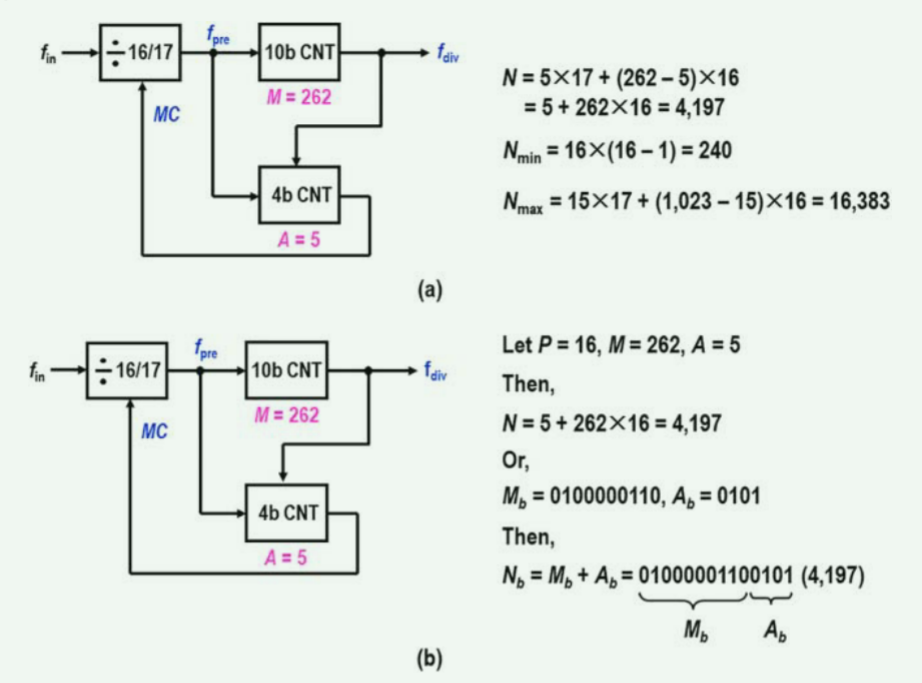

2. 基于预分频器的分频器的标准配置

基于预分频器的分频器不仅可以降低功耗,还可以提供灵活的编程。

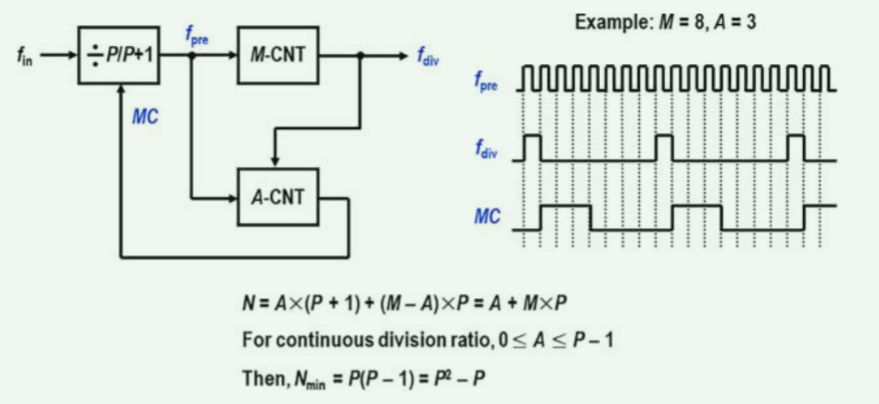

| P/(P+ 1)预分频器 | MC = 1:(P + 1)分频 MC = 0:(P)分频 |

| 主计数器(M-CNT) | M个时钟周期后复位MC信号 (M-A)个时钟周期P分频 |

| 辅助计数器(A-CNT) | MC信号在A个时钟周期内设置为逻辑高 A个时钟周期(P+ 1)分频 |

总分频比:

例如:4/5分频,M=8;A=3 ,则总分频比:

2.1 注意事项

使用基于预分频器的分频器的一个注意事项是,如果编程的分频比小于某个值,则不能保证分频比的连续集合。用于连续编程的最小分频比Nmin:

使用4/5预分频器将最小分频比设置为12,(3*4=12)

使用16/17预分频器将最小分频比设置为240(16*15=240)

- P值必须是2的幂。可以使用8/9预分频器,但不能使用7/8预分频器。

- A-CNT中的最大位数必须与

相同。如果使用8/9预分频器,则必须使用3位A-CNT。

- 总分频比不能小于

2.2 例子

3. 双模分频器的工作原理

DMD的工作原理基于脉冲吞咽法。

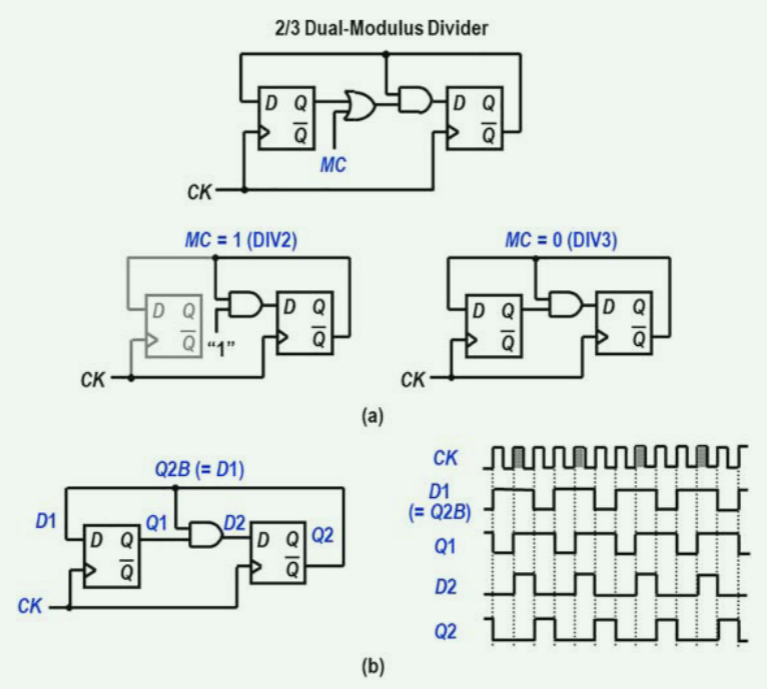

3.1 2/3分频

2/3 DMD的逻辑框图,

- 两个DFF

- 一个与门

- 一个或门组成

当MC被设置为高,

- 或门的输出将为高,而不管第一DFF的输出。

- 然后,与门的输出与第二DFF的互补输出的输出相同。

- 整个块变成一个反转触发器(TFF),并作为2分频电路工作。

当MC被设置为逻辑低时,

- 或门的输出取决于第一DFF Q1的输出

- 与2分频模式相比,在两个DFF的中间,一个输入脉冲被Q1和D1的AND门去除(或吞噬)。

- 在TFF的输入端少掉一个脉冲的情况下,TFF的输出周期变为输入周期的三倍。

这种吞脉冲技术通常用于高速DMD的设计,它比标准的同步计数方法更省电

- 2/3 DMD本身具有最少数量的逻辑门和DFF,

- 当在标准分频器的设计中用作预分频器时,它会受到严格的MC时序控制。

- 当2/3DMD用作预分频器时,MC信号不是静态的,

- 更新的MC信号必须在输入时钟的两个周期内到达。

如果1 GHz 2/3预分频器设计有主计数器和辅助计数器,则更新的MC信号必须在2 ns(1GHz的一个周期是1ns)内到达,以保证预分频器用于动态模量控制的正确功能。

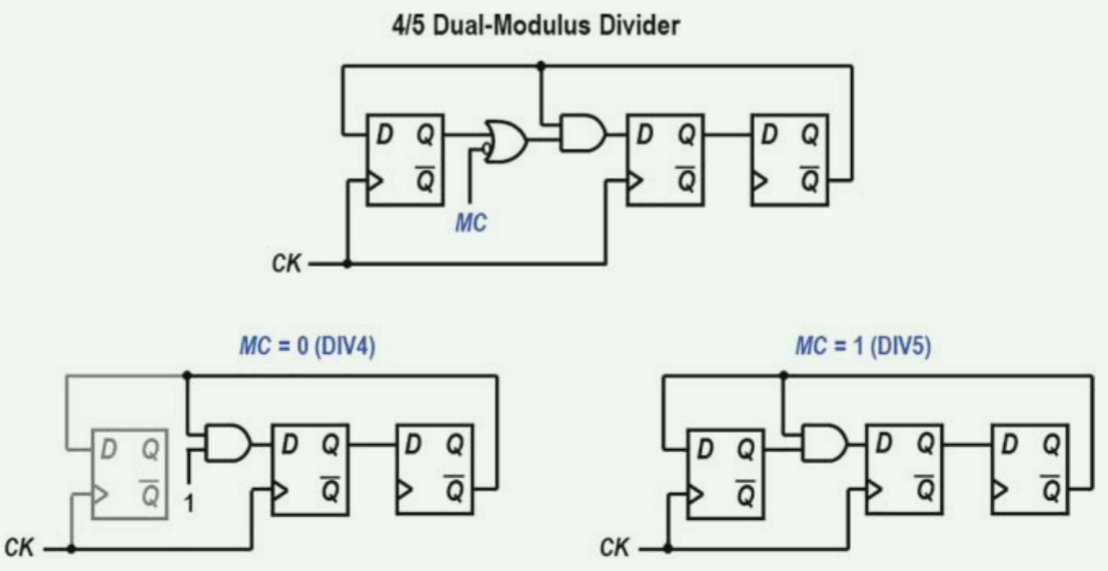

3.2 4/5 分频

在实际的标准分频器的设计中采用4/5预分频器或更高分频比的预分频器。

一个4/5 DMD的逻辑框图

- 三个DFF

- 一个AND门

- 一个OR门组成。

对于4的分频比,DMD基于级联的TFF的分频器,从而执行4分频功能。在5分频功能的情况下,脉冲吞除技术与几个控制逻辑门一起使用。

显然,4/5DMD将比2/3DMD消耗更多的功率,但是MC定时从输入时钟的两个周期放宽到四个周期。

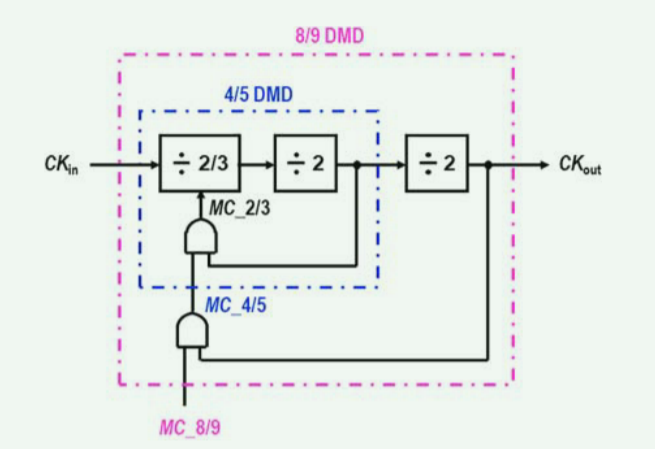

3.3 8/9分频器嵌套预分频(8/9嵌套4/5嵌套2/3)

4/5 DMD或更高分频比的DMD也可以通过广泛使用预分频器和逻辑门来实现,以减少同步DFF的数量。

- 使用2/3预分频器来设计4/5 DMD。

- 4/5 DMD可以通过2/3预分频器和TFF的级联配置来实现。

- 对于4分频比,4/5 DMD的MC输入(图中用MC_4/5表示)被设置为低电平,因此AND输出始终为低电平。

- 然后,2/3预分频器变成2分频电路,在随后的2分频电路之后产生4的分频比。

- 对于5的分频比,MC_4/5被设置为高,具有由第二级2分频电路的输出确定的AND输出MC_2/3。2/3预分频器以相等的占空比执行2分频和3分频功能,从而实现2.5的有效分频比。

- 下面的二分频电路产生一个输出时钟,其周期等于输入时钟的五个周期。

4/5 DMD是通过使用2/3预分频器、TFF和一个与门来实现的。

可以通过使用4/5DMD、TFF和与门来设计8/9DMD。

通常使用4/5 DMD设计,有三个DFF和控制逻辑电路,

而不是使用2/3预分频器,因为2/3分频的MC控制的时序裕度很小。

3.4 例子:多模分频器的设计

脉冲吞除方法的工作原理是跳过输入时钟的一个周期。

可以通过附加的控制逻辑跳过一个以上的时钟周期。例如,通过吞入两个时钟周期,分频比可以扩展2。

因此,可以用吞脉冲的方法来构造多模分频器。

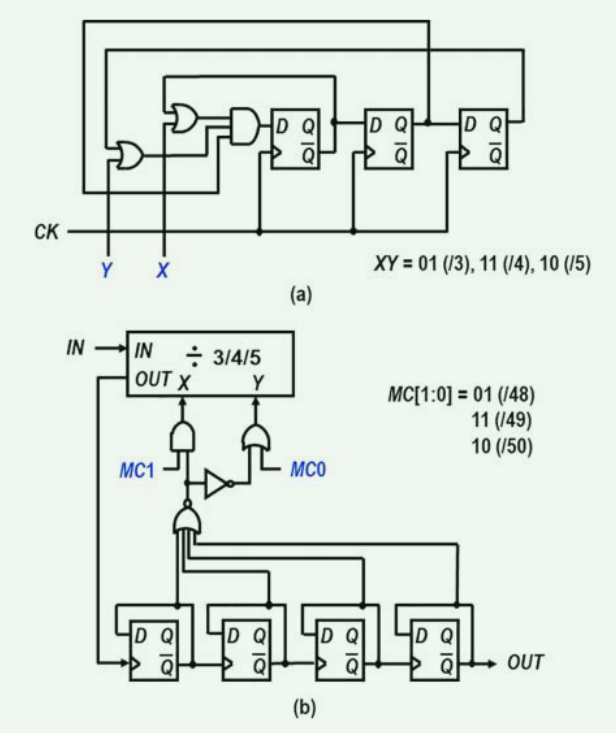

图(a)显示了3/4/5模数除法器的框图。5分频功能是通过跳过两个输入时钟周期来实现的,而4分频是通过跳过一个时钟来实现的。

如图(b)所示,3/4/5分频器被用作预分频器,构成一个具有2位模控制字的48/49/50模分频器。

- 这种多模分频器在设计特定分频范围的定制分频器时很有用,但很少用作标准配置。

- 注意,多模分频器也可以通过具有动态控制字的基于标准预分频器的分频器来实现。

- 当考虑特定分频范围时,定制架构可能有助于实现最佳功率和速度性能。

3573

3573

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?