1. 带串行链路的有线收发器

概述

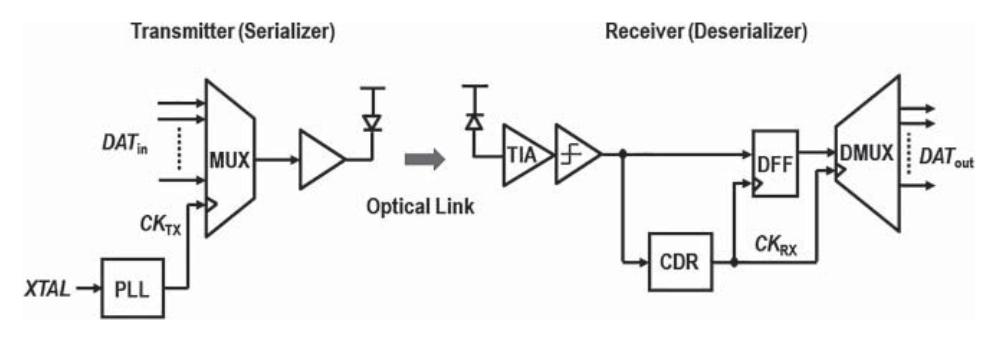

- 发射机将多个低速数据并行组合,形成调制激光器的高速串行数据

- 并行数据到串行数据的转换由具有与串行数据相同频率时钟的多路复用器完成

- 调制激光器通过光缆发射光,以利用开关键控(OOK)调制来表示数据“1”或“0”

- 接收器中的光电二极管将接收到的光转换为电流

- 利用跨阻放大器(TIA)和限幅放大器,获得正确的串行数据并将其馈送到数据限幅器

- 复用器(DMUX)将DFF的串行输出转换为多个用户的低速并行数据

将低速并行数据转换为串行数据,然后再将其转换为并行数据,称为SerDes(串行器和并行器)系统。

随着数据速率的增加,低抖动时钟生成和良好的同步是相当具有挑战性的。

光链路

- NRZ数据具有RZ数据的最小脉冲宽度的两倍

- 所以NRZ数据的带宽是RZ数据的一半

- NRZ数据主要用于大多数通信系统

- NRZ数据不包含时钟信息

- 在光通信中,通过光缆只发送数据而不发送时钟

- 接收端必须从接收到的NRZ数据中提取时钟信息,以实现DFF和DMUX的相位和频率同步

- CDR系统需要从有噪声的NRZ数据中提取时钟信息,并用提取的时钟对数据进行重新定时

电链路

- 与光链路相比,电链路可以很容易地提供多条线路来并行发送低速数据

- 我们更喜欢使用单个串行链路,但代价是产生高频时钟

- 当高速数据并行发送时,线路之间的串扰变得很大。

- 在高速下同步多个数据以执行适当的解复用是困难的

- 串行链路通信被认为是可靠的,即使具有低抖动高速时钟生成的必要要求

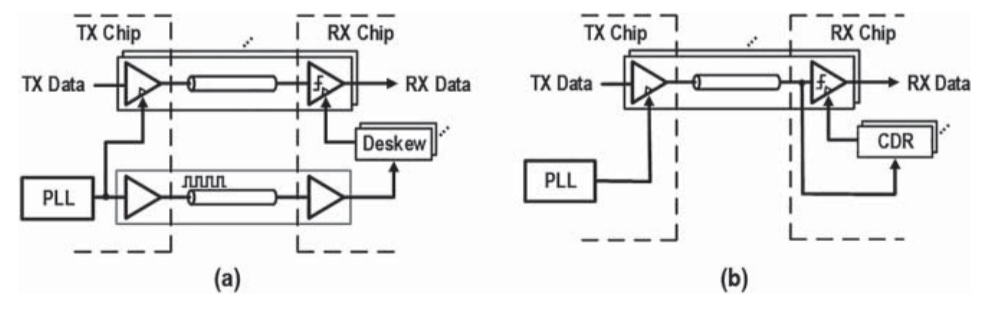

(b) clock-embedded data transmission.

- 在时钟转发传输中,我们同时发送NRZ数据和时钟。

- 由于接收机不需要从NRZ数据恢复时钟,因此可以直接利用接收的时钟和可变延迟电路来进行数据重定时

- 缺点是:需要额外的链路用于带宽是NRZ数据带宽两倍的时钟

- 时钟嵌入式系统,仅发送NRZ数据

- 时钟需要从NRZ数据中恢复

2. 锁相环实现时钟恢复和数据重定时

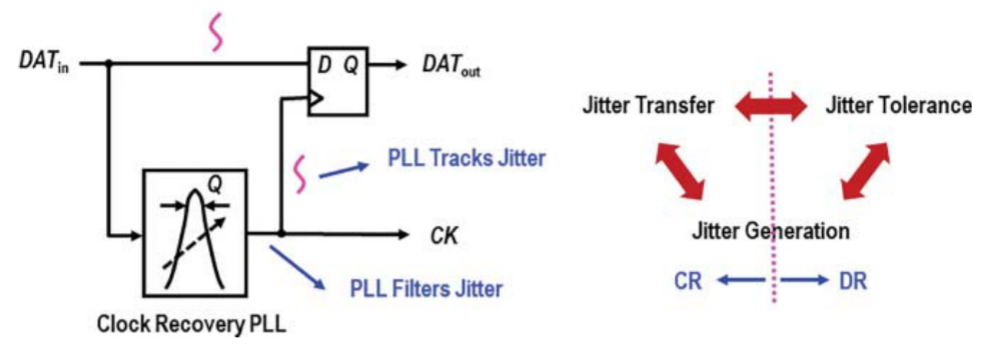

由于基于PLL的CDR采用高速非周期NRZ数据作为输入,因此设计高速高性能鉴相器非常重要。

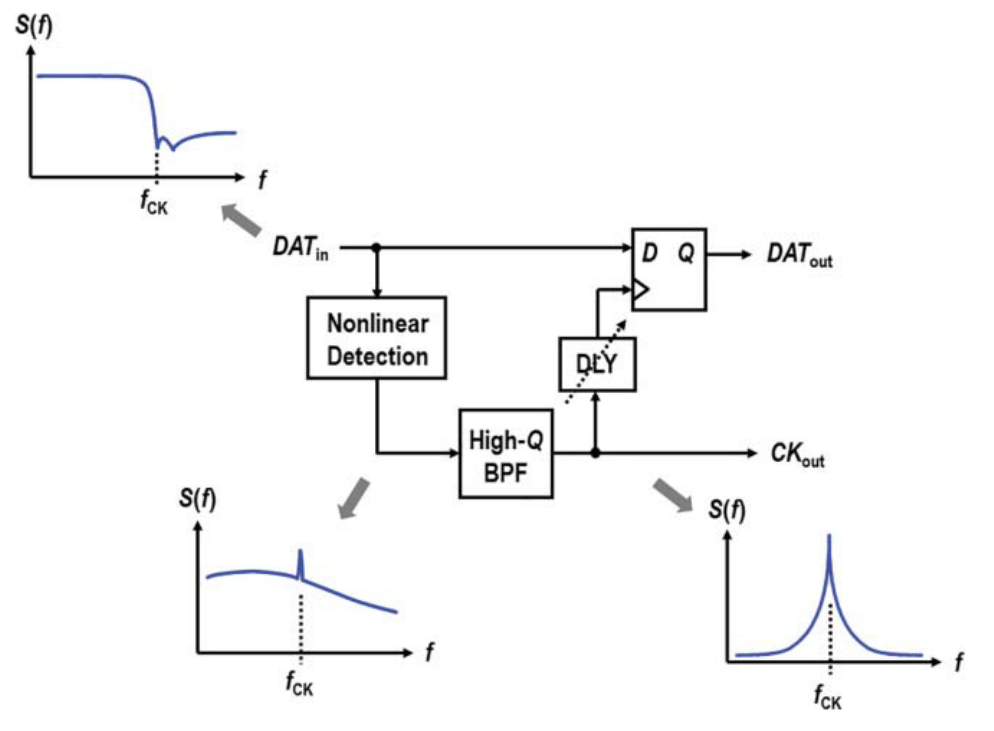

- NRZ数据不包含时钟信息,所以通过使用非线性检测电路从NRZ数据提取时钟信息

- 通过非线性电路恢复的时钟可能非常微弱

- 因此使用高Q带通滤波器通过抑制不需要的宽带噪声来提高时钟功率

这种传统的CDR系统存在以下困难:

- 需要一个外部高Q值带通滤波器

- 高Q带通滤波器的频率可调谐性有限,因为在品质因数和可调谐性之间存在基本的折衷

- 由于输入数据和恢复的时钟之间的相位偏移不能被很好地控制,所以我们需要用于数据重定时的移相器

- 由于CDR电路采用外部滤波器和独立的移相器,难以实现低功耗或高速性能

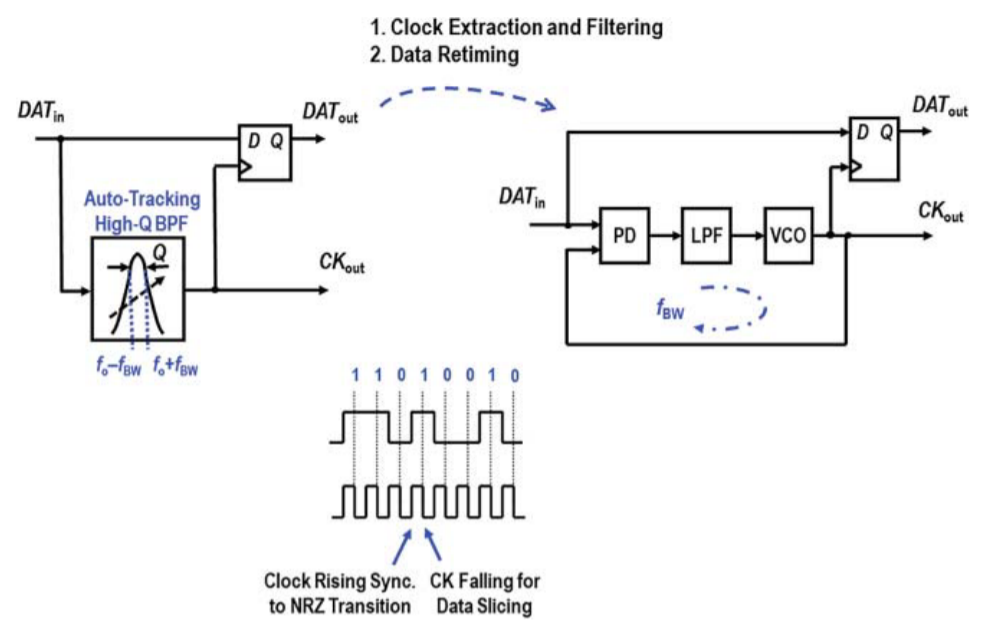

PLL对频域中的输入信号起到带通滤波器的作用(或对相域中的输入相位起到低通滤波器的作用)

- PLL带宽可以独立于输出频率设置,可以实现非常高Q值的带通滤波器

- 输出频率1GHz,带宽1MHz的PLL

- 品质因数(1GHz/2MHz)=500

- 如果环路带宽为100kHz

- 品质因数(1GHz/200kHz)=5000

- 更重要的是,这种高Q值带通滤波器的可调谐性主要由VCO的调谐范围决定,通常大于20%

- 除了自动跟踪高Q滤波功能外,PLL还提供NRZ数据跳变与时钟上升沿或下降沿之间的相位同步

基于PLL的CDR的主要功能:

- 自动跟踪高Q带通滤波器

- 从NRZ数据恢复时钟

- 具有自动相位跟踪功能的数据重定时

CDR PLL需要最佳带宽以获得最佳性能

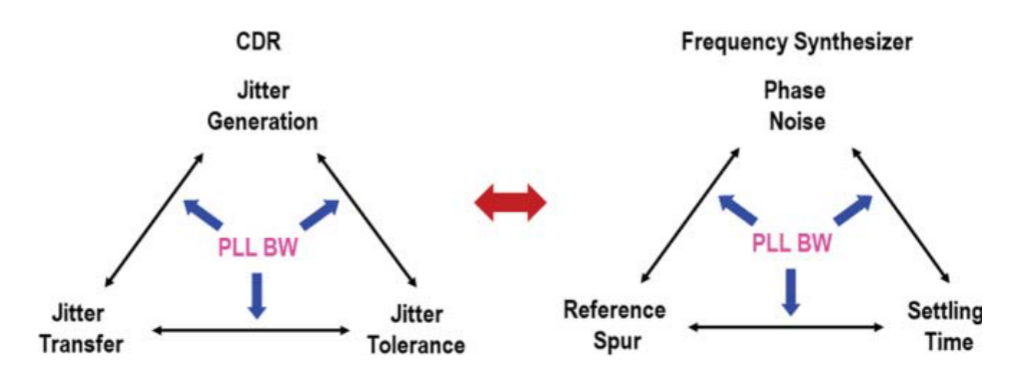

在CDRPLL的设计中,主要考虑了三个关键参数:抖动产生、抖动传输和抖动容忍

2.1 抖动产生

- 抖动产生表示当注入无噪声输入数据时,PLL输出端产生的抖动量

- 与频率合成器的情况类似,通过考虑PLL中的不同噪声源,获得最佳带宽非常重要

- 由于CDR PLL不具有分频器,因此不存在由于倍频而导致的相位噪声劣化。

- 高频相位检测器的带内噪声贡献比VCO的带内噪声贡献小,

- 大多数情况下需要宽带宽来抑制VCO的相位噪声

- 对于有噪声的输入数据,选择最佳带宽还取决于其他两个参数:抖动传输和抖动容限。

2.2 抖动传输

- 抖动传输指示输入数据的多少抖动被CDR电路滤波,其基本上由PLL的系统传递函数确定。

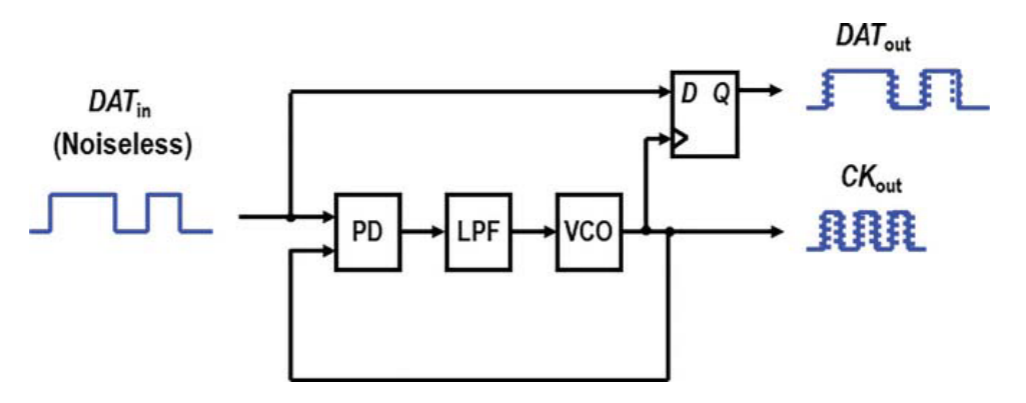

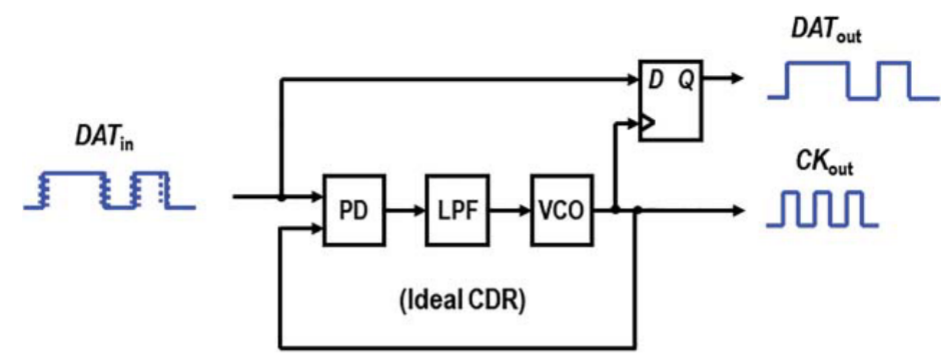

- 图为理想CDR PLL的概念图,该PLL可在极窄带宽内完全滤除输入抖动。

- 当输出数据用干净的时钟重新定时时,输入抖动在输出数据处被完全抑制。

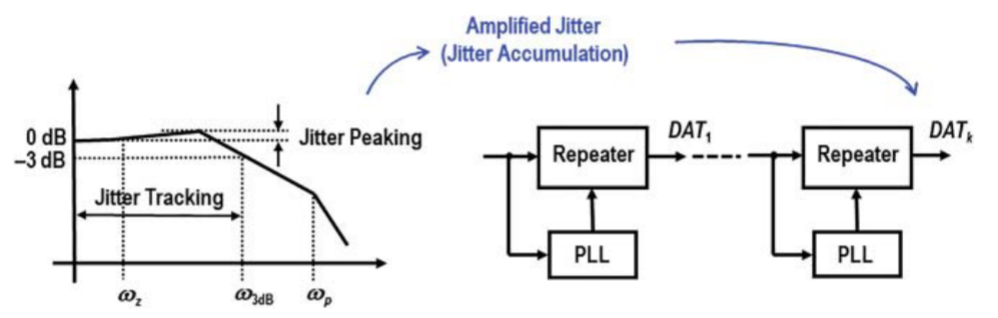

- 基于2型PLL的CDR系统在抖动传递函数中始终表现出接近3 dB带宽的增益峰值,因为稳定性需要系统零点。

- 在某些采用级联CDR电路的应用中,抖动传递函数中的增益峰值可能是一个问题。它会放大PLL带宽附近的抖动,导致CDR中继器出现抖动累积问题

- 对于同步光网络(SONET),其中单个时钟处理具有中继器的整个网络上的数据重定时,这种抖动峰值应该被严格控制为小于0.1dB。

- 因此,必须考虑过阻尼的PLL。

- 当使用级联CDR PLL时,一些电链路还需要在抖动传递函数中进行严格的抖动峰值控制,以过滤输入抖动。

2.3 抖动容限

抖动容限显示CDR PLL的相位跟踪能力,表明数据重定时的质量,以最大限度地降低误码率。

- 如图所示,如果PLL可以完全跟踪输入数据的相位边沿,

- 则DFF时钟的相位边沿始终与数据的相位边沿同步,

- DFF用恢复的时钟对输入数据重新定时时不会出错。

- 如果数据抖动的频率分量在环路带宽内,

- 则输入数据的相位变化可以由恢复的时钟跟踪,使得输入抖动对于数据重定时是可容忍的。

- 抖动容限的频率响应显示PLL的高通滤波器特性

- 因此,锁相环需要很宽的带宽来跟踪相位边沿的快速变化。

- 抖动容限遵循PLL的误差传递函数,具有与系统传递函数相同的3 dB转折频率

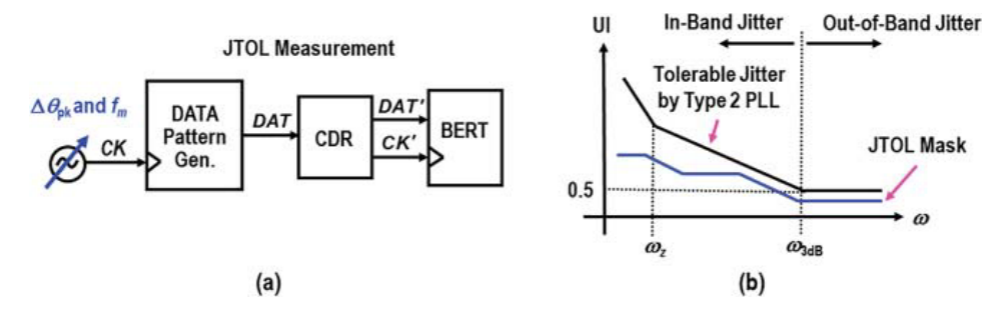

在大多数收发器系统中,数据跟踪的最低要求用频率响应图来指定,即抖动容限掩模(jitter tolerance mask)

(b) JTOL mask

- 峰值相位偏差【

】,由调制指数【m】给出

- 调制指数【m】,是峰值频率偏差【

】与调制频率【

】的比值

- 通过测量频域中时钟的杂散水平,可以获得给定【

】的【

】

- 具有针对给定fm的可变【

】的相位调制时钟被用于数据模式生成器以生成相位调制数据

- 对于给定的fm,记录满足误码率(BER)要求的最大

- BER性能的测量可以通过BER测试仪(BERT)完成,其中使用CDR电路的输出数据和时钟。

- 上图(b),2型PLL抖动容限性能沿着抖动容限掩码

- 由于抖动容限由PLL的开环增益决定

- 因此它给出的曲线与开环增益曲线相同,

- 相位容限由单位间隔(UI)表示,即一个时钟周期

CDR PLL在CDR带宽内具有良好的抖动容限,而在带宽外不显示抖动跟踪。

实际上,通过假设所有其他抖动分量对时钟周期的贡献小于50%,将0.5 UI设置为抖动容限的最小值。

抖动容限掩码意味着输入数据的长期抖动是可容忍的,因为类型2 PLL的高通滤波器特性,而短期抖动是关键的。

2.4 带宽作用 & CDR与频率综合器比较

- 【抖动传输】:需要窄带宽的抖动传输,以恢复从噪声数据的时钟

- 【抖动容限】:需要宽的带宽,以执行具有最小BER的数据重定时

- 【抖动产生】:需要考虑每个电路的噪声贡献来获得最佳带宽

CDR PLL的三个系统参数的带宽要求与频率合成器的三个系统参数的带宽要求相当。

| CDR | 频率合成器 |

| 抖动产生 | 相位噪声 |

| 抖动传输 | 参考杂散 |

| 抖动容限 | 建立时间 |

228

228

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?