《A 14nm Analog Sampling Fractional-N PLL with a Digital-to-Time Converter Range-Reduction Technique Achieving 80fs Integrated Jitter and 93fs at Near-Integer Channels》

1. 引言

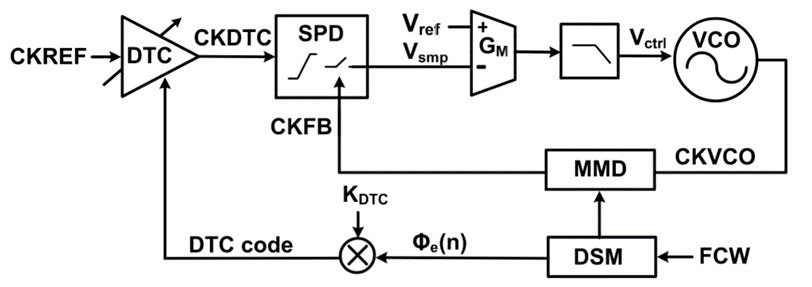

1.1 模拟分数采样锁相环优势

- 高增益、线性、与BBPD相比定义明确

- MMD --》VCO更好的隔离度,与SSPD相比简化了SPD

- 没有高分辨率的TDC;不需要DCO

DTC消除DSM累积的量化噪声

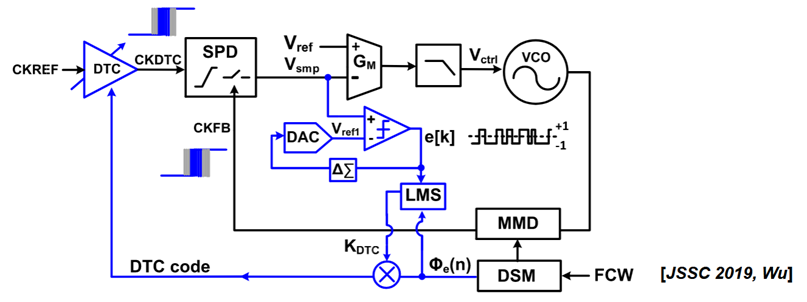

1.2 DTC增益校准

- e[k]通过LMS,控制DTC延时,消除量化奥斯

- 调整Vref1,消除DC偏移

1.3高性能分数SPLL挑战

- 高出纯度参考时钟,低VCO相噪

- 低抖动、高精度 DTC

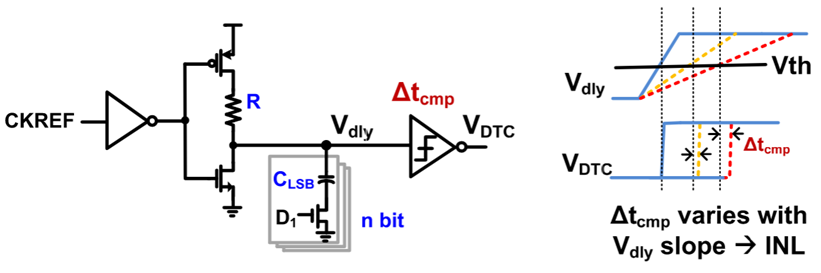

- 线性DTC:非线性造成分数杂散、噪声折叠

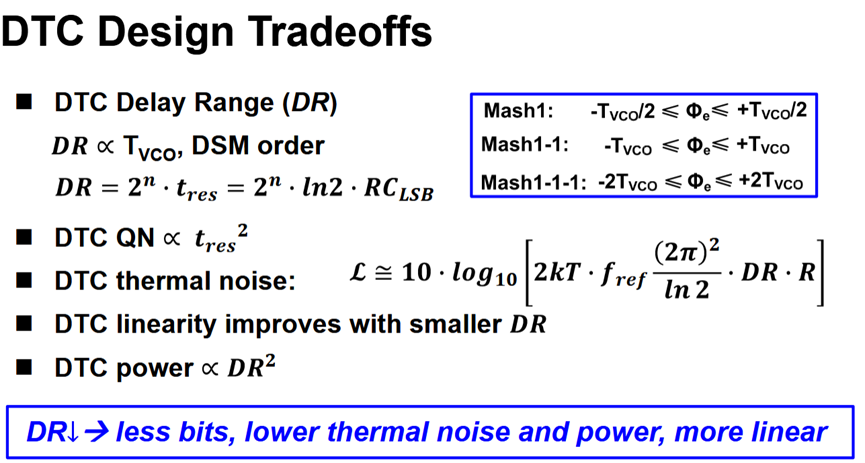

1.4 DTC设计权衡

2. 创新点

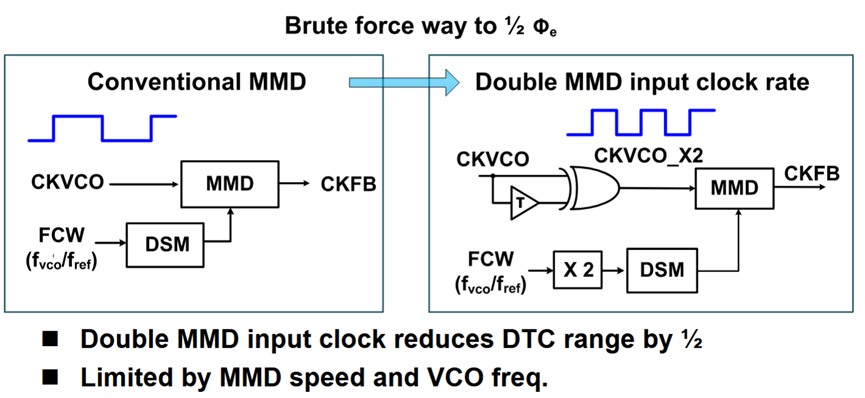

2.1 DTC范围缩小技术 ( 提高MMD时钟频率,减小DTC范围 )

2.2 可转换双核VCO

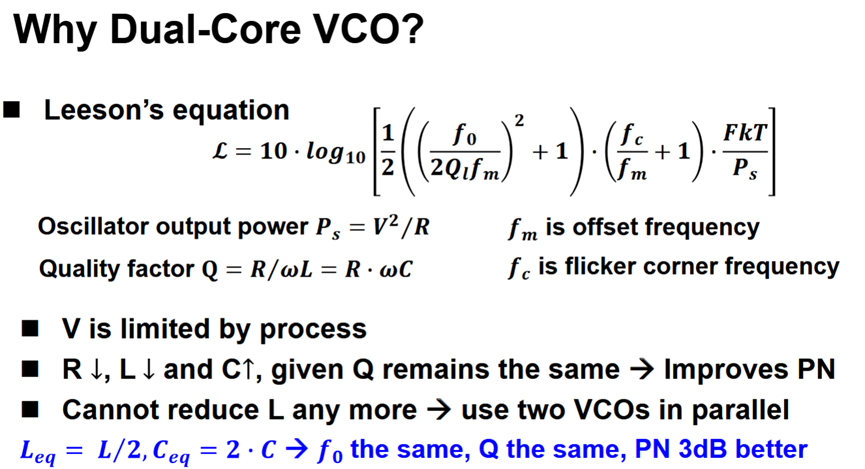

不能再减小L --> 使用两个VCO并列

参考文献

W. Wu et al., "32.2 A 14nm Analog Sampling Fractional-N PLL with a Digital-to-Time Converter Range-Reduction Technique Achieving 80fs Integrated Jitter and 93fs at Near-Integer Channels," 2021 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 2021, pp. 444-446, doi: 10.1109/ISSCC42613.2021.9365850.

1960

1960

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?