本次参考教程来自野火FPGA书籍

在本次工程中,重点是在分频的同时将分频得到的时钟信号挂在全局时钟树上,因此本次只能使用flag标志信号进行标志分频点

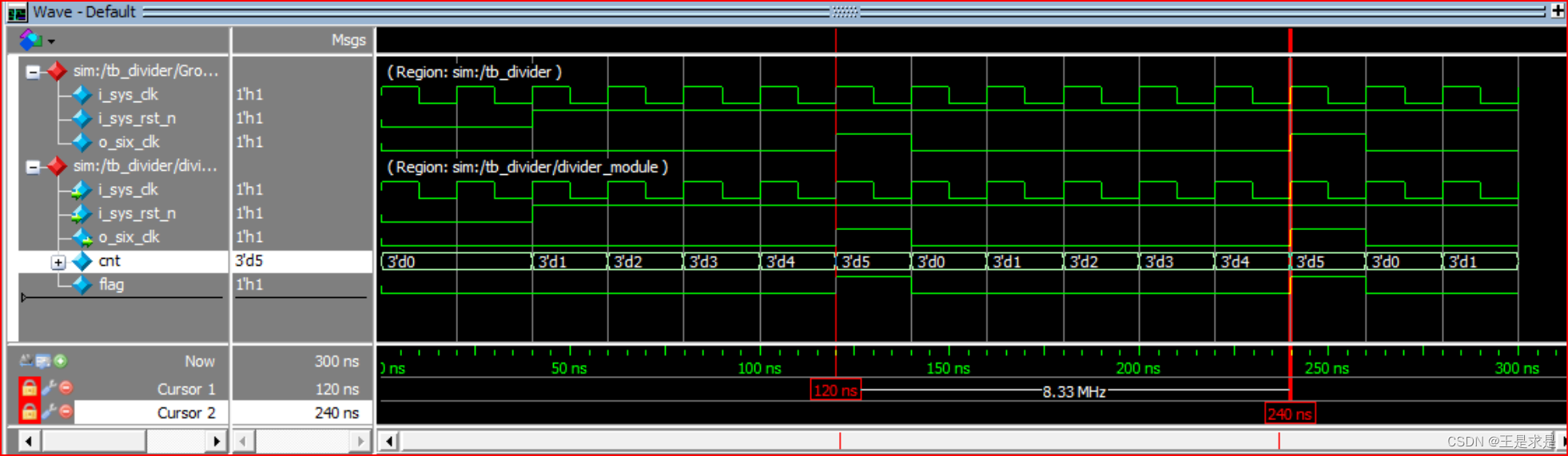

偶分频(6分频)

1.这里需要一个计数器,实现计数,因此需要确定计数的最大值

2.因为是六分频,且每次都是(上边沿检测)检测一个周期,因此可由只需要检测012345便可以开始分频了

代码如下:

module divider

#(

parameter CNT_MAX = 5

)

(

input i_sys_clk ,

input i_sys_rst_n ,

output o_six_clk

);

reg[2:0] cnt ;

reg flag ;

assign o_six_clk = flag;

always@(posedge i_sys_clk or negedge i_sys_rst_n)

if(!i_sys_rst_n)

cnt <= 3'd0;

else if(cnt == CNT_MAX)

cnt <= 3'd0;

else

cnt <= cnt + 1'b1;

always@(posedge i_sys_clk or negedge i_sys_rst_n)

if(!i_sys_rst_n)

flag <= 1'b0;

else if(cnt == CNT_MAX - 1)

flag <= 1'b1;

else

flag <= 1'b0;

endmodule

`timescale 1ns/1ns

module tb_divider();

reg i_sys_clk ;

reg i_sys_rst_n ;

wire o_six_clk ;

initial begin

i_sys_clk = 1'b1;

i_sys_rst_n = 1'b0;

#40

i_sys_rst_n = 1'b1;

end

always #10 i_sys_clk = !i_sys_clk;

divider

#(

.CNT_MAX(4)

)

divider_module

(

.i_sys_clk (i_sys_clk ),

.i_sys_rst_n(i_sys_rst_n),

.o_six_clk (o_six_clk )

);

endmodule 下面是偶分频,将参数改为5,即可

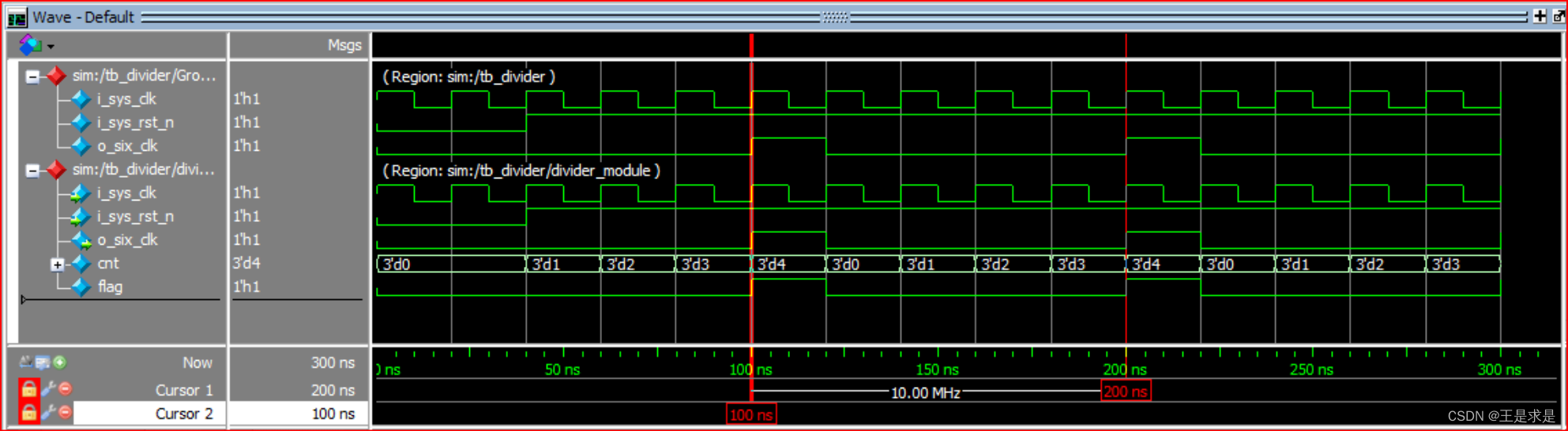

下面是奇分频,将参数改为4,即可

这个与黑金有一个很大的区别,就是不会延迟一拍,

因为要挂在全局时钟树上,所以无法将这个

2023.6.24买了一个黑金屏幕4.3寸正好搭配我的征途mini(前些天买的,还送了ov5640)这样东西都全了,可以开始准备搞图像处理了。一共花了490

//----------6.25更-------------//

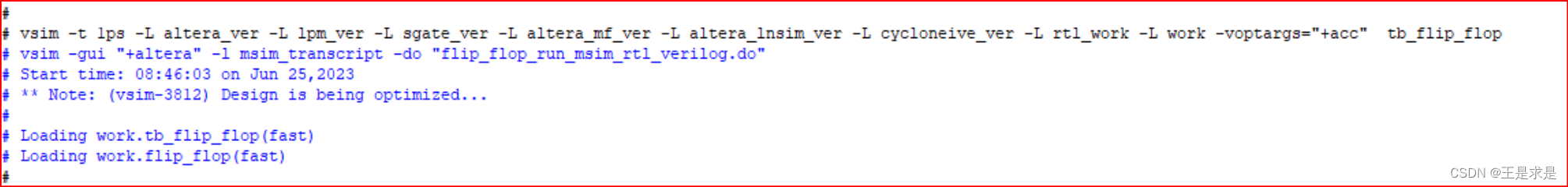

之所以没有延迟一拍是只因为在tb文件中只有系统时钟使用阻塞赋值,其他输入信号使用非阻塞赋值

通过按上下键,可以不用在重新打开modesim .然后找到do后enter

本文介绍了使用FPGA进行偶分频(6分频)的方法,通过设置计数器和flag标志来实现。代码示例展示了如何在不引入额外延迟的情况下将分频信号挂到全局时钟树上。此外,文章提到了黑金屏幕和OV5640传感器在图像处理系统的应用。

本文介绍了使用FPGA进行偶分频(6分频)的方法,通过设置计数器和flag标志来实现。代码示例展示了如何在不引入额外延迟的情况下将分频信号挂到全局时钟树上。此外,文章提到了黑金屏幕和OV5640传感器在图像处理系统的应用。

3093

3093

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?