1.目的:设计一个每50ms交替变换的输出端驱动LED灯的亮灭

2.原理

2.1输入信号:时钟clk,复位信号reset

2.2输出信号:LED控制led

2.3内部逻辑:

开发板晶振是50Mhz,故时钟周期为20ns。因而达到50ms需要计数25000000次,用25位的寄存器reg[24:0]存储当前计数值较为合适。因而,

一方面需要控制计数器的加减:即1:复位来时计数器清零;2:时钟来时:若计数器达到25000000-1,计数器清0;负责加1。

另一方面需要控制LED的输出:即1:复位来时LED输出置零;2:时钟来时:若计数器达到25000000-1,时钟翻转;否则不变

2.4注意:

1. 注意计数周期虽是25000000,但是计数本身有从MAX到0这一过程,故计数值需自减1才对。

2. 虽说一个always语句块就能完成,但为了规范性以及后续分析的合理性,不同的赋值块最好分开单独写。

3.源码

module cnt(

input clk,

input reset,

output reg led_test

);

//定义一个25位的寄存器用于计数

reg [24:0] cnt;

//f:50Mhz,则T:20ns.则500ms需要翻转25_000_0000次

//计数器控制过程

always @(posedge clk or posedge reset)

begin

if (reset)

cnt<=25'd0;

else if (cnt == 25'd250000000-25'd1)

cnt <=25'd0;

else

cnt <= cnt+25'd0;

end

//LED翻转过程

always @(posedge clk or posedge reset)

begin

if (reset)

led_test<=1'b0;

else if (cnt == 25'd250000000-25'd1)

led_test <= ~led_test;

else

led_test<=led_test;

end

endmodule

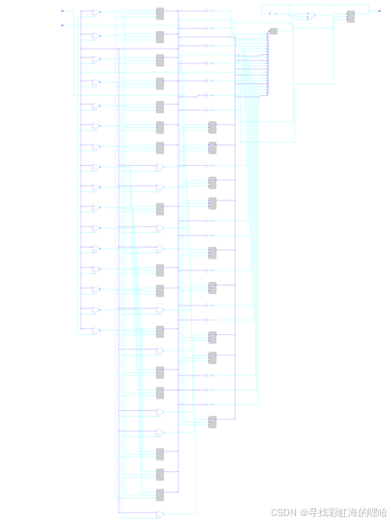

4.RTL描述与分析

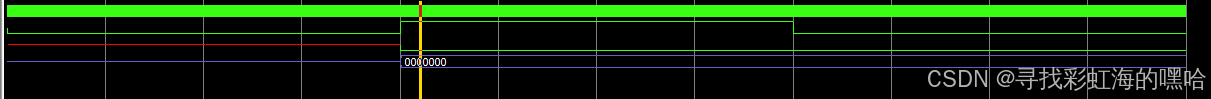

5.modersim仿真

5.1仿真内容

输入周期为50Mhz的时钟,并在开始的连续3个20ms翻转复位(共产生一个复位上升沿),观察led输出波形及计数器波形。(我这里时间设置的有点短,所以没能看到计数器计满去使LED翻转的过程)

5.2tb源码

`timescale 1ns/1ns

module cnt_tb;

reg clk;

reg reset;

wire led;

cnt cnt(

.clk(clk),

.reset(reset),

.led_test(led)

);

initial clk = 1;

always #10 clk= ~clk;

initial begin

reset = 1'b0;

#20000;

reset =1'b1;

#20000;

reset =1'b0;

#20000;

$stop;

end

endmodule

5.3仿真结果

6.板级测试

6.1时序约束

由于这个是时序逻辑电路,故需要对时钟信号进行时序约束

6.2IO约束

6.3测试结果

725

725

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?