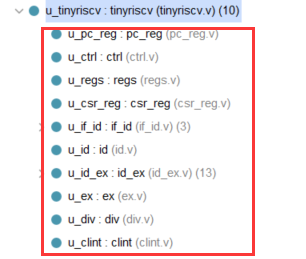

tinyriscv的实例化模块

这段代码实现的是一个 TinyRISC-V 处理器的核心设计。它将处理器核心、多个外设(如 定时器、UART、JTAG、GPIO、SPI、CSR、Interrupt Controller)通过 寄存器接口总线(RIB)连接在一起,形成一个完整的系统。

1. 处理器核心:tinyriscv

tinyriscv u_tinyriscv(

.clk(clk),

.rst(rst),

.rib_ex_addr_o(m0_addr_i),

.rib_ex_data_i(m0_data_o),

.rib_ex_data_o(m0_data_i),

.rib_ex_req_o(m0_req_i),

.rib_ex_we_o(m0_we_i),

.rib_pc_addr_o(m1_addr_i),

.rib_pc_data_i(m1_data_o),

.jtag_reg_addr_i(jtag_reg_addr_o),

.jtag_reg_data_i(jtag_reg_data_o),

.jtag_reg_we_i(jtag_reg_we_o),

.jtag_reg_data_o(jtag_reg_data_i),

.rib_hold_flag_i(rib_hold_flag_o),

.jtag_halt_flag_i(jtag_halt_req_o),

.jtag_reset_flag_i(jtag_reset_req_o),

.int_i(int_flag)

);

tinyriscv是一个 RISC-V 处理器的实例,处理指令执行、寄存器操作和数据流控制。该处理器通过总线接口和其他外设进行通信。- 它与多个外设(如 ROM、RAM、定时器、GPIO 等)和调试接口(如 JTAG)进行交互,接收外设的数据,发送操作指令,处理中断信号等。

- RIB 接口:

rib_ex_addr_o、rib_ex_data_o、rib_ex_data_i等信号用于与外设进行地址和数据交换,控制读写操作。

Register Interface Bus(寄存器接口总线)

2. 程序计数器(PC)寄存器:pc_reg

pc_reg u_pc_reg(

.clk(clk),

.rst(rst),

.jtag_reset_flag_i(jtag_reset_flag_i),

.pc_o(pc_pc_o),

.hold_flag_i(ctrl_hold_flag_o),

.jump_flag_i(ctrl_jump_flag_o),

.jump_addr_i(ctrl_jump_addr_o)

);

pc_reg:是一个程序计数器(PC)寄存器模块,负责存储当前正在执行的指令地址。- 它使用 时钟(

clk)和 复位信号(rst)进行同步控制。 - 跳转控制:如果

jump_flag_i为真,它会将程序计数器跳转到jump_addr_i地址。

3. 控制模块:ctrl

ctrl u_ctrl(

.rst(rst),

.jump_flag_i(ex_jump_flag_o),

.jump_addr_i(ex_jump_addr_o),

.hold_flag_ex_i(ex_hold_flag_o),

.hold_flag_rib_i(rib_hold_flag_i),

.hold_flag_o(ctrl_hold_flag_o),

.hold_flag_clint_i(clint_hold_flag_o),

.jump_flag_o(ctrl_jump_flag_o),

.jump_addr_o(ctrl_jump_addr_o),

.jtag_halt_flag_i(jtag_halt_flag_i)

);

ctrl:控制信号模块,主要用于处理 暂停 和 跳转 操作的控制。- 暂停信号:控制处理器是否暂停(

hold_flag)。 - 跳转信号:控制处理器是否跳转到新的指令地址(

jump_addr)。 - JTAG 调试:

jtag_halt_flag_i输入信号用于接收来自 JTAG 的停止指令。

- 暂停信号:控制处理器是否暂停(

4. 寄存器堆:regs

regs u_regs(

.clk(clk),

.rst(rst),

.we_i(ex_reg_we_o),

.waddr_i(ex_reg_waddr_o),

.wdata_i(ex_reg_wdata_o),

.raddr1_i(id_reg1_raddr_o),

.rdata1_o(regs_rdata1_o),

.raddr2_i(id_reg2_raddr_o),

.rdata2_o(regs_rdata2_o),

.jtag_we_i(jtag_reg_we_i),

.jtag_addr_i(jtag_reg_addr_i),

.jtag_data_i(jtag_reg_data_i),

.jtag_data_o(jtag_reg_data_o)

);

regs:是一个 寄存器堆(Register File),用于存储处理器的寄存器值(如x0到x31)。- 它支持 读 和 写 操作,通过信号

we_i、waddr_i和wdata_i来写入数据,通过raddr1_i、raddr2_i来读取数据。 - 还支持 JTAG 接口,允许通过调试接口来读取和写入寄存器。

- 它支持 读 和 写 操作,通过信号

5. 控制和状态寄存器(CSR):csr_reg

csr_reg u_csr_reg(

.clk(clk),

.rst(rst),

.we_i(ex_csr_we_o),

.raddr_i(id_csr_raddr_o),

.waddr_i(ex_csr_waddr_o),

.data_i(ex_csr_wdata_o),

.data_o(csr_data_o),

.global_int_en_o(csr_global_int_en_o),

.clint_we_i(clint_we_o),

.clint_raddr_i(clint_raddr_o),

.clint_waddr_i(clint_waddr_o),

.clint_data_i(clint_data_o),

.clint_data_o(csr_clint_data_o),

.clint_csr_mtvec(csr_clint_csr_mtvec),

.clint_csr_mepc(csr_clint_csr_mepc),

.clint_csr_mstatus(csr_clint_csr_mstatus)

);

csr_reg:用于管理 控制和状态寄存器(CSR),用于配置中断、控制处理器的状态等。- CSR 地址:如

csr_clint_csr_mtvec、csr_clint_csr_mepc等地址映射到不同的控制寄存器。 - 中断使能:

csr_global_int_en_o用于启用全局中断。

- CSR 地址:如

6. 流水线阶段:if_id, id, id_ex, ex 等

这些模块分别对应于流水线的不同阶段,用于处理指令的抓取(IF)、解码(ID)、执行(EX)等操作。

if_id:负责从指令存储器(如 ROM)中获取指令,并将其送到id阶段 进行解码。id:解码指令并读取相应的寄存器数据。id_ex:在ID阶段之后准备执行阶段所需的寄存器和数据。ex:执行阶段,执行算术、逻辑操作或内存访问。

7. 除法模块:div

div u_div(

.clk(clk),

.rst(rst),

.dividend_i(ex_div_dividend_o),

.divisor_i(ex_div_divisor_o),

.start_i(ex_div_start_o),

.op_i(ex_div_op_o),

.reg_waddr_i(ex_div_reg_waddr_o),

.result_o(div_result_o),

.ready_o(div_ready_o),

.busy_o(div_busy_o),

.reg_waddr_o(div_reg_waddr_o)

);

div:用于执行 除法 操作,接收被除数(dividend_i)、除数(divisor_i),并产生结果(result_o)。- 状态信号:如

ready_o表示除法是否完成,busy_o表示除法是否正在进行。

8. CLINT(定时器中断控制器)模块:clint

clint u_clint(

.clk(clk),

.rst(rst),

.int_flag_i(if_int_flag_o),

.inst_i(id_inst_o),

.inst_addr_i(id_inst_addr_o),

.jump_flag_i(ex_jump_flag_o),

.jump_addr_i(ex_jump_addr_o),

.hold_flag_i(ctrl_hold_flag_o),

.div_started_i(ex_div_start_o),

.data_i(csr_clint_data_o),

.csr_mtvec(csr_clint_csr_mtvec),

.csr_mepc(csr_clint_csr_mepc),

.csr_mstatus(csr_clint_csr_mstatus),

.we_o(clint_we_o),

.waddr_o(clint_waddr_o),

.raddr_o(clint_raddr_o),

.data_o(clint_data_o),

.hold_flag_o(clint_hold_flag_o),

.global_int_en_i(csr_global_int_en_o),

.int_addr_o(clint_int_addr_o),

.int_assert_o(clint_int_assert_o)

);

clint:用于管理 定时器中断控制器(CLINT),它用于中断处理、跳转控制以及全局中断使能。

总结:

这段代码实现了 TinyRISC-V 处理器的 SOC,包括处理器核心、外设(如定时器、UART、GPIO、SPI)和中断控制。外设通过寄存器接口总线(RIB)连接,与处理器进行数据交互。每个模块(如寄存器堆、控制寄存器、除法器、定时器)都有自己的任务,协同工作以完成处理任务。

1678

1678

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?