0、前言

参考资料:

《野火 Linux 基础与应用开发实战指南基于 i.MX6ULL 系列》PDF 第27章

https://www.gnu.org/software/make/manual

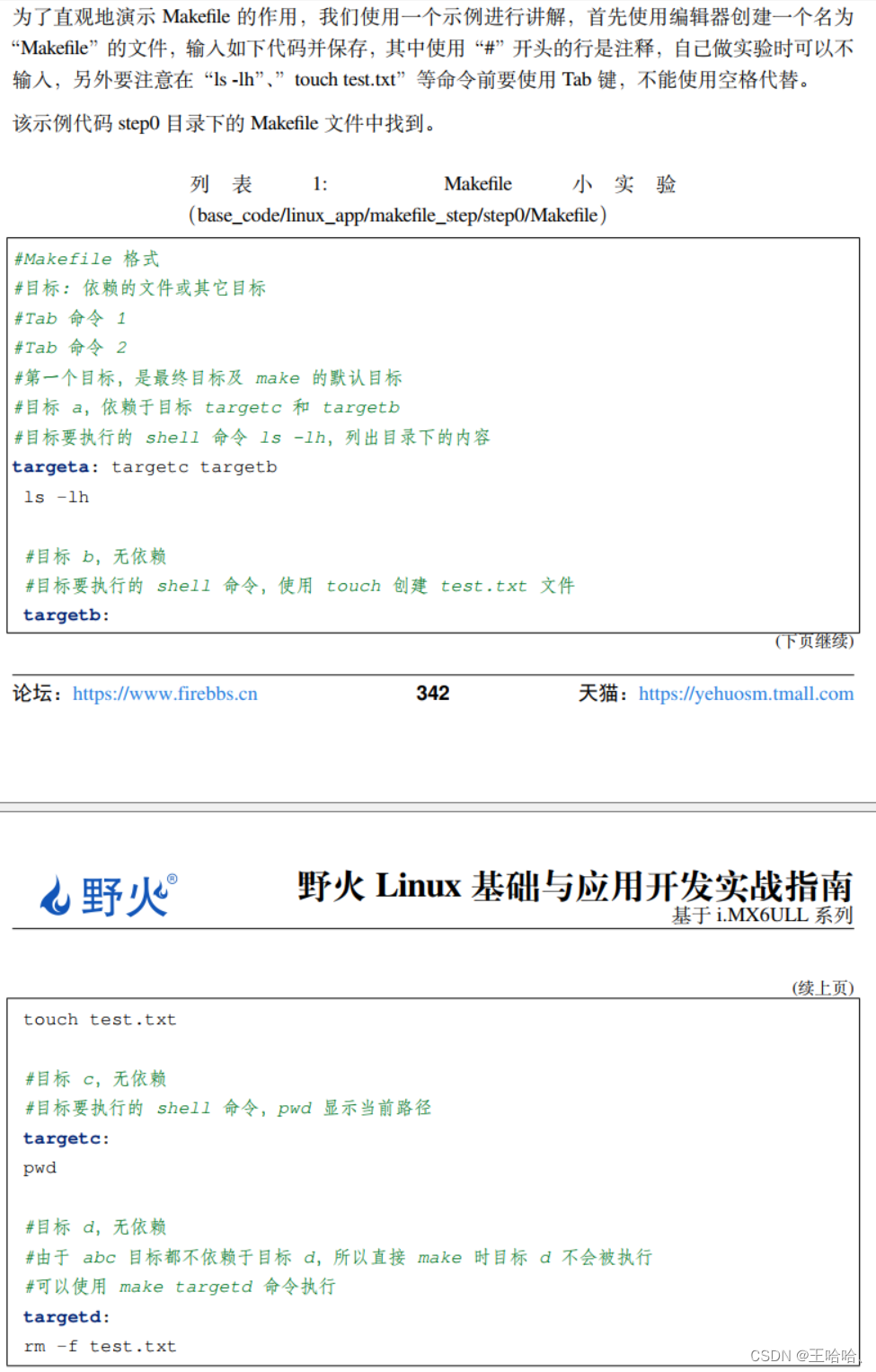

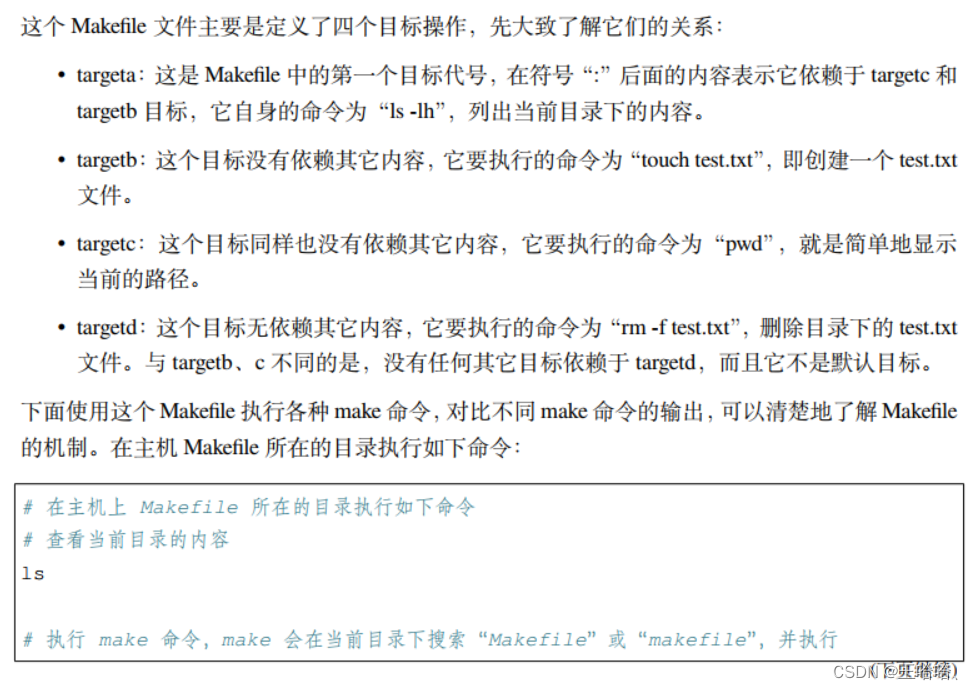

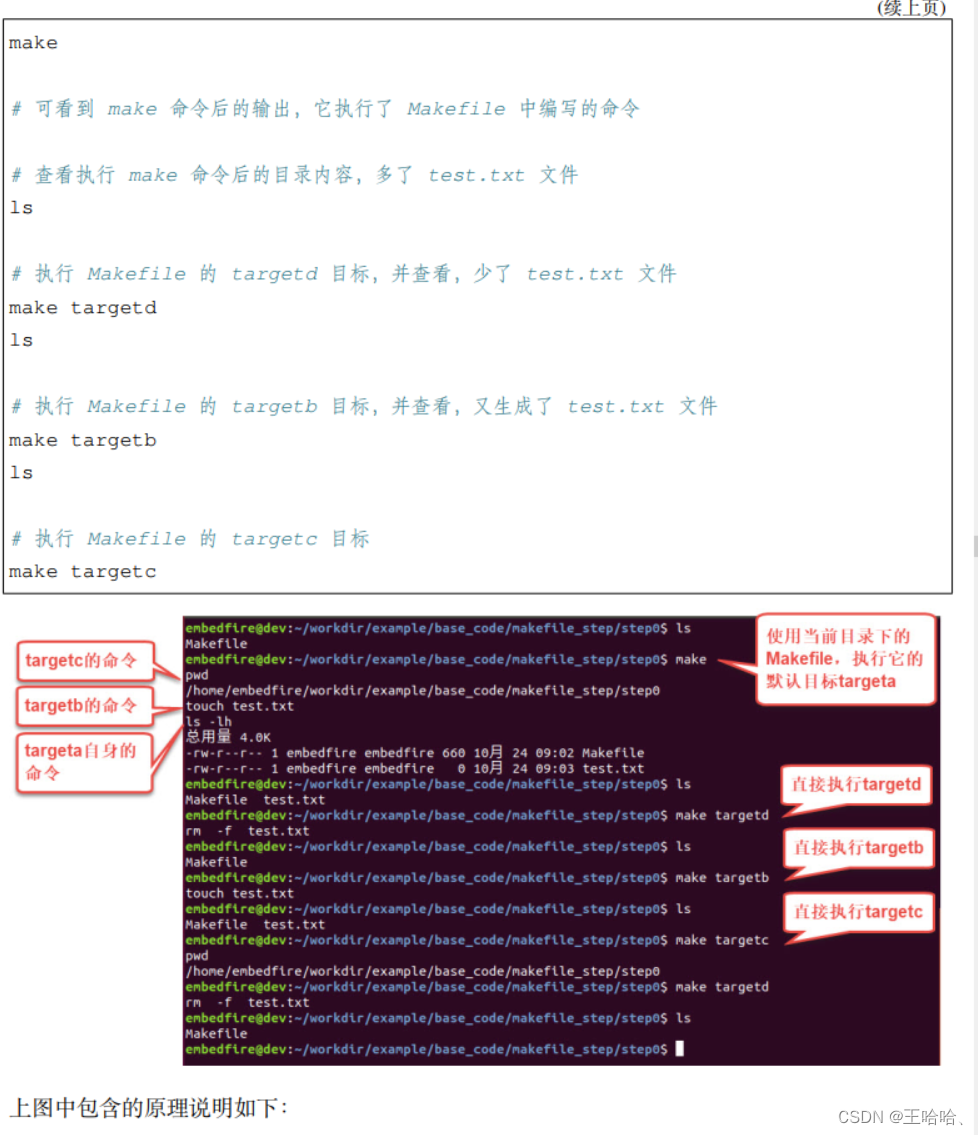

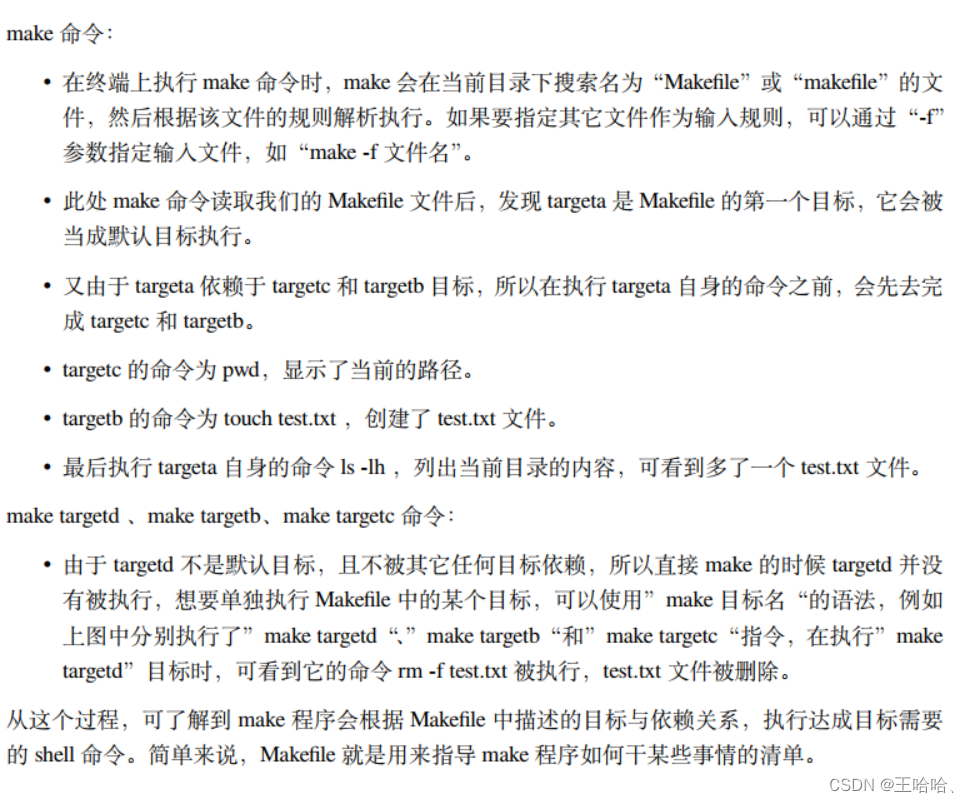

1、Makefile 小实验

2、使用 Makefile 编译程序

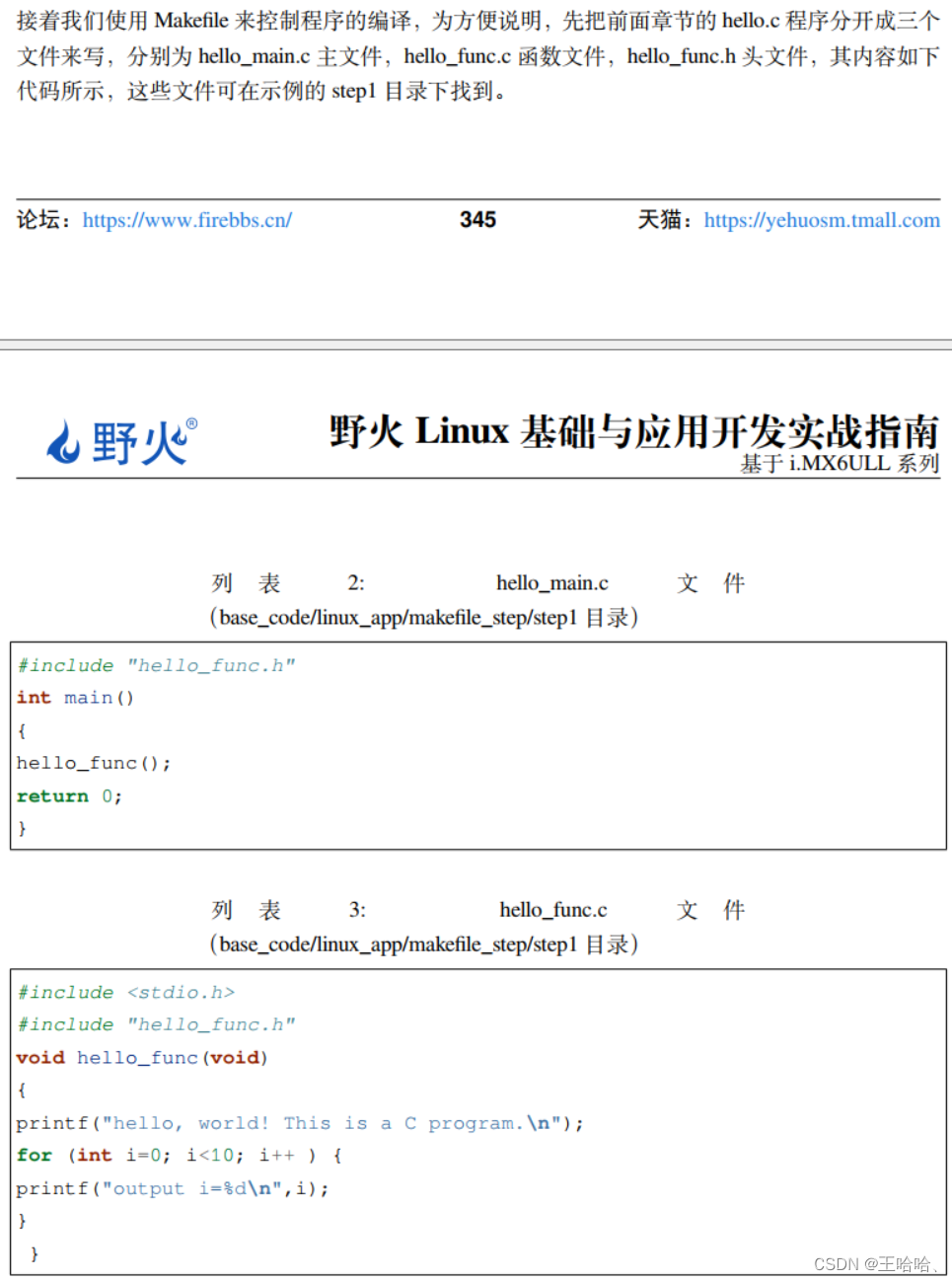

2.1 使用 GCC 编译多个文件

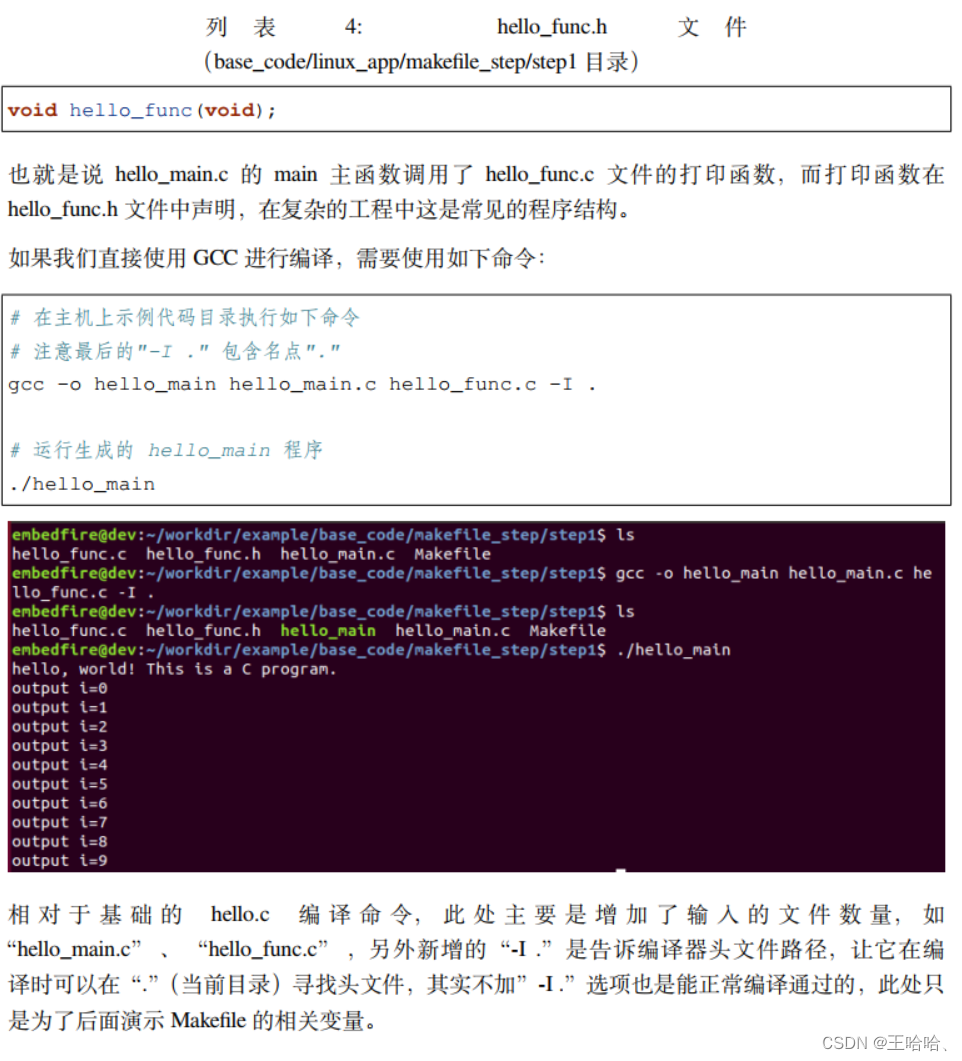

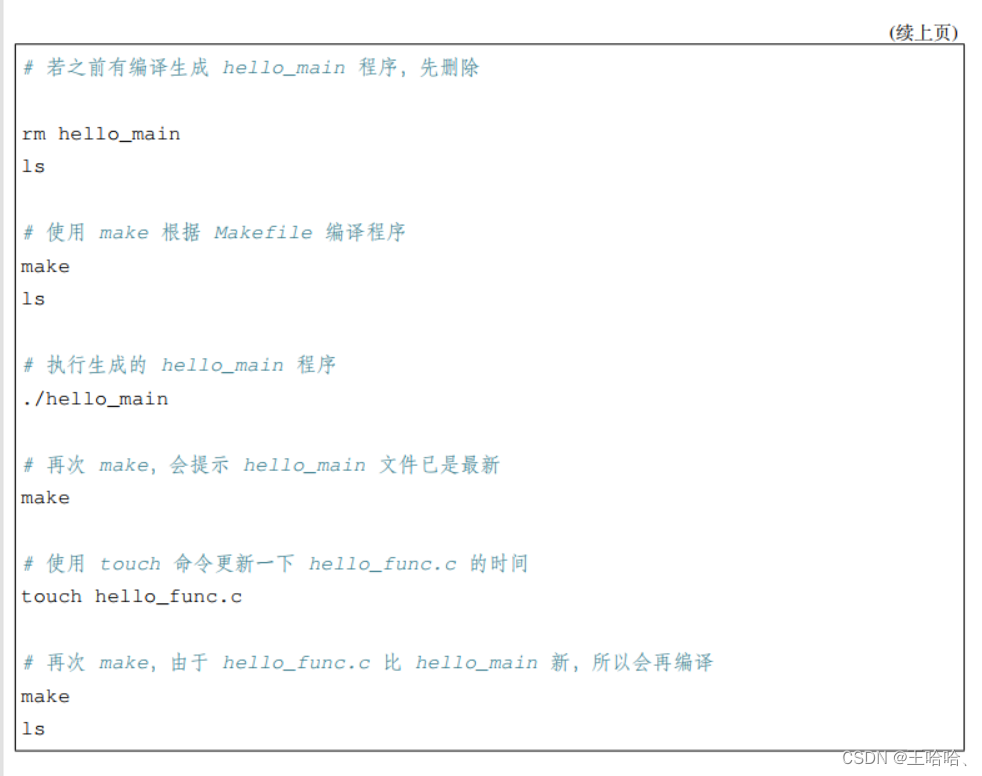

2.2、使用 Makefile 编译

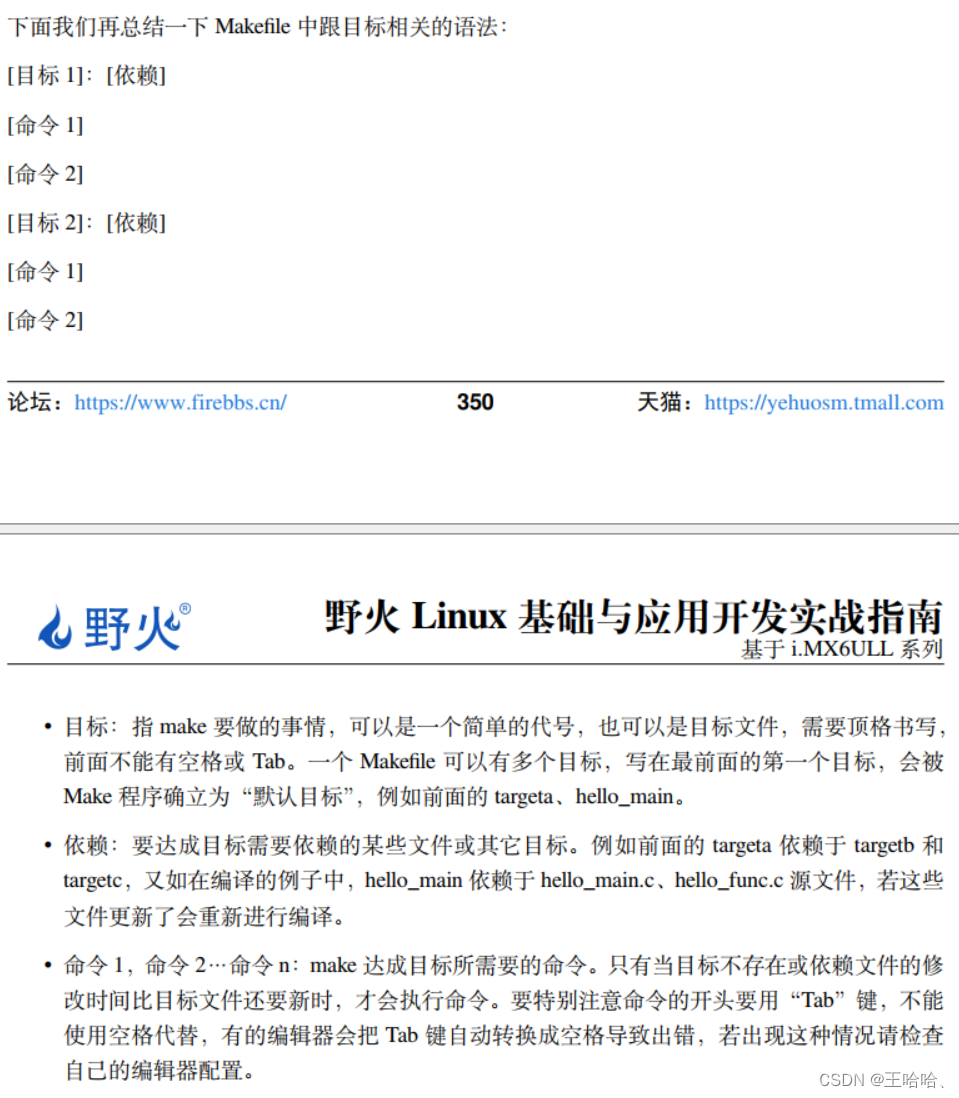

3、目标与依赖

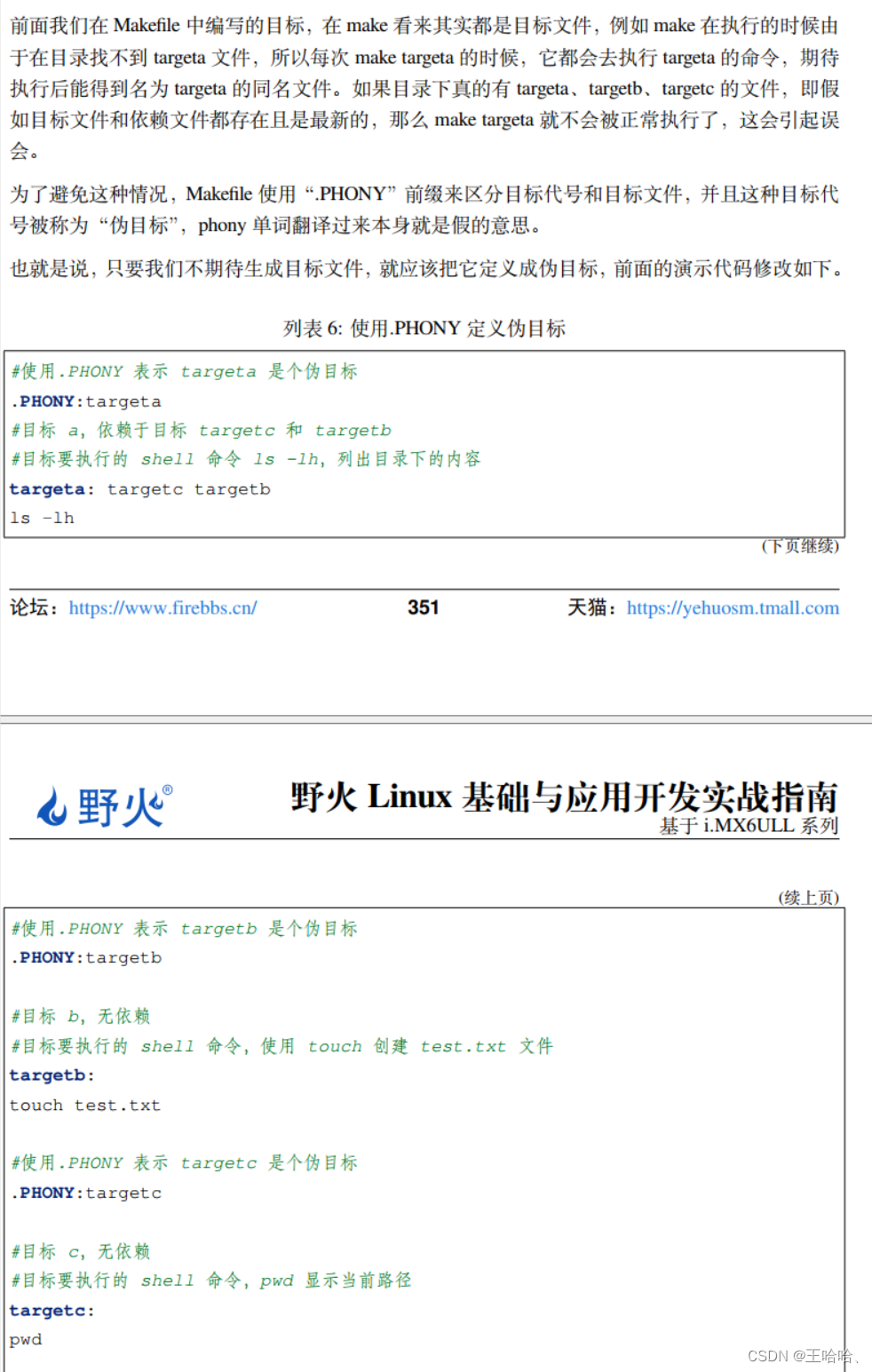

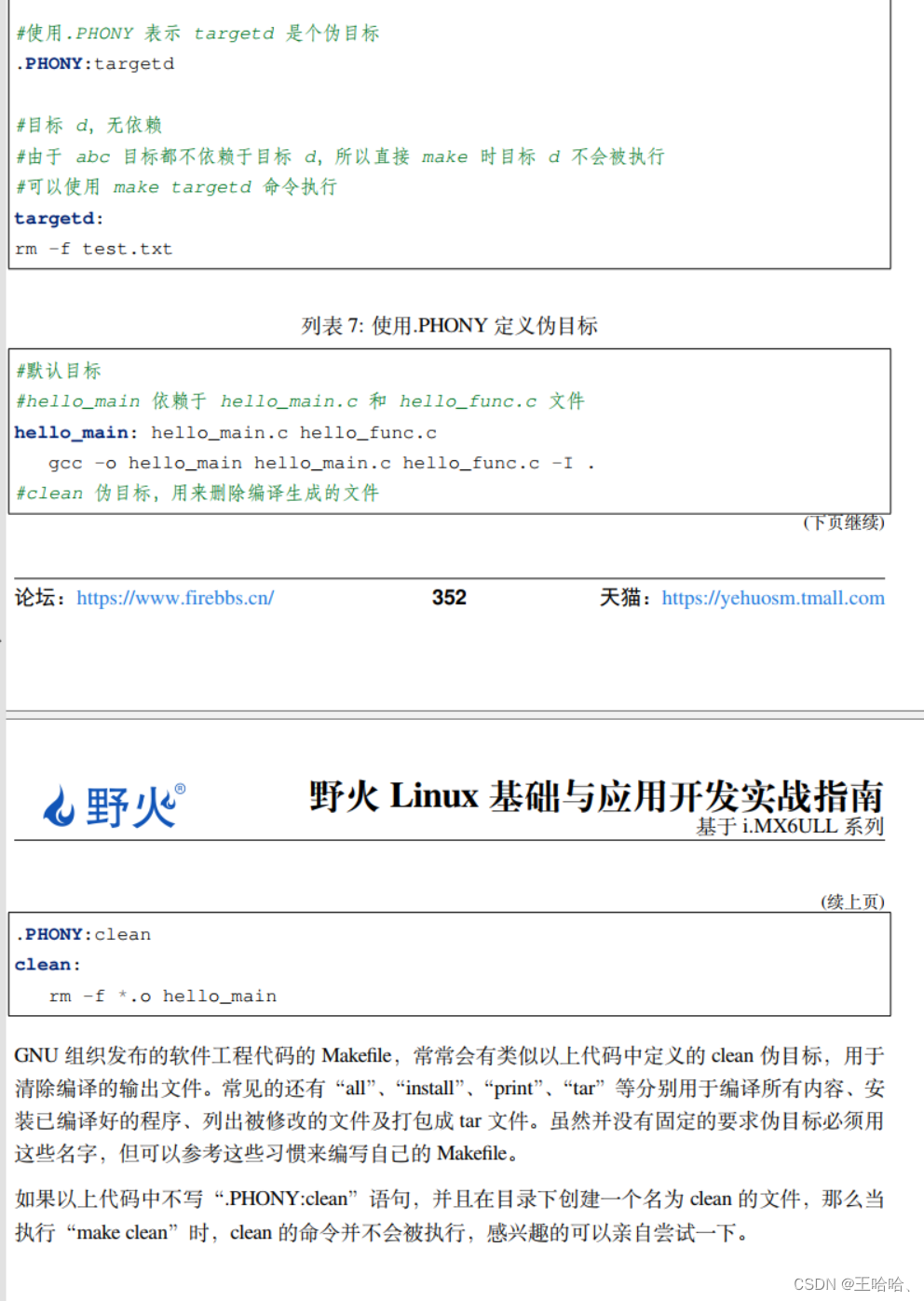

4、伪目标

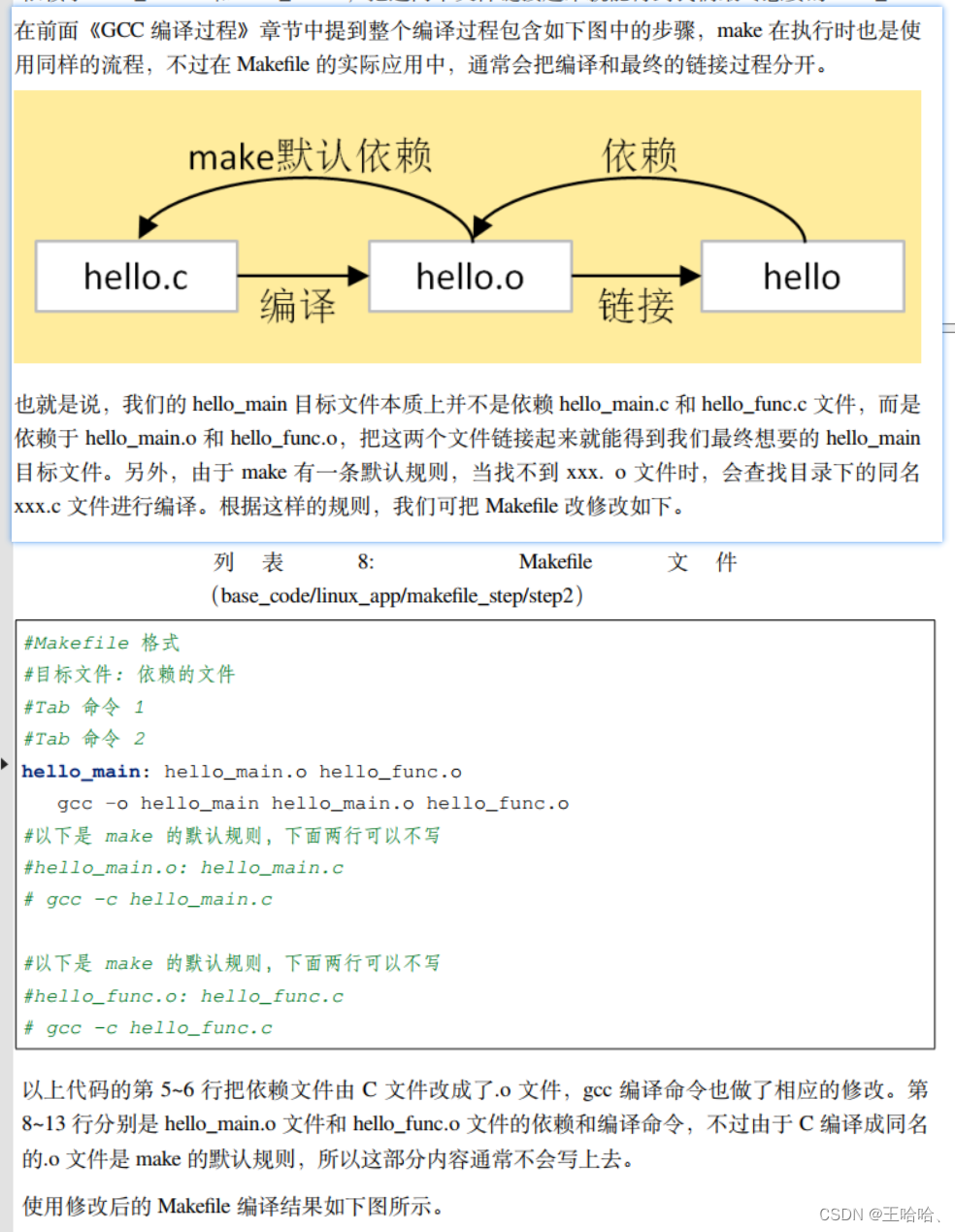

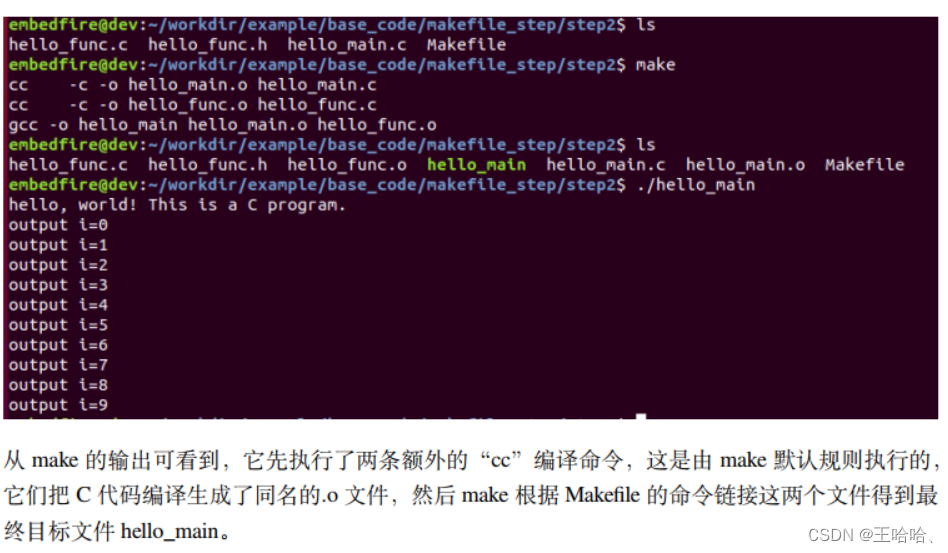

5、默认规则

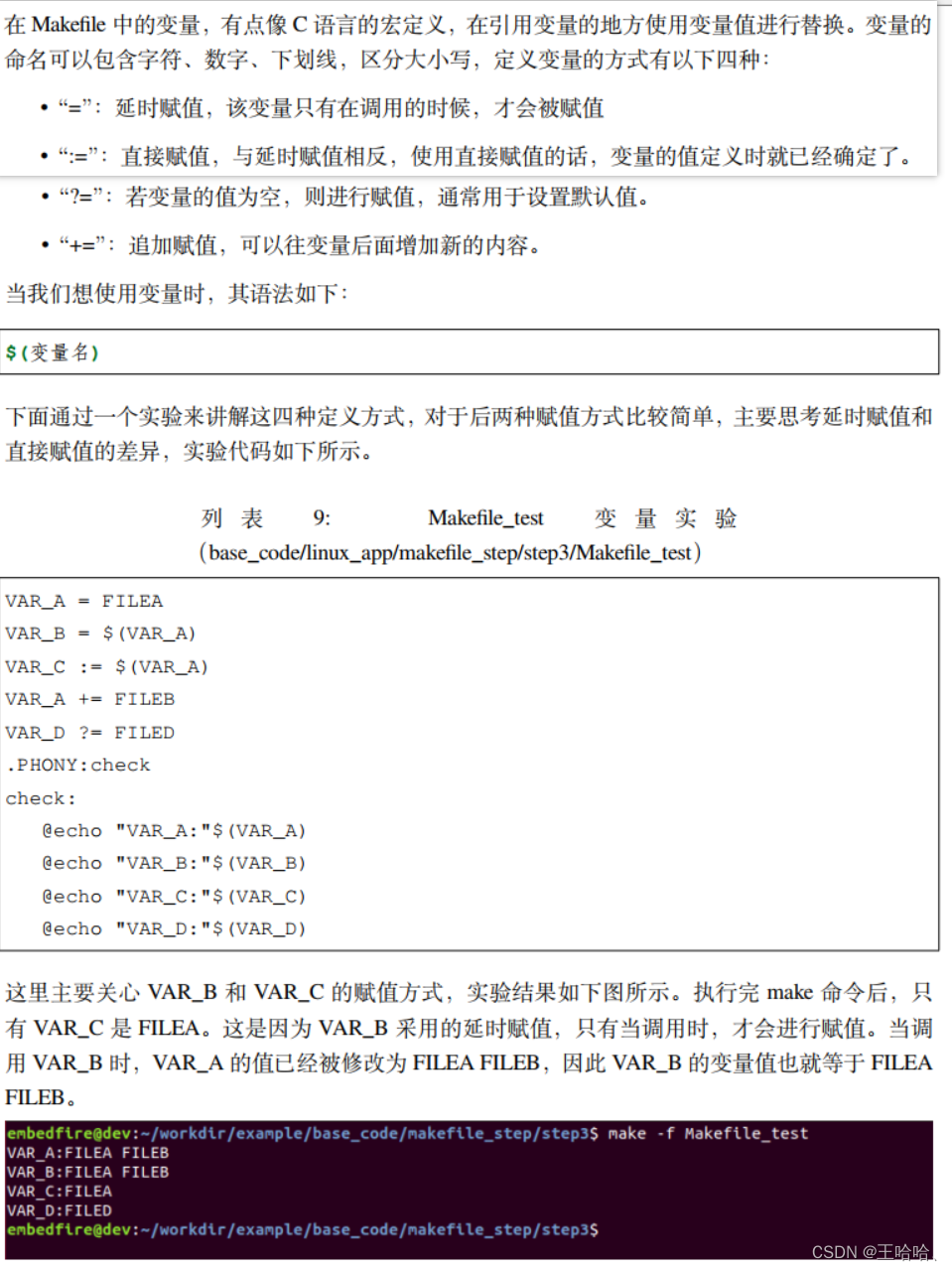

6、使用变量

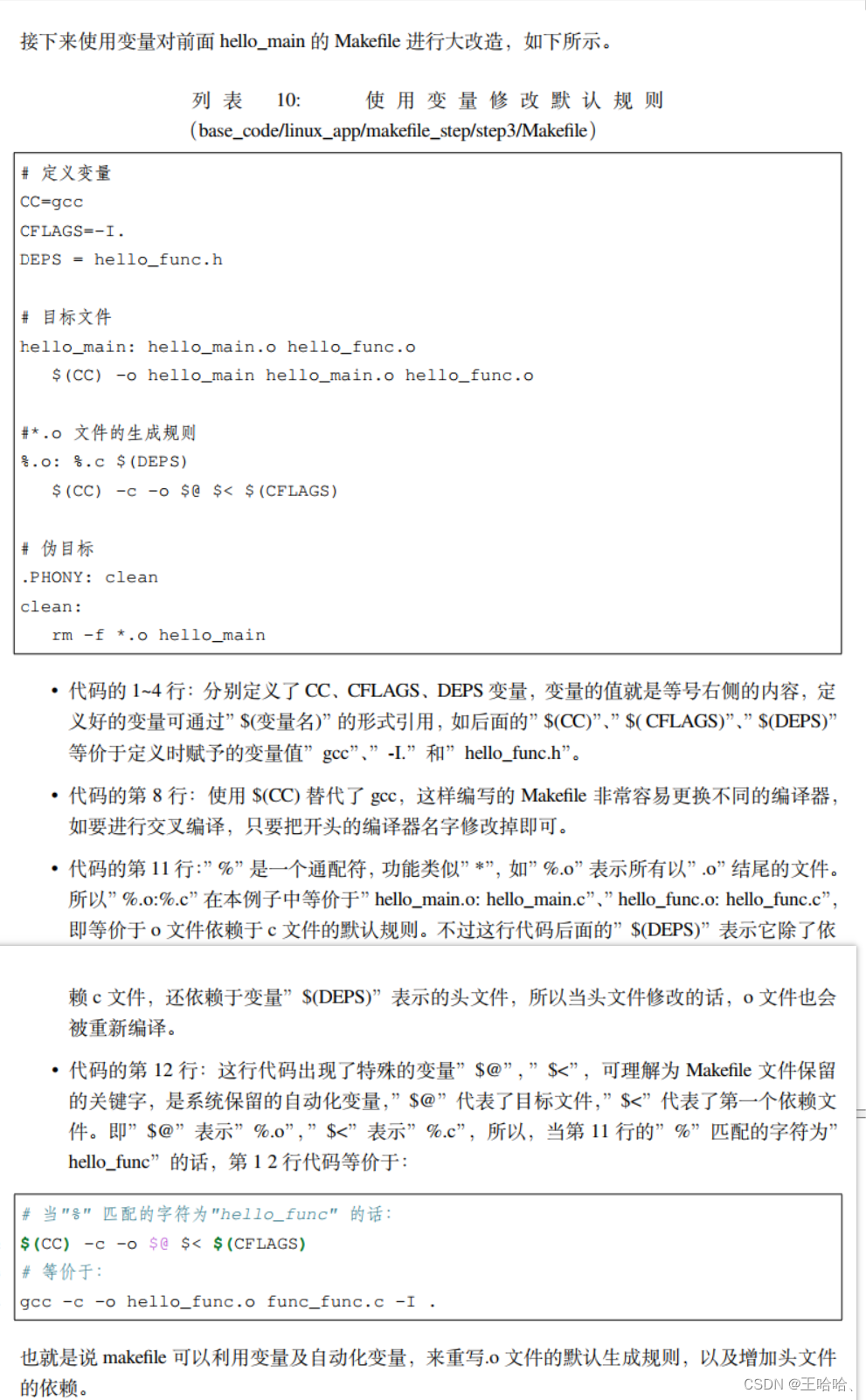

使用 C 自动编译成 *.o 的默认规则有个缺陷,由于没有显式地表示 *.o 依赖于.h 头文件,假如我

们修改了头文件的内容,那么 *.o 并不会更新,这是不可接受的。并且默认规则使用固定的“cc”

进行编译,假如我们想使用 ARM-GCC 进行交叉编译,那么系统默认的“cc”会导致编译错误。

要解决这些问题并且让 Makefile 变得更加通用,需要引入变量和分支进行处理。

6.1 基本语法

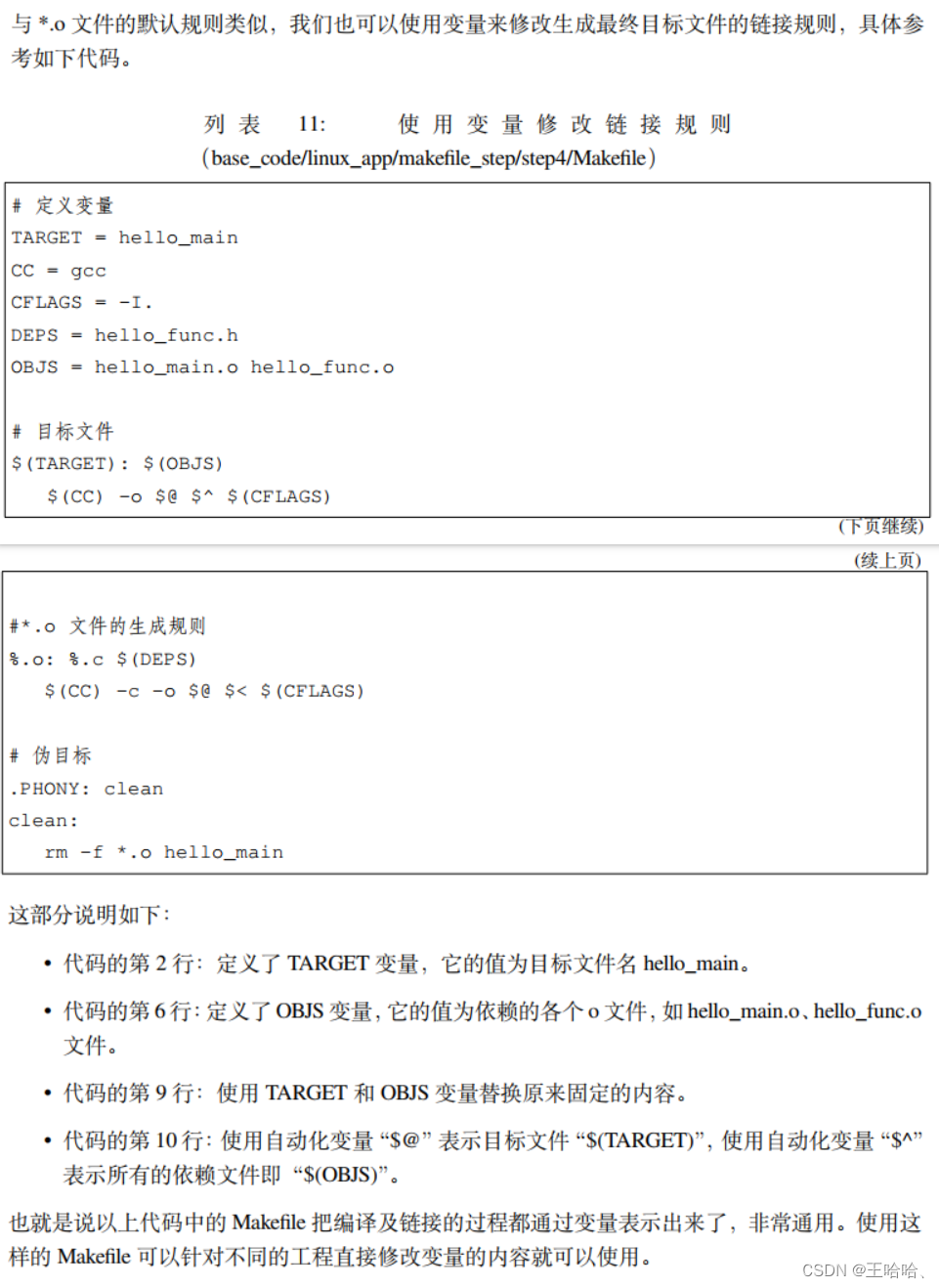

6.2 改造默认规则

6.3 改造链接规则

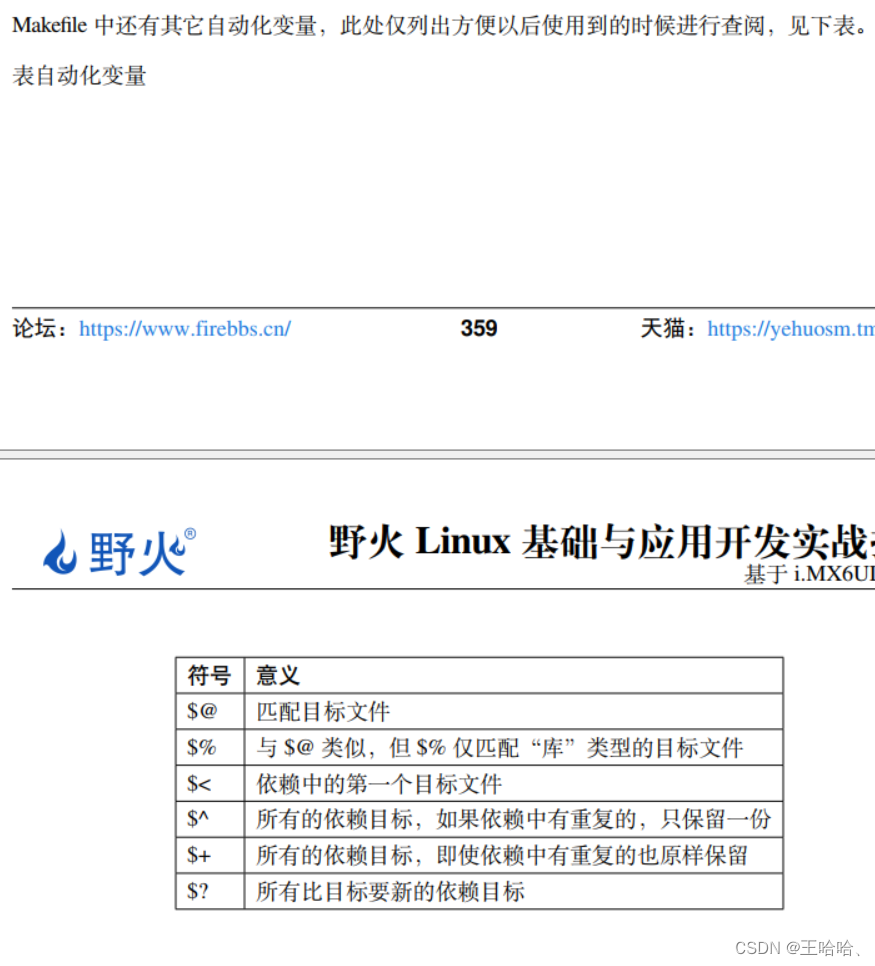

6.4 其它自动化变量

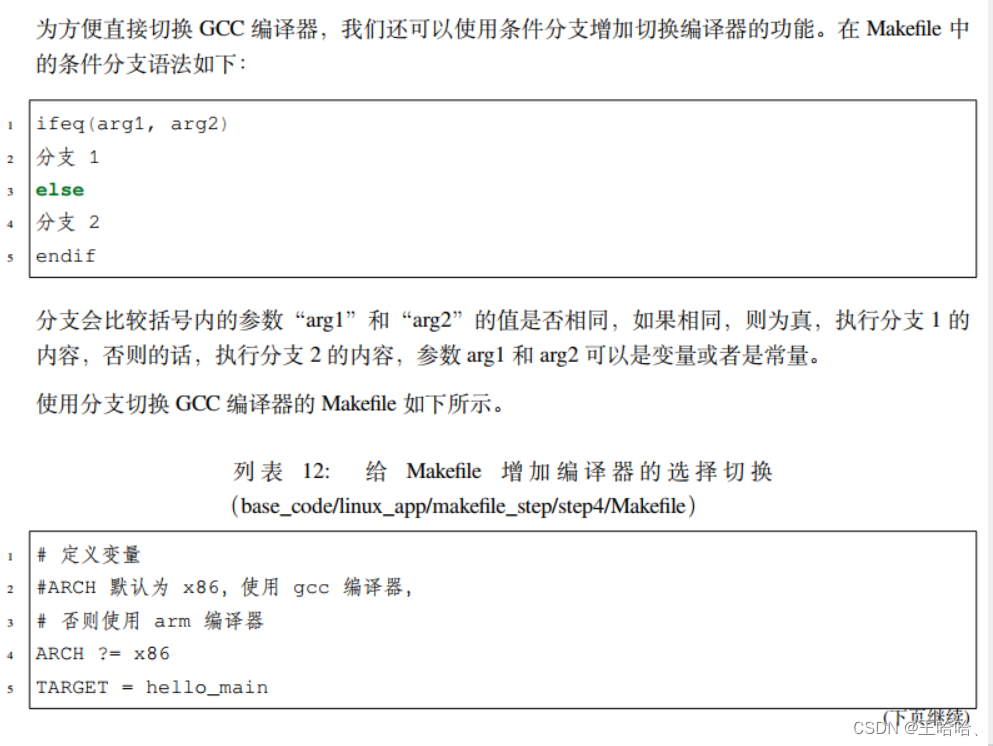

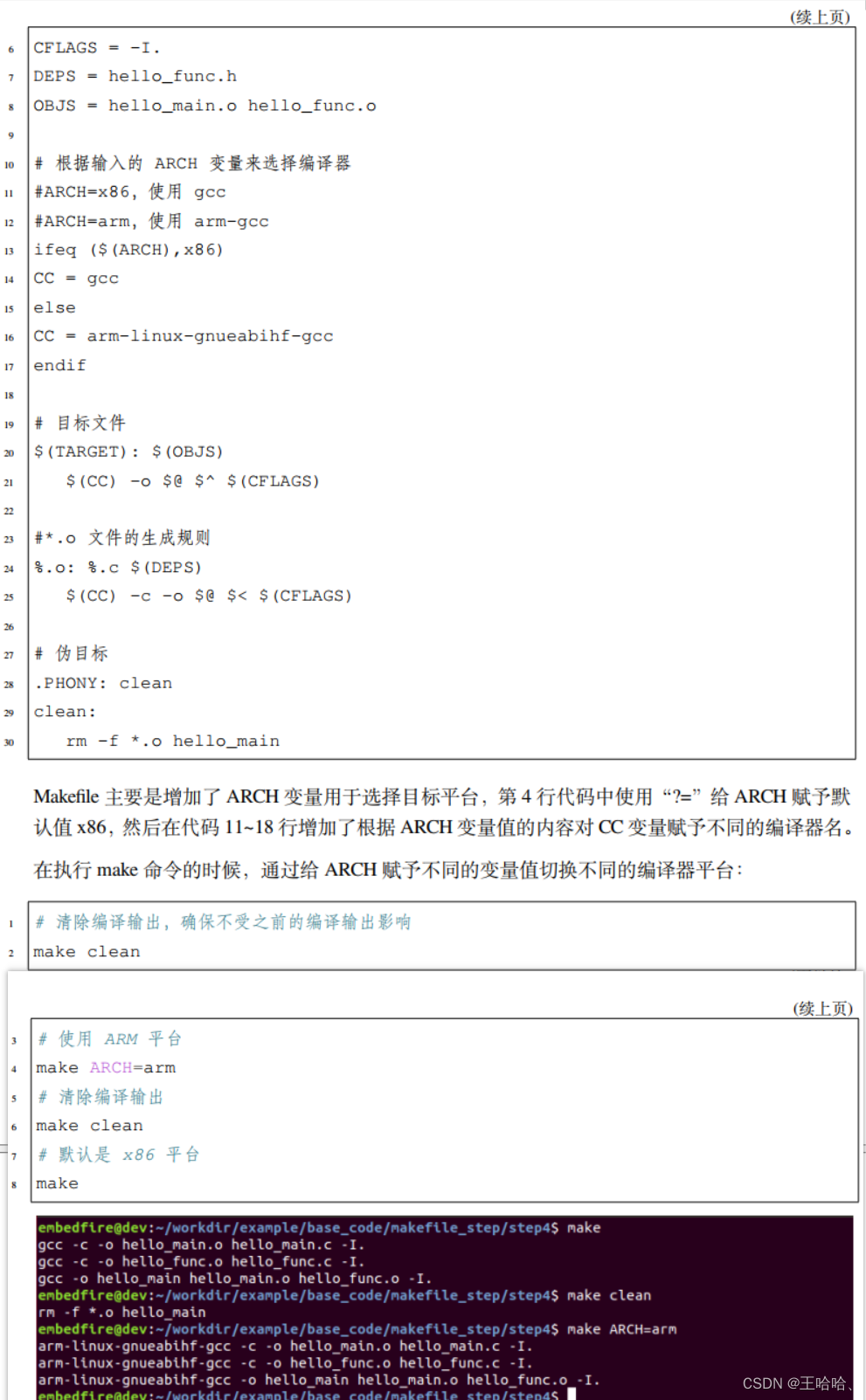

7、使用分支

8 使用函数

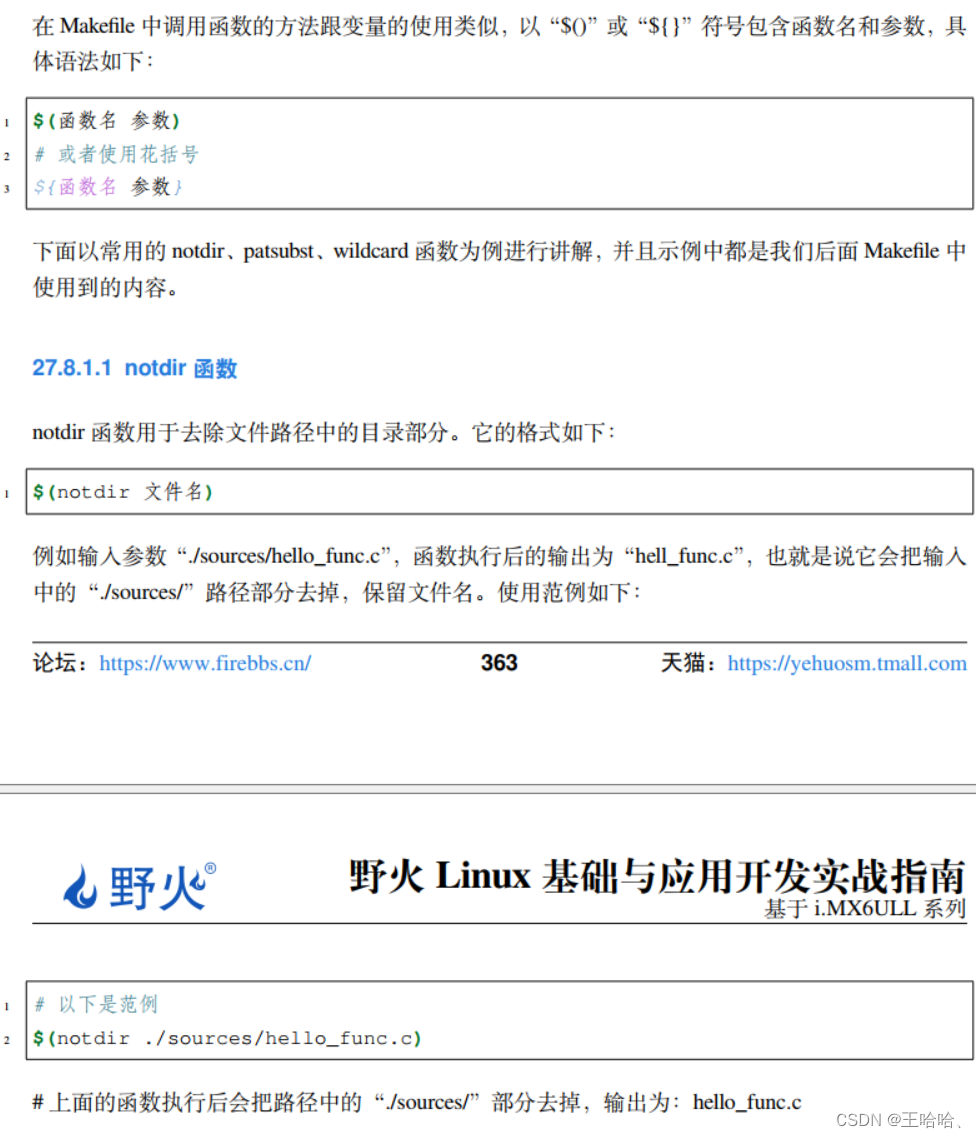

8.1、函数格式及示例

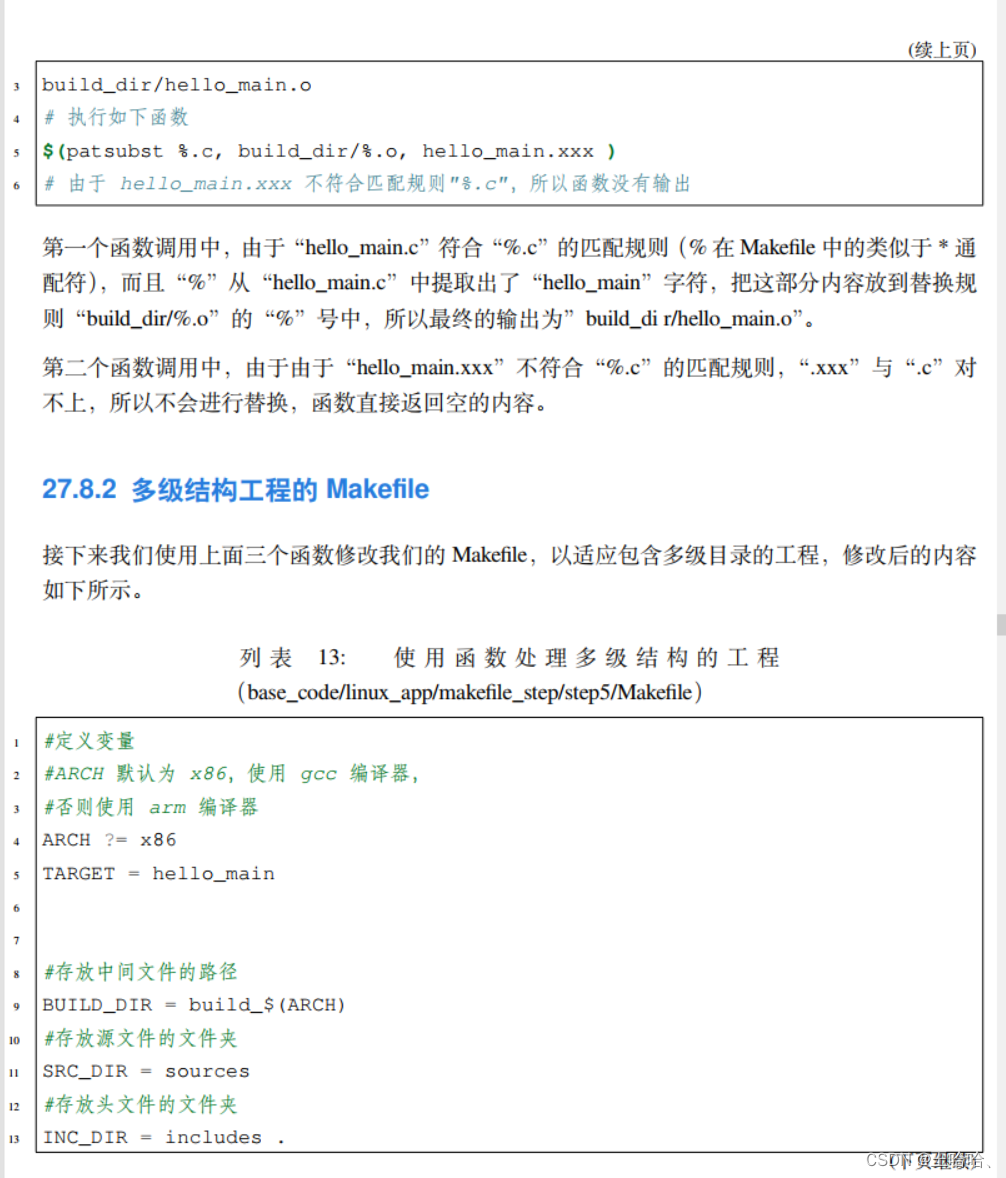

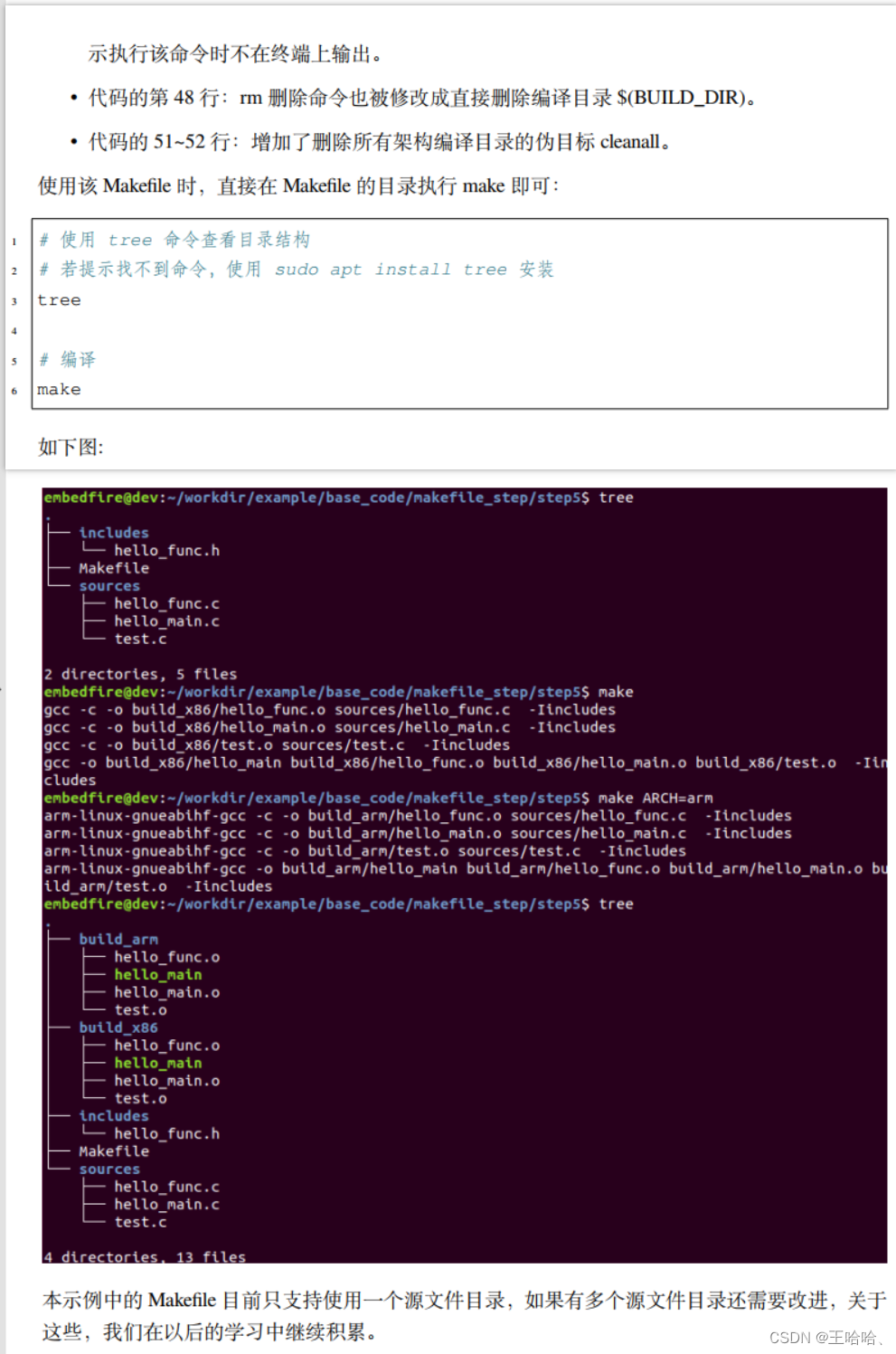

step5代码:

#Makefile格式

#目标文件:依赖的文件

#Tab 命令1

#Tab 命令2

#定义变量

#ARCH默认为x86,使用gcc编译器,

#否则使用arm编译器

ARCH ?= x86

TARGET = hello_main

#存放中间文件的路径

BUILD_DIR = build_$(ARCH)

#存放源文件的文件夹

SRC_DIR = sources

#存放头文件的文件夹

INC_DIR = includes .

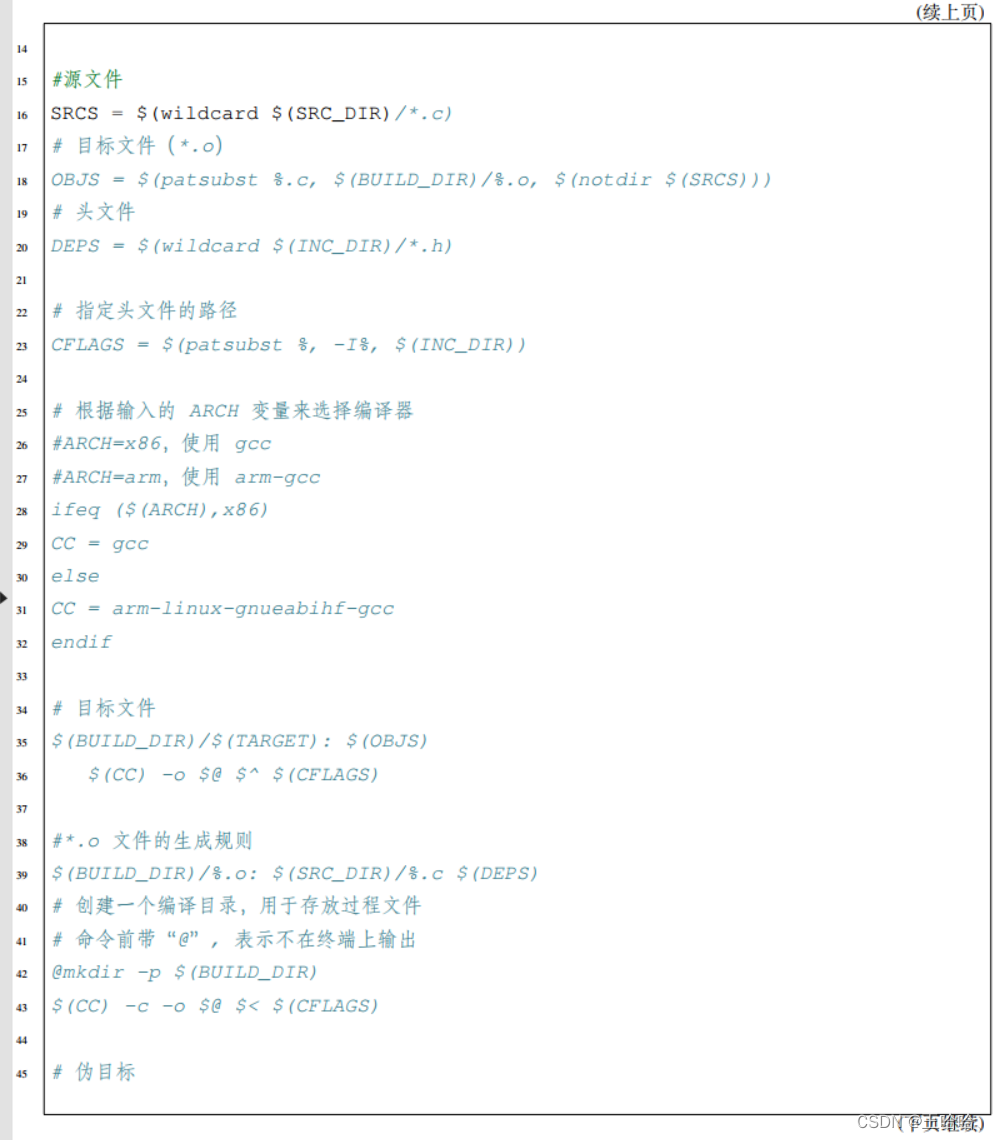

#源文件

SRCS = $(wildcard $(SRC_DIR)/*.c)

#目标文件(*.o)

OBJS = $(patsubst %.c, $(BUILD_DIR)/%.o, $(notdir $(SRCS)))

#头文件

DEPS = $(wildcard $(INC_DIR)/*.h)

#指定头文件的路径

CFLAGS = $(patsubst %, -I%, $(INC_DIR))

#根据输入的ARCH变量来选择编译器

#ARCH=x86,使用gcc

#ARCH=arm,使用arm-gcc

ifeq ($(ARCH),x86)

CC = gcc

else

CC = arm-linux-gnueabihf-gcc

endif

#目标文件

$(BUILD_DIR)/$(TARGET): $(OBJS)

$(CC) -o $@ $^ $(CFLAGS)

#*.o文件的生成规则

$(BUILD_DIR)/%.o: $(SRC_DIR)/%.c $(DEPS)

#创建一个编译目录,用于存放过程文件

#命令前带"@",表示不在终端上输出

@mkdir -p $(BUILD_DIR)

$(CC) -c -o $@ $< $(CFLAGS)

#伪目标

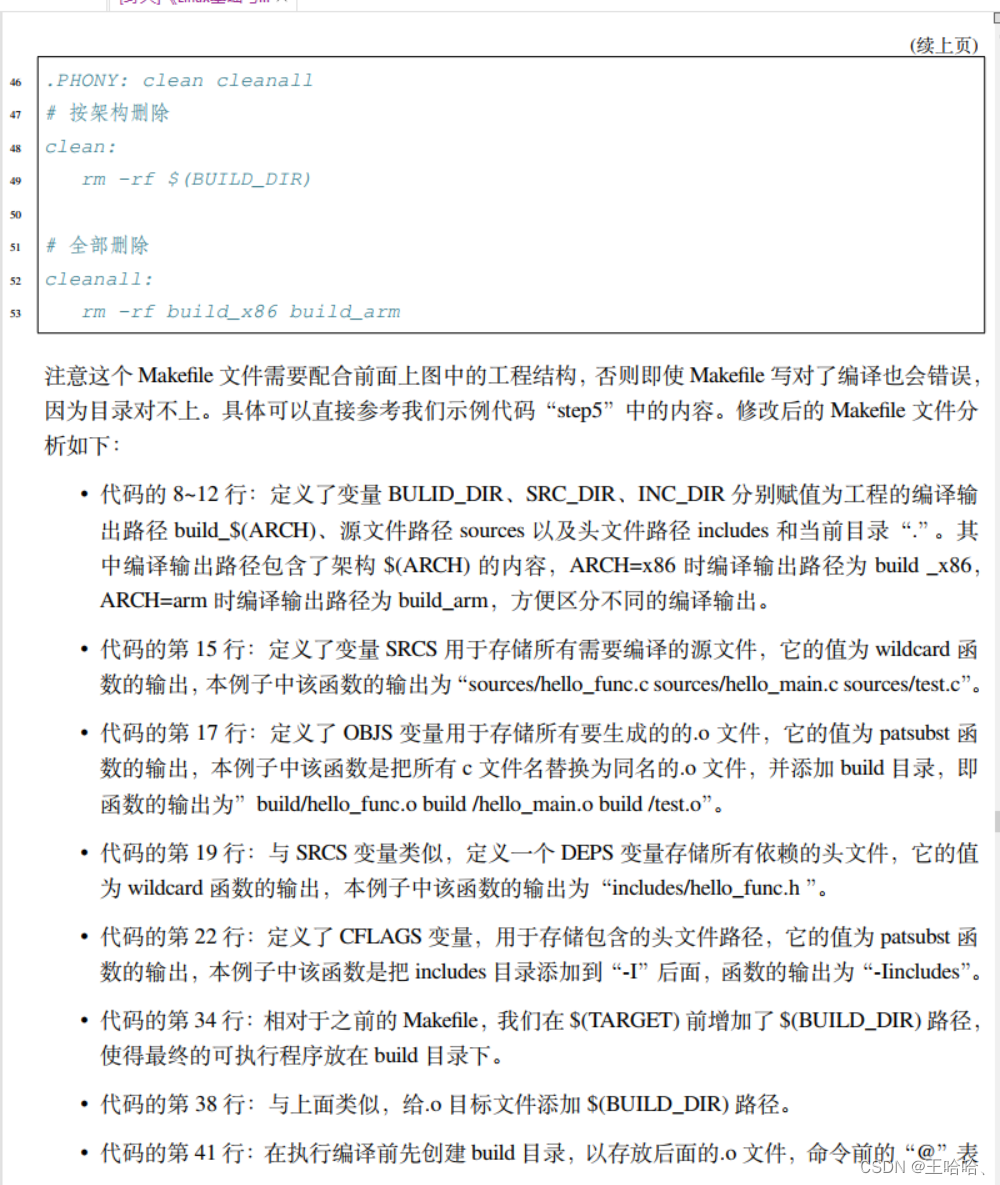

.PHONY: clean cleanall

#按架构删除

clean:

rm -rf $(BUILD_DIR)

#全部删除

cleanall:

rm -rf build_x86 build_arm

4109

4109

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?