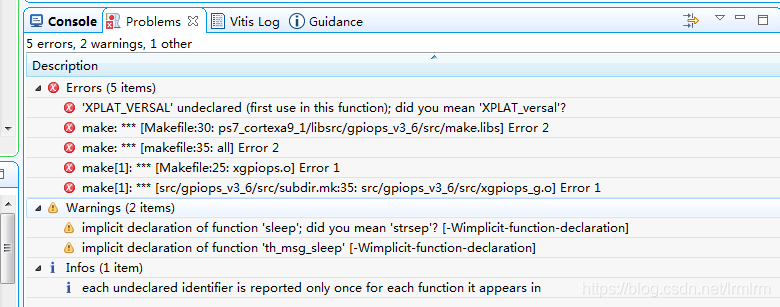

这两天尝试在zynq双核运行linux+ucos,在micrium官网下载Xilinx的SDK软件包后倒入到vitis编译时总是提示 XPLAT_VERSAL undeclared这个错误,如下图

检查错误位置,发现是gpiops文件内有几处判断使用到了XPLAT_VERSAL这个宏定义,但是仔细检查发现程序里面xplatform_info.h这个文件是有XPLAT_VERSAL这个定义的,只不过是XPLAT_versal,后面是小写而已,然后手动改为大写,或者直接在报错的文件内重新自定义一个相同的声明,这样编译是通过了,看起来也没什么问题,但是有点恼火的是如果bsp有变更重新编译后自己改动的部分又会被还原,实际上就是没有解决根本问题,自定义一个XPLAT_VERSAL只是临时办法,后来经过仔细研究,发现根本原因是micrium提供的ucos SDK开发包是基于visit 2019.1版本的,而且随着ucos 一起的ucos standalone程序包是旧版本的,这个standalone包在创建bsp工程时会被复制到bsp目录,而visit 2019.2默认的standalone是比较新的7.1版本,gpiops_v3_6这个程序依赖standalone 7.1版本,因此只要使用了ucos默认的standalone库就会报错XPLAT_VERSAL未定义。知道原因后就好办了,尝试从visit按照目录下查找standalone 7.1版本的位置 路径是 x:\Xilinx\Vitis\2019.2\data\embeddedsw\lib\bsp\standalone_v7_1,复制src文件夹内的所有文件到ucos 程序包内的 x:\ucos_v1_45\ucos\components\ucos_standalone\src,然后重新刷新visit软件仓库,最好在bsp设置内重新取消勾选ucos_standalone编译一次,然后再勾选ucos_standalone再重新编译一次,就可以发现编译正常通过了

博主在尝试在Zynq双核上运行Linux+UCOS时遇到编译错误XPLAT_VERSALundeclared。问题源于UCOSSDK基于旧版Vitis,而编译器使用的是新版,导致gpiops文件宏定义不匹配。解决方案是更新UCOSSDK中的standalone库为与Vitis版本匹配的7.1版本,并重新配置BSP工程,避免编译时错误。

博主在尝试在Zynq双核上运行Linux+UCOS时遇到编译错误XPLAT_VERSALundeclared。问题源于UCOSSDK基于旧版Vitis,而编译器使用的是新版,导致gpiops文件宏定义不匹配。解决方案是更新UCOSSDK中的standalone库为与Vitis版本匹配的7.1版本,并重新配置BSP工程,避免编译时错误。

2059

2059

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?