4.1背景

Xilinx的axidmatest驱动程序对axidma这个IP的软件驱动方式做了很基础很清晰的示范。但是该驱动程序也有让笔者觉得值得使用不方便的地方。首先,该驱动程序只能在probe/remove函数中进行收发的执行。这意味着如果使用者想要反复执行收发的逻辑,首先需要将其单独编译成模块,然后利用动态插入/拔除内核模块的方式执行收发逻辑。其次,该驱动的数据验证方式利用pattern的对比进行确认,执行逻辑稍显繁琐。

基于以上背景,笔者在借用axidma部分概念的基础上重写了一个测试驱动程序,命名为axidmatester。本文基于该驱动进行部分分析。

4.2 改进方案

笔者的axidmatester驱动程序针对第一部分提到的问题,主要进行两方面的改进。

首先,对axidma的自发自收逻辑从probe函数拿了出来。axidmatester驱动自带sysfs节点,每次利用cat命令访问该节点,即可触发一次自发自收来验证fpga部分设计的有效性。也就是向workqueue添加一个work,在该work中进行数据的收发测试。

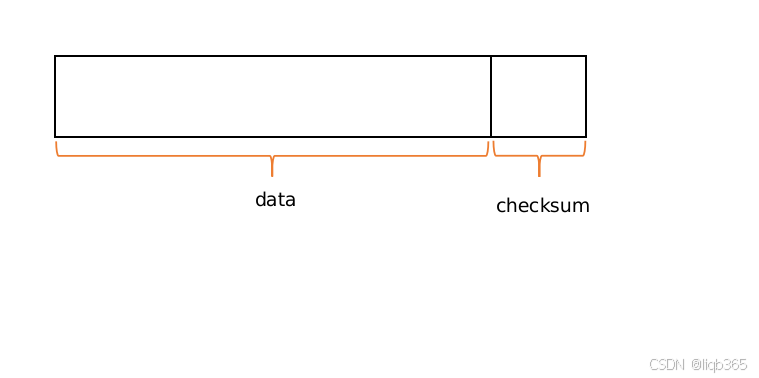

其次,axidmatester驱动抛弃了pattern对比的验证方式。scatterlist中的所有buffer均被分割为下面的格式:

每次测试在data部分生成随机数,然后计算16比特的校验码放到buffer的最后两个字节中。

收到数据后重新计算data部分的校验码和传递过来的checksum进行对比以得出校验结果。

4.3 实现

放这儿了。

2312

2312

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?