1.概述

axidmatest驱动程序是Petalinux自带的AXIDMA驱动验证程序,该驱动在初始化的过程中,通过dmaengine机制进行自发自收来验证FPGA设计的成功。本文讨论数据验证的方式。内容基于6.1.5内核。

总的来讲,数据的校验并非是通过校验码等机制实现验证,主要是通过pattern对比进行的。比如一块数据,会被分成三部分。每部分会被填入不同的pattern,传输后对传输后的数据进行pattern的对比,以此来判定axidma传输的成功与否。

2.填入pattern

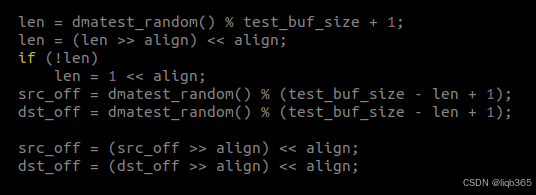

上一章节谈到数据发送前后会被分成三部分。这三部分会被填入不同的pattern。中间这部分的起始地址和大小是随机动态生成的。

上图中的代码里面,dmatest_random函数生成一个随机数,计算后的len变量就是传输数据的第二部分的大小。src_off是传输前的buffer第二部分起始地址。dst_off是传输目的buffer第二部分起始地址。

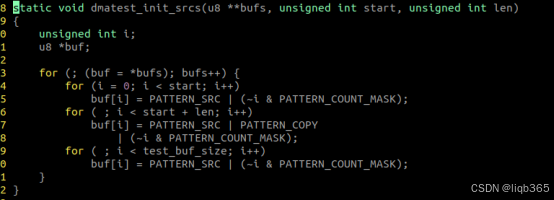

source数据的pattern填入的逻辑在dmatest_init_srcs函数中。

外层的for循环,处理的是scatterlist中的每个buffer。该驱动中sg包含13块buffer,每个16KB大小。内层三个for循环分别填入第一块,第二块,第三块数据的pattern。

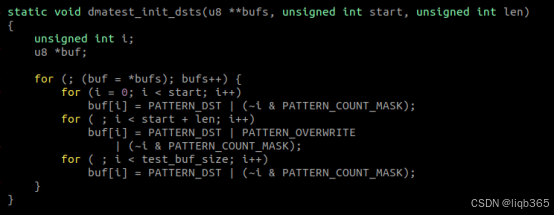

destination数据patten填入在dmatest_init_dsts中。

逻辑与dmatest_init_srcs相似,不过多描述。

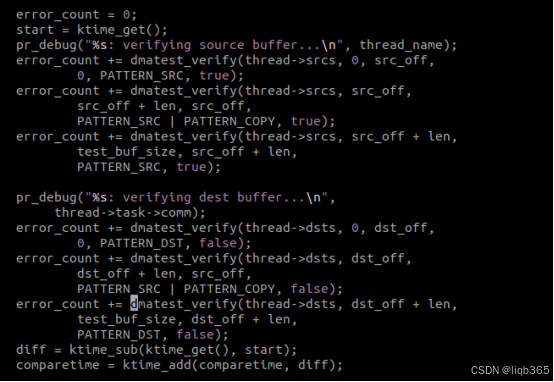

3.patten验证

dma传输后分别对buffer的三个部分进行校验:

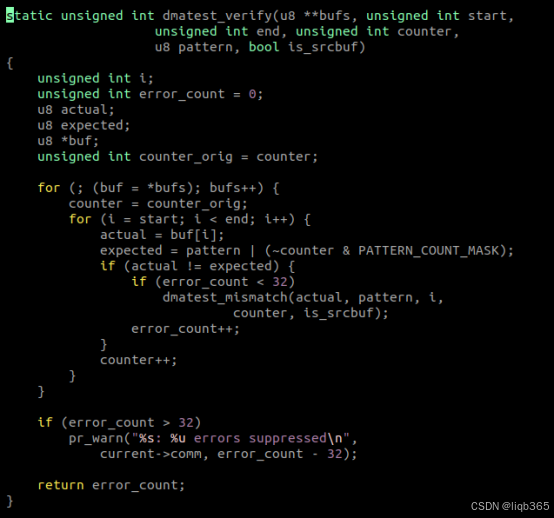

对数据的验证在dmatest_verify中。

外层for循环处理sg中的每块buffer。

内层循环对一块buffer的pattern进行验证,如果pattern不符合,对error_count进行累加,这个计数程序执行的最后会打印出来。

4.总结

数据验证是通过pattern进行的。比如一块数据,被分成三部分。比如下图中的一块数据,被分成A,B,C三个部分。

每个部分的每个字节被填入不同的pattern。每次测试,中间的B部分的其实地址和大小是随机生成的。DMA传输之后,source和destination两个buffer会分别通过pattern进行对比,如果pattern对不上,会被进行计数统计。

4772

4772

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?