不使用petallinux构建apu核rpu之间的核间通信

一:首先需要在RPU中创建openamp裸机程序:居于openamp框架实现rpmag通信

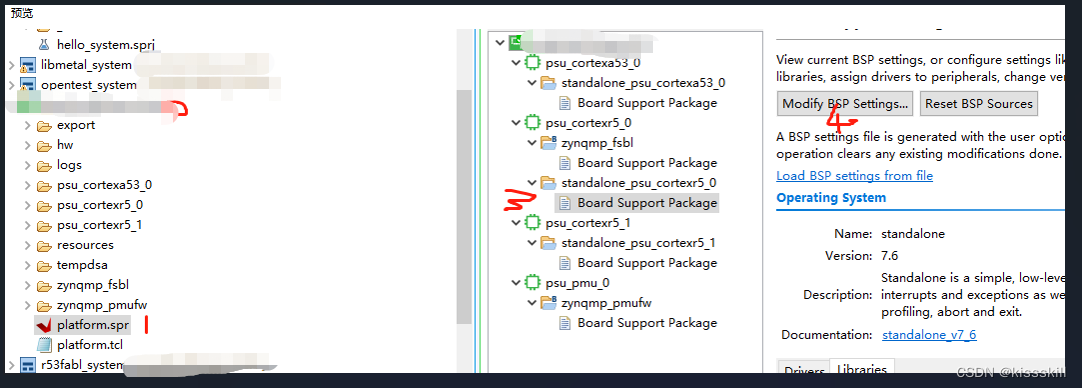

打开vitis平台将xsa导入并创建平台工程,然后再平台工程中找到platform.spr文件并打开,可以看到平台添加的cpu核支持包:

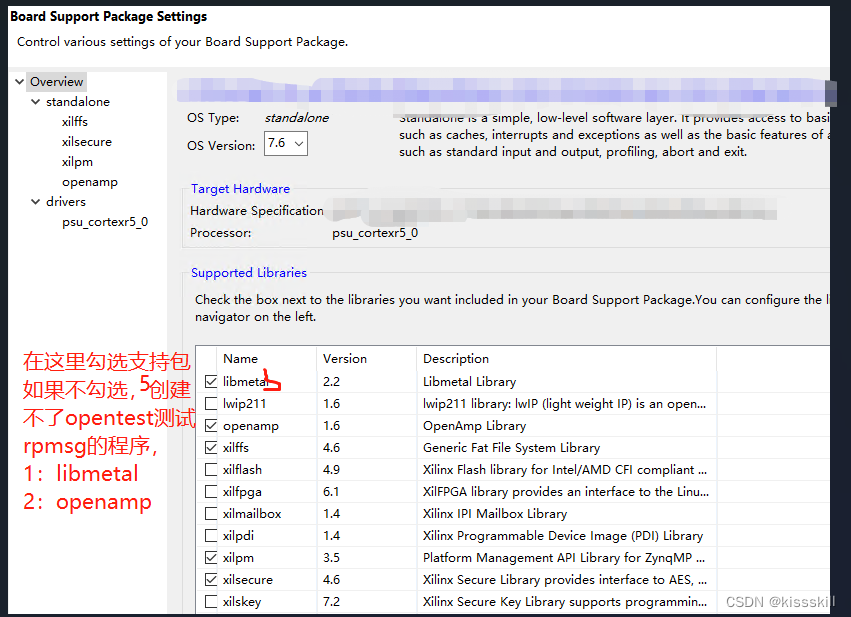

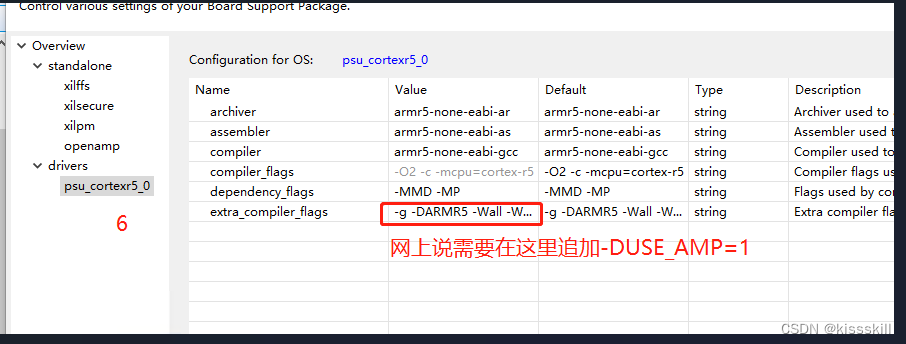

首先需要在平台下面对应的芯片中,打开board support支持包(modify BSP setting),选中里面的lib库metallib,amplib库(注意图片截取的是1.6和2.4版本,实际opentest工程是用1.7openamp/2.4libmetal)

上述步骤操作完成后,

在芯片bsp下面的system.mss描述中出现下述lib描述添加:

BEGIN LIBRARY

PARAMETER LIBRARY_NAME = openamp

PARAMETER LIBRARY_VER = 1.7

PARAMETER PROC_INSTANCE = psu_cortexr5_1

END

BEGIN LIBRARY

PARAMETER LIBRARY_NAME = libmetal

PARAMETER LIBRARY_VER = 2.4

PARAMETER PROC_INSTANCE = psu_cortexr5_1

END然后编译platform平台工程。

完成编译后,开始创建application程序,在vitis工具中file->new->application创建openamp的测试程序:选中r50,选中opentest工程创建即可。

二:内核设备树修改如下:

linux 内核设备树描述: 参考链接

//https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/1896251596/OpenAMP+2021.1

/dts-v1/;

#include <dt-bindings/power/xilinx-zynqmp-power.h>

#include "zynqmp.dtsi"

#include "zynqmp-clk-ccf.dtsi"

#include <dt-bindings/phy/phy.h>

/ {

chosen {

bootargs = "earlycon";

stdout-path = "serial0:115200n8";

};

aliases {

i2c0 = &i2c0;

i2c1 = &i2c1;

spi0 = &qspi;

mmc0 = &sdhci0;

serial0 = &uart0;

serial1 = &uart1;

ethernet0 = &gem1;

// rtc0 = &rtc0;

// nvmem0 = &eeprom;

};

memory@0 {

device_type = "memory";

reg = <0x00000000 0x00000000 0x00000000 0x7FF00000>, <0x00000008 0x00000000 0x00000001 0x80000000>;

};

gem_clk: psgrt_gem_clock {

compatible = "fixed-clock";

#clock-cells = <0>;

clock-frequency = <125000000>;

};

usb_clk: psgrt_usb_clock {

compatible = "fixed-clock";

#clock-cells = <0>;

clock-frequency = <100000000>;

};

reserved-memory {

#address-cells = <2>;

#size-cells = <2>;

ranges;

global_reserved: global_reserved@0 {

no-map;

reg = <0x0 0x0 0x0 0x00800000>;

};

rpu0vdev0vring0: rpu0vdev0vring0@800000 {

no-map;

reg = <0x0 0x00800000 0x0 0x100000>;

};

rpu0vdev0vring1: rpu0vdev0vring1@900000 {

no-map;

reg = <0x0 0x00900000 0x0 0x100000>;

};

rpu0vdev0buffer: rpu0vdev0buffer@A00000 {

no-map;

reg = <0x0 0xA00000 0x0 0x200000>;

};

rpu0load: rpu0load@1000000 {

no-map;

reg =

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5650

5650

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?