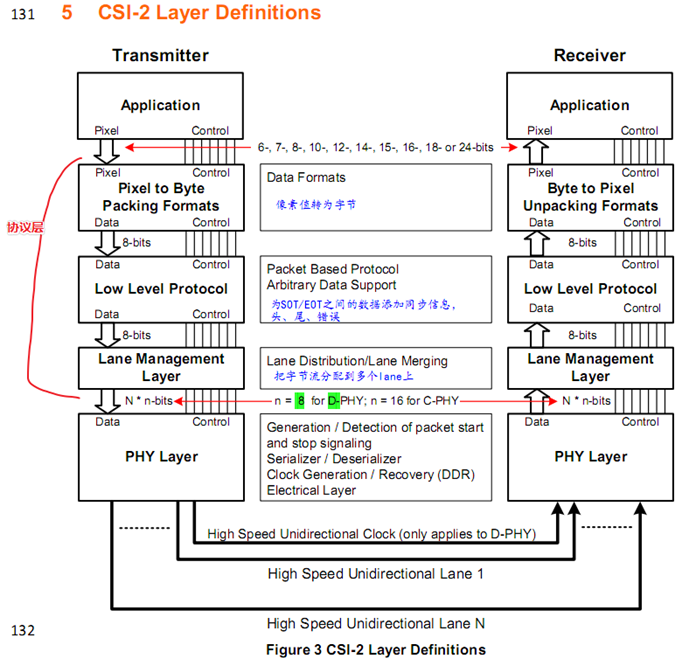

1、CSI-2层功能

CSI-2的手册中主要介绍了,协议层的功能块:像素重组成字节(协议中提到的仅适用于标准图像格式,实际可以自定义),LLP层数据拆分按长短包组包+包头+ECC+CRC,字节按照lane通道分配。

重点在LLP的长包+短包格式。其它的有整帧图像的数据组织方式,IIC控制协议,ECC的计算原理,CRC的计算原理,虚拟通道的使用。

CSI-2 spec并没有规定最终的图像输出接口,在协议层定义,可自定义两种接口IDI(image data interface像素仍按字节打包),IPI(image pixel interface直出像素,行场使能)。

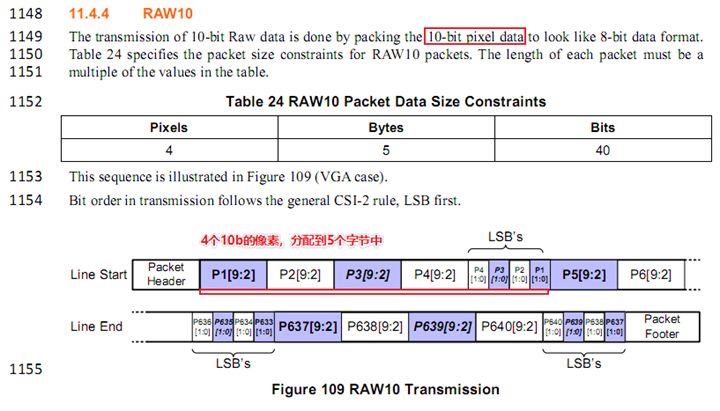

2、像素转换字节

以RAW10为例(实际工程中采用非标格式:图像像素10bit且非标,用256b来装入25个像素,高6bit不是像素,但用来表示该分组中有几个有效像素)。

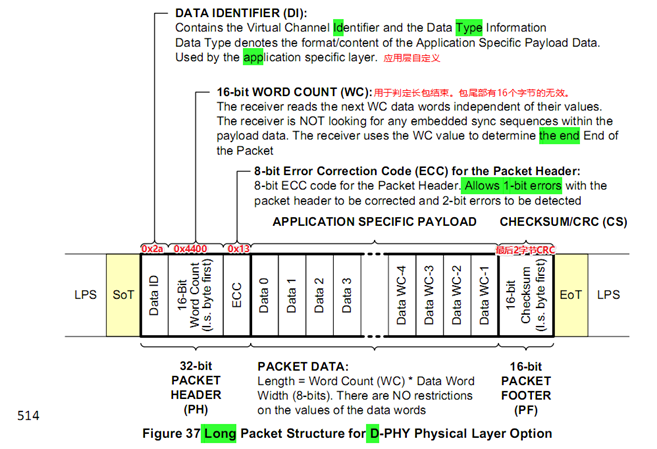

3、LLP长短包格式

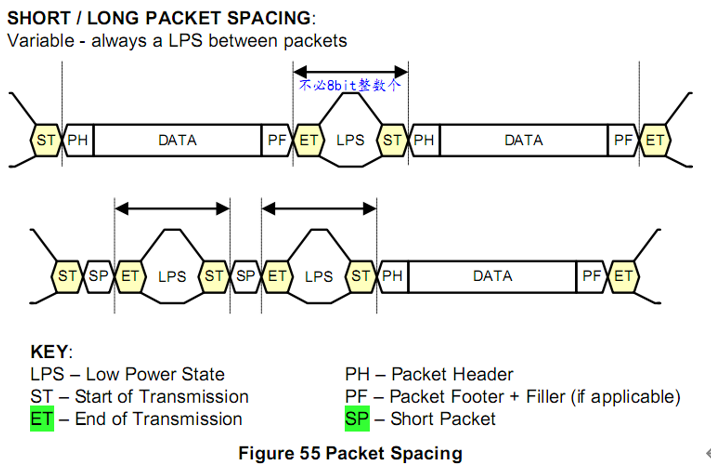

payload须为字节整数倍,每个字节LSB低位先出。

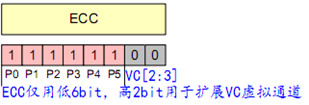

ECC仅使用低6bit,高2bit可用于扩展虚拟通道VC个数到4bit共16个。

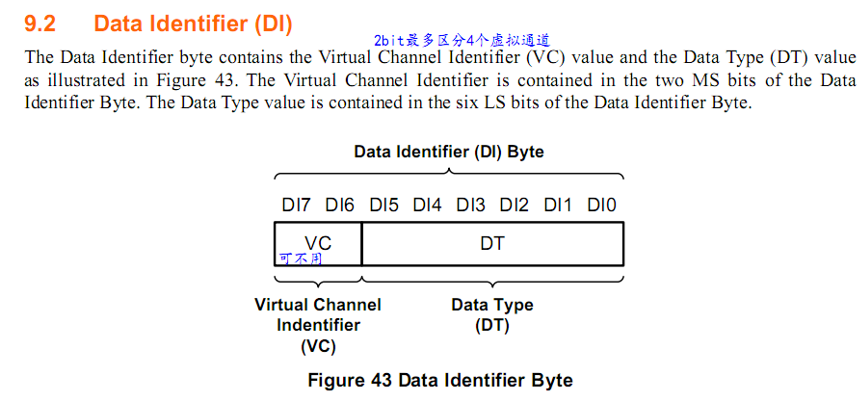

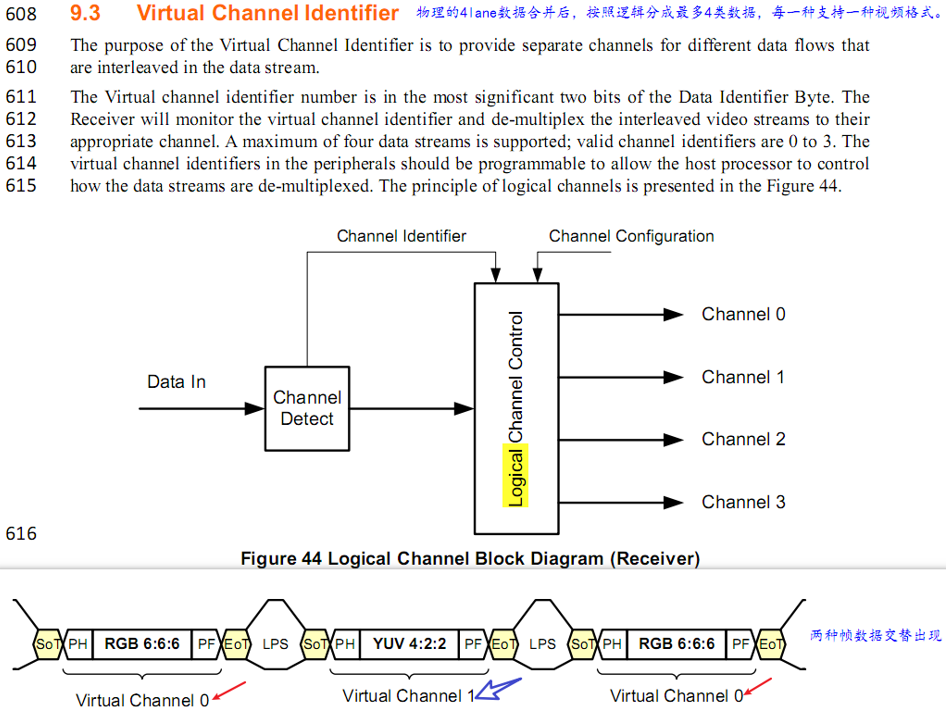

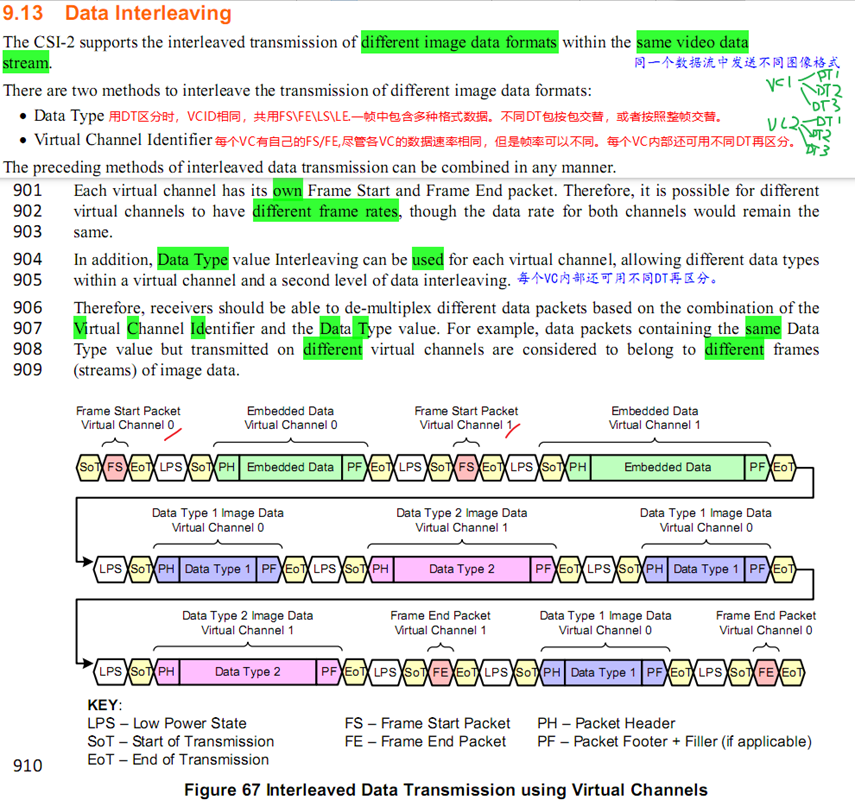

使用VC可同时发送不同格式的图像,且帧行头尾不共用;

使用DT时同时发送不同分辨率的图像,帧率相同,帧行头尾共用;

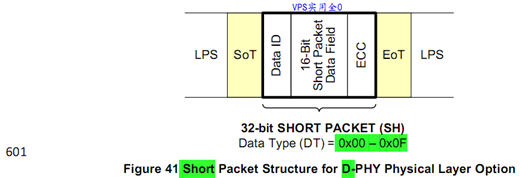

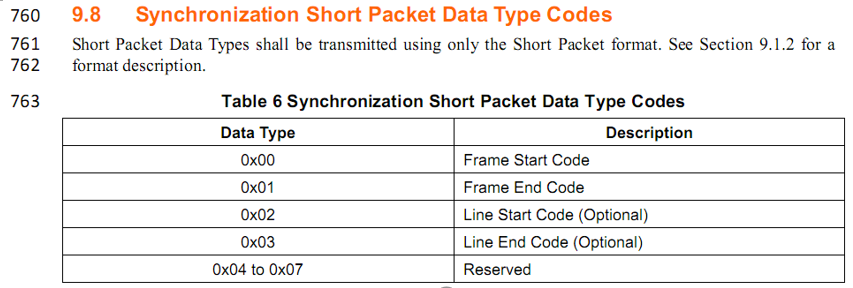

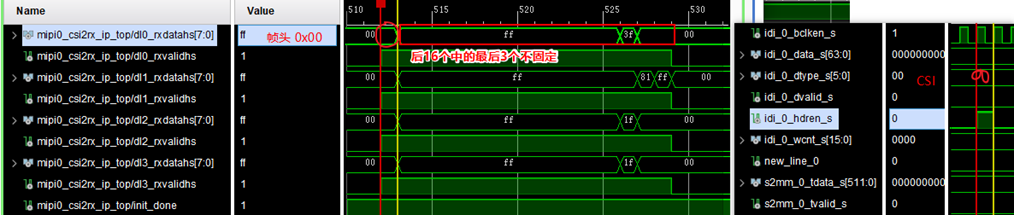

3.1 帧头DT=0x00

使用Xilinx DPHY IP接收的CSI原始数据。每个通道尾部有多余的数据ff,根据WC字节长度去除。

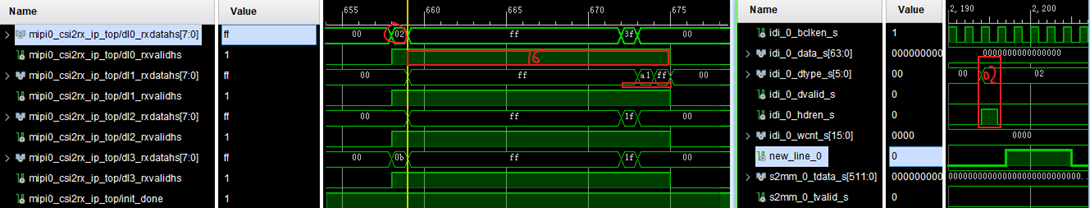

3.2 行头DT=0x02

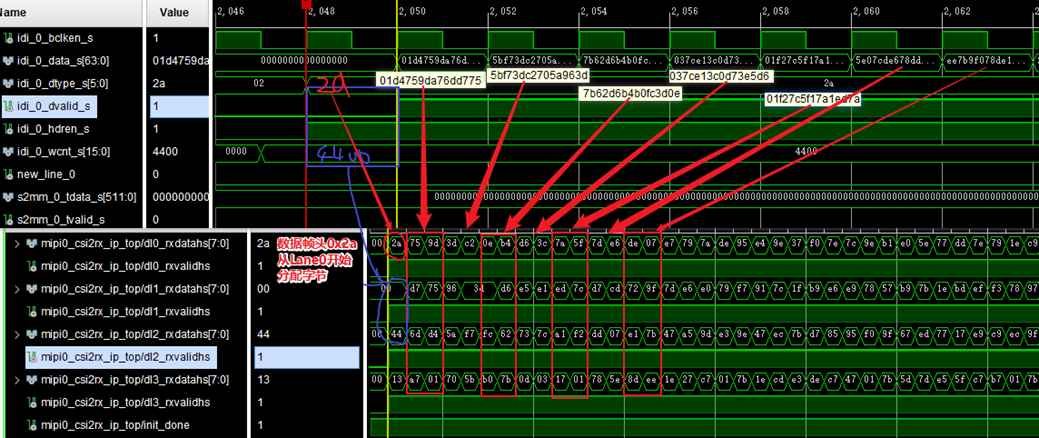

3.3 数据头DT=0x2a

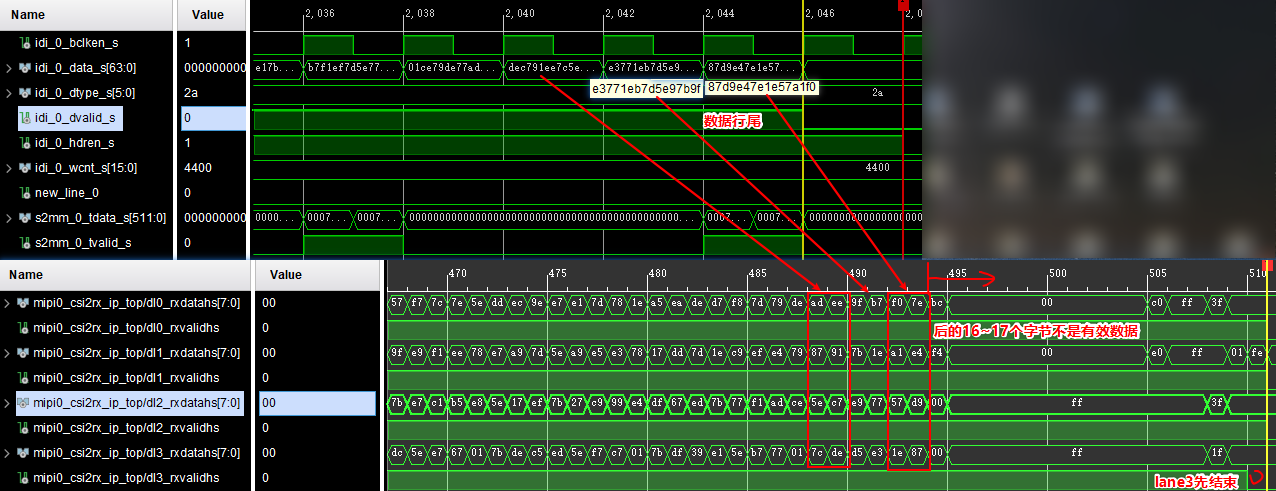

数据尾部整体视图

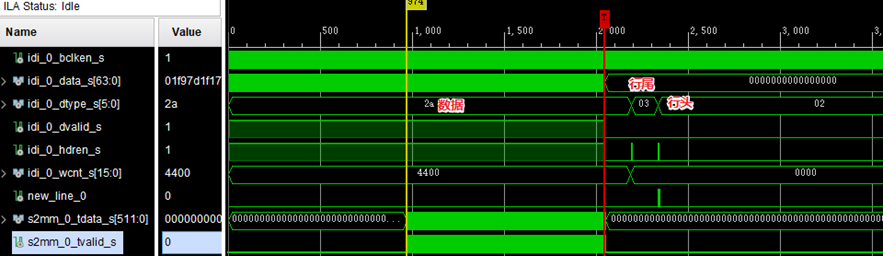

行尾数据,每个lane最后有16~17个无效字节。数据长包最后2字节是CRC(图中0xf4bc),包头第4字节是ECC。

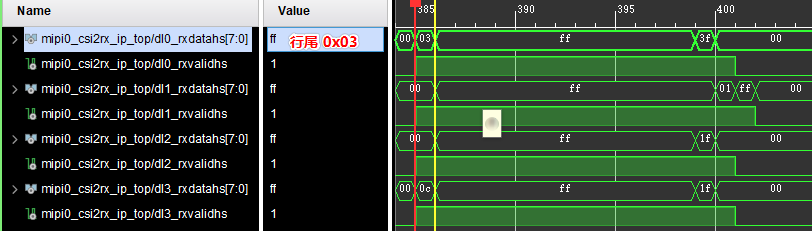

3.4 行尾DT=0x03

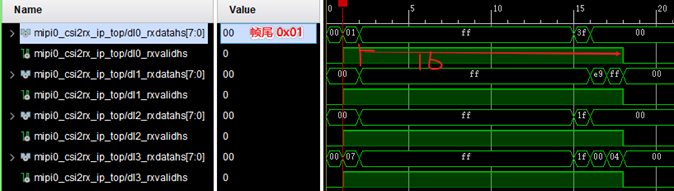

3.5 帧尾DT=0x01

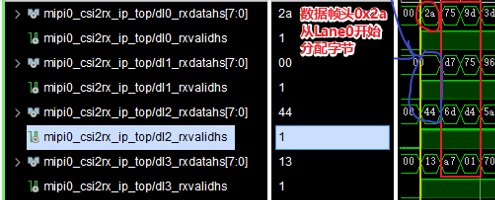

4、数据包分发到lane

按照顺序分发,有的lane可能提前结束。下图中把长包数据头DT=0x2a,长度=0x0044低字节先出,ECC=0x13,分别放入0123lane.

5、总结

- 包头:长短包都有,且有专用的ECC机制(矫正1bit错误,识别2bit错误,包头为重要数据);

- ECC:仅用6bit,其余2Bit可用于扩展虚拟通道VC;

- CRC:仅长包有;

- 长包用于发送图像数据,根据包头WC提取数据长度;

- 短包用于发送帧头/尾,行头/尾。

- 虚拟通道VCID:

- 数据交替:一次传输多种图像格式(用Data ID的两部分VCID,DT都可以区分)

- Xilinx DPHY IP在KU+器件中1.5G时不能调整线路延时,不能使用link training。可使用bitslice(速率1.6G)原语自行设计DPHY,实现延时调整。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?