modelsim安装

软件版本选择

vivado与modelsim软件版本之间有对应关系,仿真前一定要需对工具版本,否则仿真会出现仿真库找不到的问题。vivado版本对应的仿真工具版本如下,详情参见xilinx官网说明。

Vivado Design Suite 2019.2

Mentor Graphics ModelSim SE/DE/PE (2019.2)

Mentor Graphics Questa Advanced Simulator (2019.2)

Cadence Incisive Enterprise Simulator (IES) (15.20.073)

Cadence Xcelium Parallel Simulator (19.03.005)

Synopsys VCS and VCS MX (O-2018.09-SP2-1)

Aldec Active-HDL (10.5a) Aldec Riviera-PRO (2019.04)

Vivado Design Suite 2019.1

Mentor Graphics ModelSim SE/DE/PE (10.7c)

Mentor Graphics Questa Advanced Simulator (10.7c)

Cadence Incisive Enterprise Simulator (IES) (15.20.065)

Cadence Xcelium Parallel Simulator (18.09.005)

Synopsys VCS and VCS MX (O-2018.09)

Aldec Active-HDL (10.5a) Aldec Riviera-PRO (2018.10)

Vivado Design Suite 2018.3

Mentor Graphics ModelSim SE/DE/PE (10.6c)

Mentor Graphics Questa Advanced Simulator (10.6c)

Cadence Incisive Enterprise Simulator (IES) (15.20.053)

Cadence Xcelium Parallel Simulator (18.03.005)

Synopsys VCS and VCS MX (N-2017.12-SP2)

Aldec Active-HDL (10.5) Aldec Riviera-PRO (2018.02)

Vivado Design Suite 2018.2

Mentor Graphics ModelSim SE/DE/PE (10.6c)

Mentor Graphics Questa Advanced Simulator (10.6c)

Cadence Incisive Enterprise Simulator (IES) (15.20.042)

Cadence Xcelium Parallel Simulator (17.10.005)

Synopsys VCS and VCS MX (N-2017.12)

Aldec Active-HDL (10.4a) Aldec Riviera-PRO (2017.10)

当前vivado版本是2018.3,因此选择安装Questasim10.6c版本仿真工具。

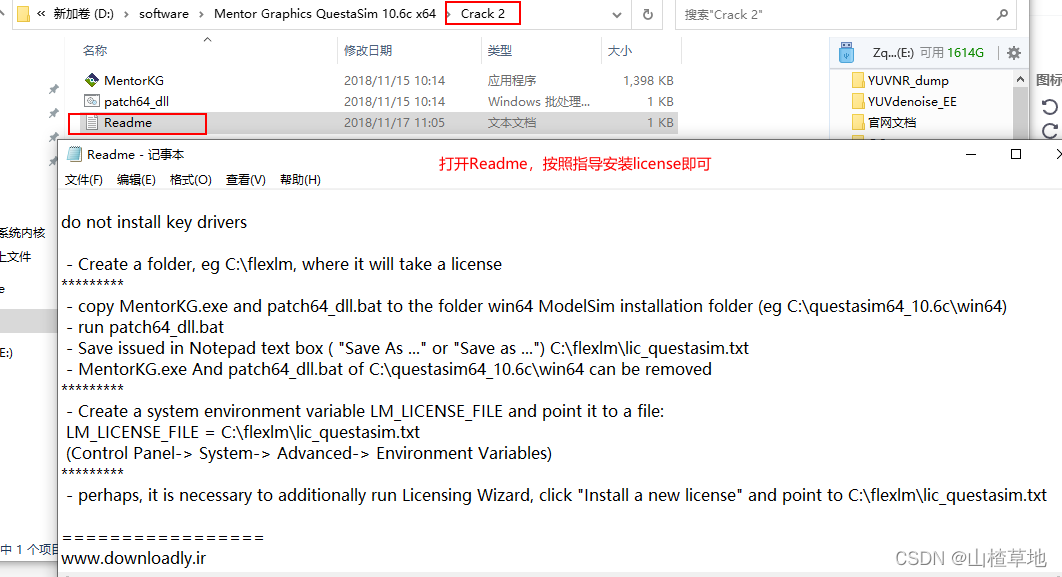

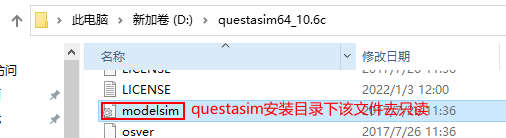

Questasim安装

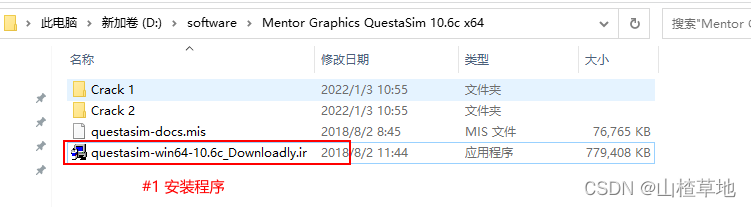

点击安装程序

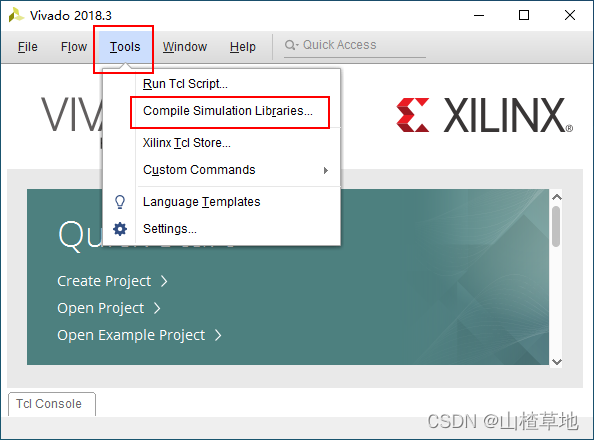

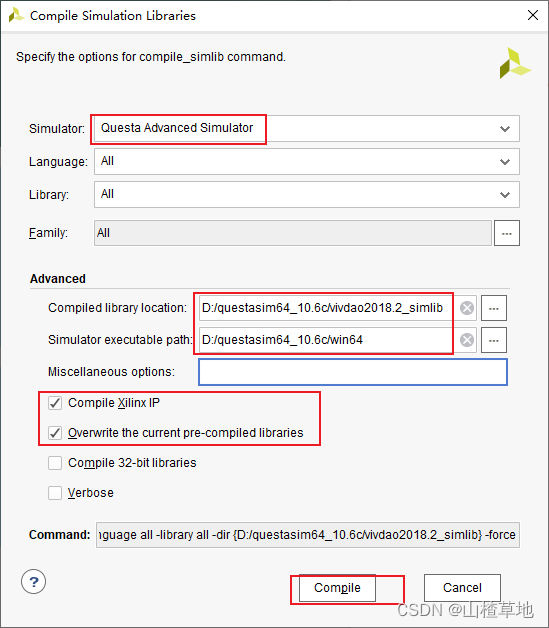

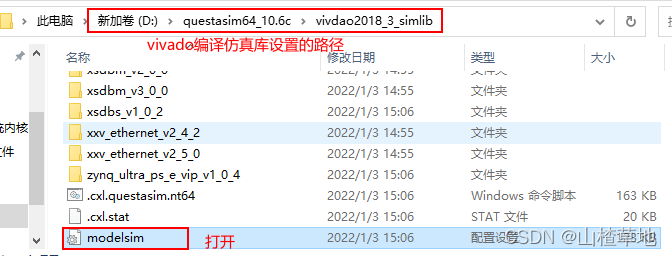

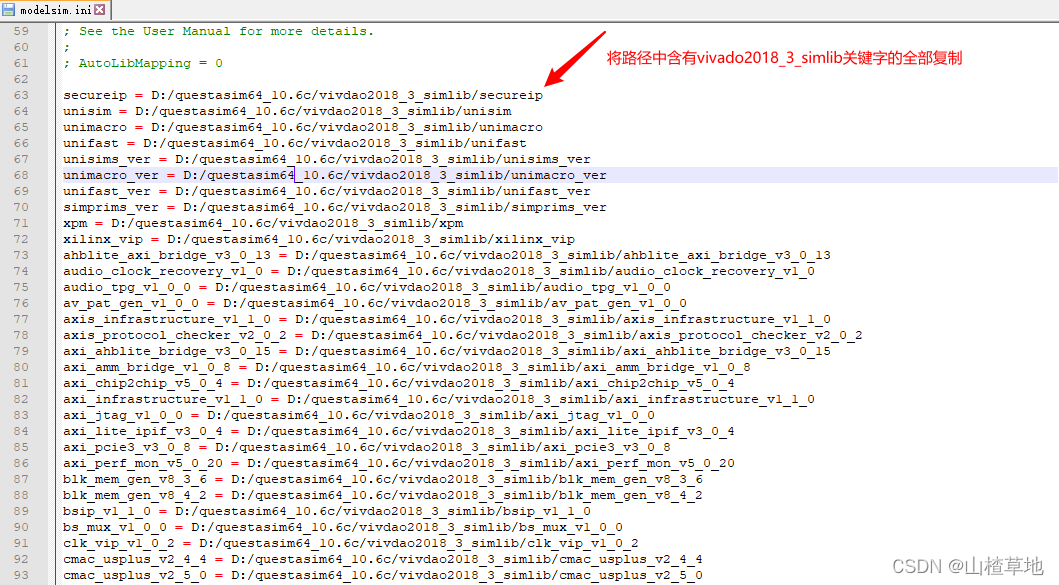

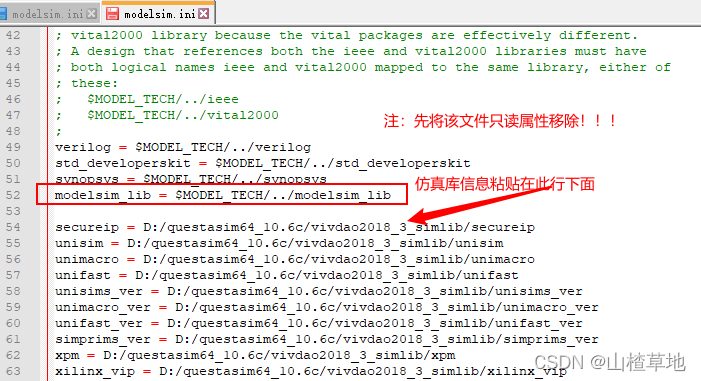

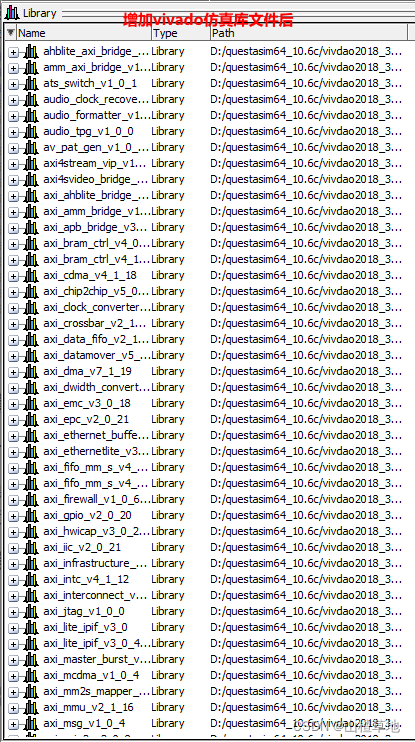

添加vivado仿真库

使用vivado2018.3编译仿真库报错:

[Vivado 12-7080] Failed to find the ‘sccom’ executable path! Trying standard GNU compiler from current installation environment.

官网解释可以忽略该错误:

compile_simlib does not compile any files that require ‘sccom’. As a result, this error can be ignored.

官网

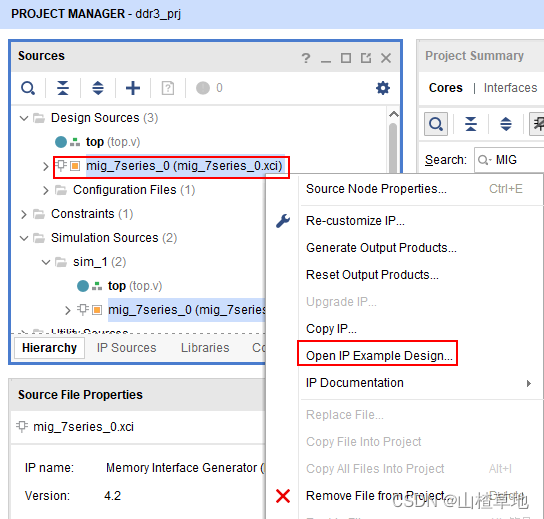

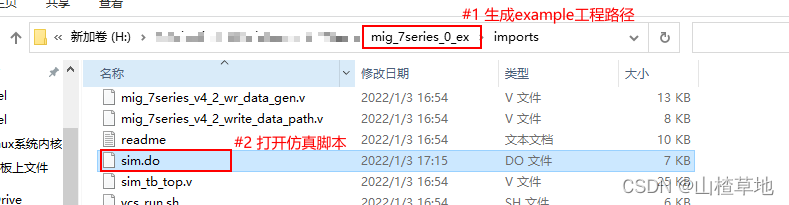

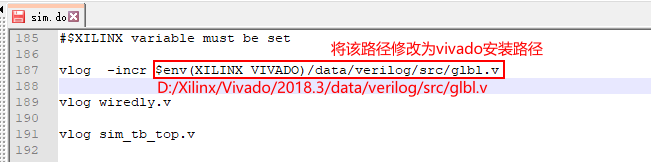

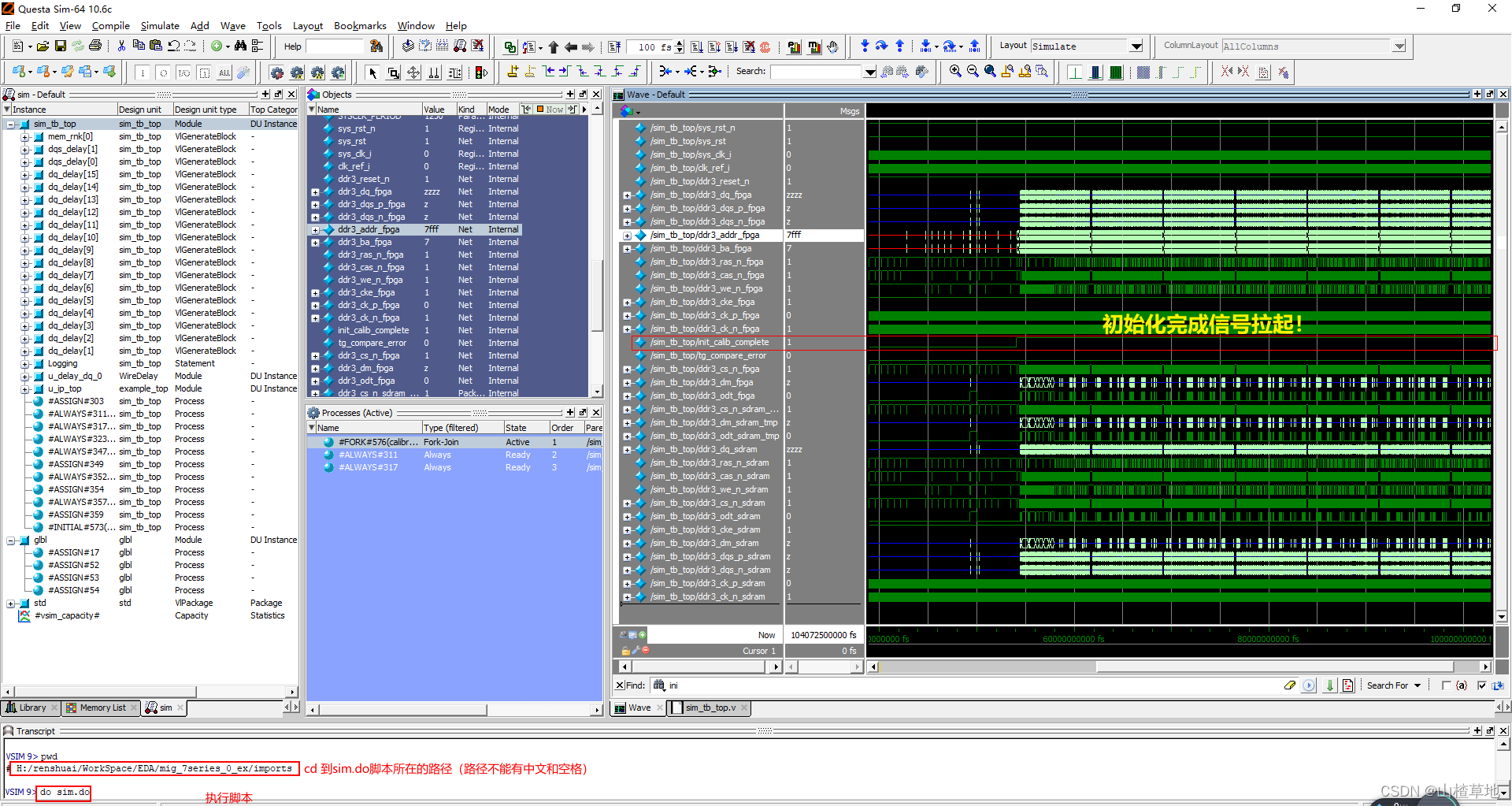

也可以鼠标右键>打开方式>Questasim,工具打开后就是sim.do脚本所在的路径。

注:自己修改平台ddr时,初始化信号无法拉起问题原因ddr3_addr信号位宽少了1bit。

其他IP仿真文件

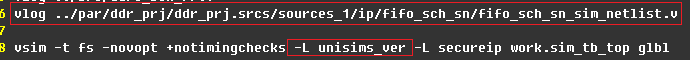

添加FIFO仿真文件

将IP生成FIFO的网表文件加入sim.do脚本中即可:

仿真一般性问题解决方法

1. modelsim仿真PLL输出高阻态问题

原因是在sim.do中将ip下的所有.v都添加,导致文件夹下有个网表.v文件也定义了同一个模块,导致输出时钟为高阻态。将网表.v在sim.do文件中移除即可。

2. 信号波形为X态或高阻态的一般解决办法

- 排查时钟是否ok

- 排查复位信号是否ok

3. DDR仿真读操作多返回一拍无效数据

问题现象:

DDR写地址是连续的,且写入的数据都ok。读地址也是连续的,但是在2个地址返回的有效数据之间夹了一拍无效数据(app_rdata_valid有效数据是乱码)。明显多出来的一拍数据,除去这拍数据前后数据是可以连接上的,且符合预期。

原因:

查看波形发现app_rdy为0时,发起了app_en使能操作。原因是代码实现以app_rdy为条件时序逻辑驱动app_en,导致在app_en上升沿时,app_rdy为下降沿。

修改:

将ddr控制器app侧信号全部用组合逻辑驱动,确保app_rdy高电平时才能驱动app_en信号和其他接口信号。

改进措施:

仿真中应该引进断言的使用,可以快速发现不符合预期的设计,提高问题定位效率。

本文介绍了在Vivado 2018.3版本下,如何选择和安装Questasim 10.6c进行DDR3仿真,并详细阐述了DDR3仿真平台搭建步骤、其他IP如FIFO的添加,以及在仿真过程中遇到的 PLL 输出高阻态、信号为X态或高阻态、DDR读操作异常等问题的解决方法。

本文介绍了在Vivado 2018.3版本下,如何选择和安装Questasim 10.6c进行DDR3仿真,并详细阐述了DDR3仿真平台搭建步骤、其他IP如FIFO的添加,以及在仿真过程中遇到的 PLL 输出高阻态、信号为X态或高阻态、DDR读操作异常等问题的解决方法。

3468

3468

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?