I2S

I²S(Inter-IC Sound)是一种用于数字音频设备之间传输音频数据的串行总线接口标准。它由飞利浦(现为恩智浦半导体)在1986年提出,主要用于集成电路(IC)之间的音频数据传输。I²S广泛应用于消费电子产品,如音频编解码器、数字信号处理器(DSP)、微控制器和音频放大器等。

I²S的主要特点

-

串行传输:I²S使用串行通信方式传输音频数据,减少了引脚数量,简化了硬件设计。

-

立体声支持:I²S支持立体声传输,可以同时传输左右声道的数据。

-

高音质:由于是数字传输,I²S能够提供高保真的音频信号,避免了模拟传输中的噪声和失真问题。

-

同步传输:I²S使用主从模式,主设备生成时钟信号,从设备同步接收数据,确保数据传输的准确性。

I²S的信号线

I²S总线通常由以下三条信号线组成:

-

SCK(Serial Clock):串行时钟信号,由主设备生成,用于同步数据传输。时钟频率通常为采样频率的倍数(如32倍、64倍等)。

-

WS(Word Select):字选择信号,用于指示当前传输的是左声道还是右声道的数据。WS信号的电平变化表示声道切换。

-

SD(Serial Data):串行数据信号,用于传输音频数据。数据在SCK的上升沿或下降沿进行采样。

I²S的数据格式

I²S传输的音频数据通常是PCM(脉冲编码调制)格式,每个采样点用一定位数的二进制数表示。常见的位数为16位、24位或32位。数据格式如下:

-

左声道数据:WS为低电平时传输。

-

右声道数据:WS为高电平时传输。

数据在SCK的每个时钟周期传输一位,从最高有效位(MSB)开始传输。

I²S的工作模式

I²S支持多种工作模式,常见的有:

-

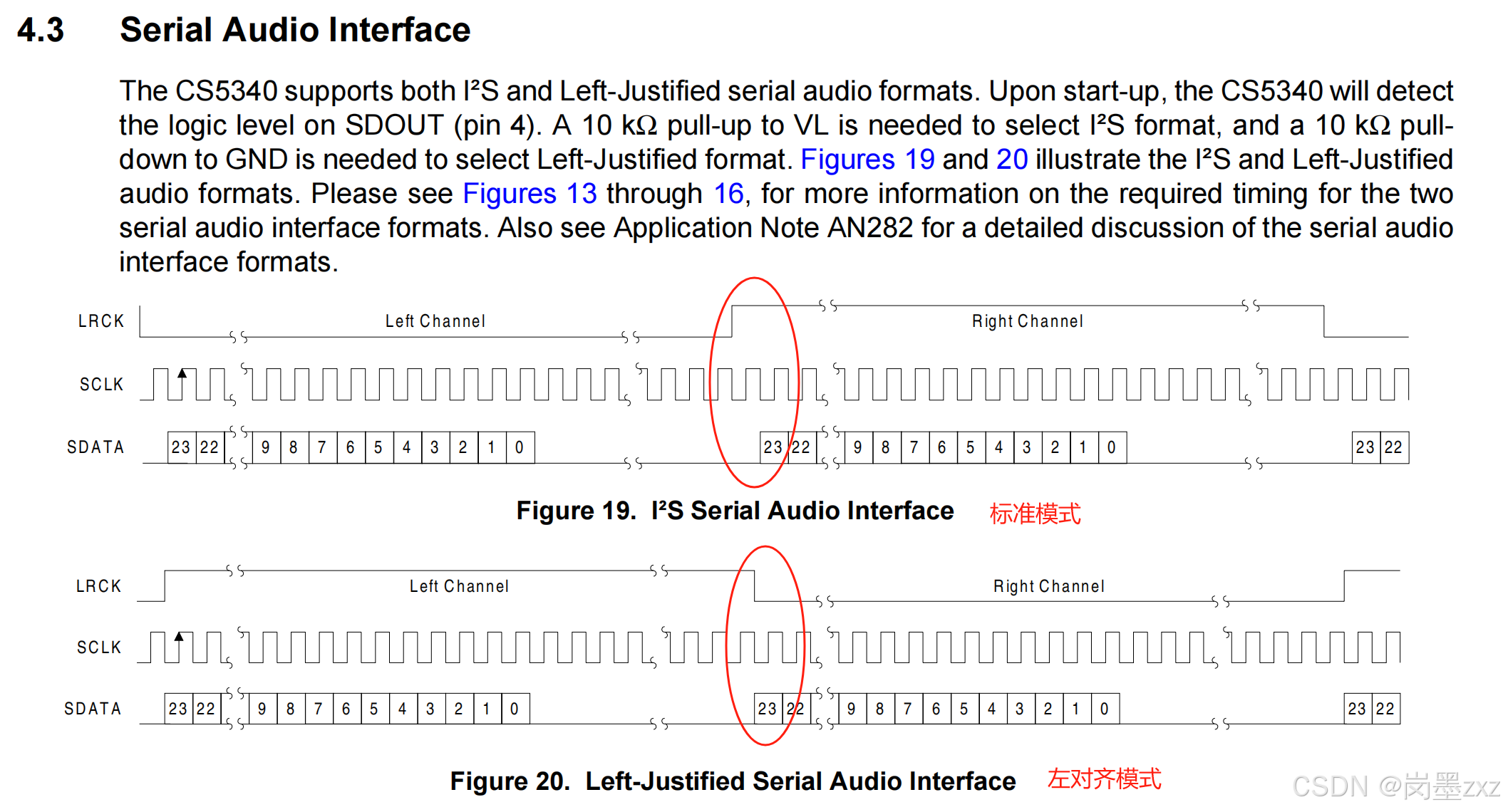

标准模式:数据在SCK的上升沿采样,WS信号在SCK的下降沿变化。

-

左对齐模式:数据在SCK的上升沿采样,WS信号在SCK的上升沿变化。

-

右对齐模式:数据在SCK的上升沿采样,WS信号在SCK的上升沿变化,但数据对齐方式与标准模式不同。

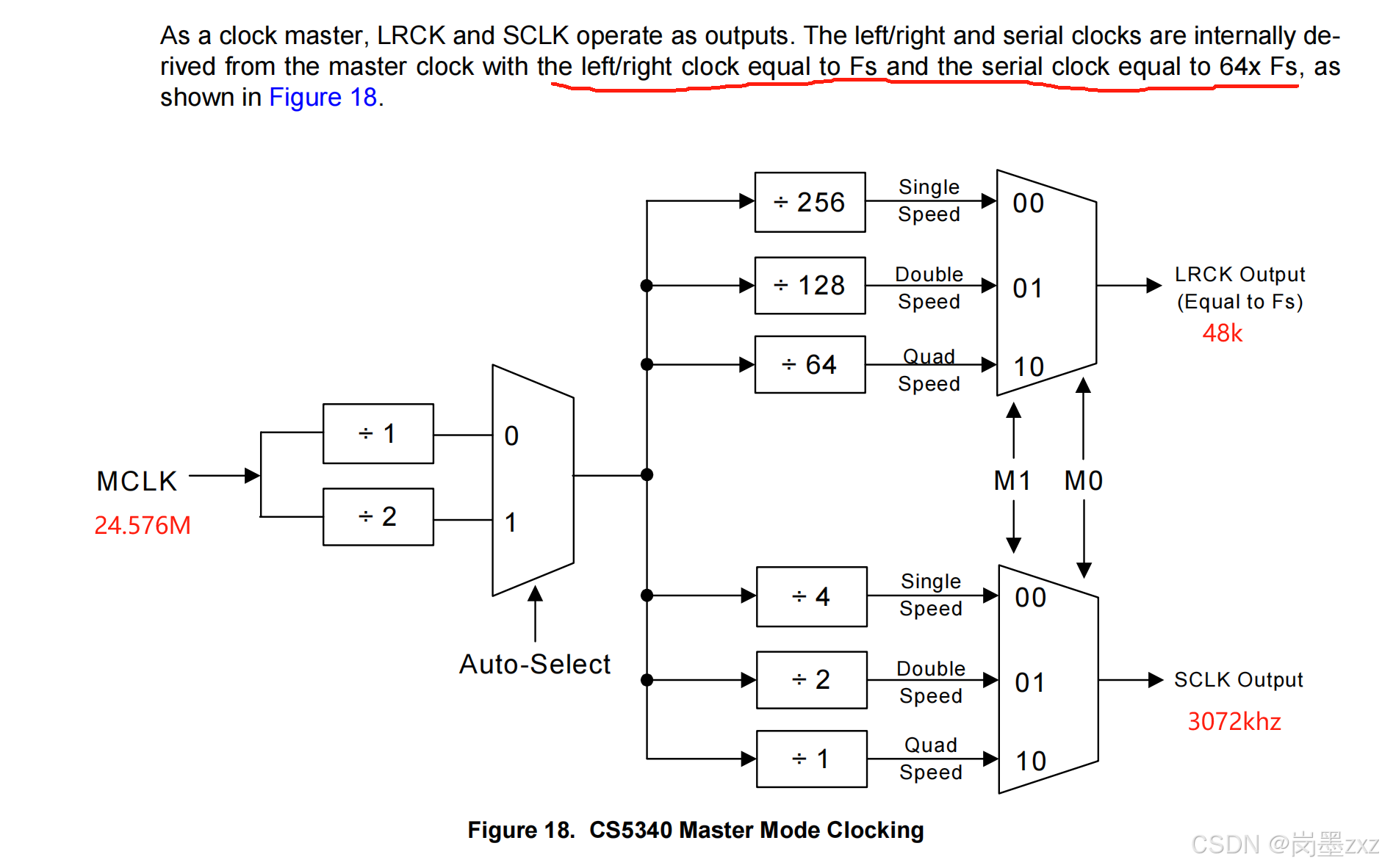

时钟

采样率

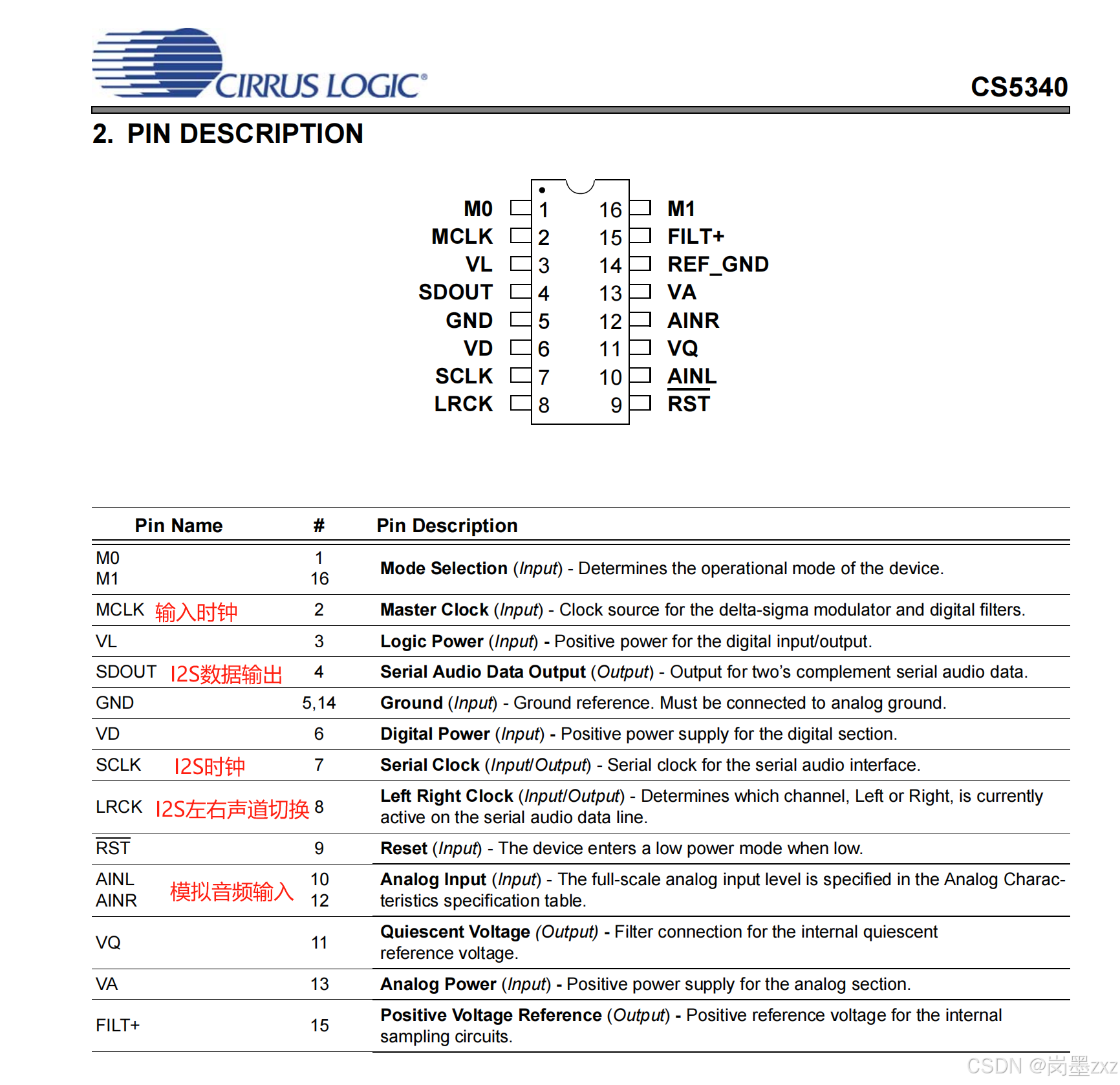

48K采样率,左右时钟48k,串行时钟3072k,64倍关系,对应64bit串行数据,左声道32bit,右声道32bit

位深

标准支持32bit,CS5340芯片为24bit

其他

I2S和I2C没有关系

I2S中串行数据以二进制补码的形式传输

二进制补码的定义

对于一个n位的二进制数,补码表示法的规则如下:

-

正数:与原码相同。例如,8位二进制中,+5表示为

00000101。 -

负数:通过对该数的绝对值取反(逐位取反)再加1得到。例如,-5的8位补码表示为:

绝对值:00000101取反:11111010加1:11111011

补码的特点

-

唯一性:每个数有唯一的补码表示。

-

符号位:最高位为符号位,0表示正数,1表示负数。

-

范围:n位补码的范围是-2^{n-1}−2n−1到2^{n-1}-12n−1−1。例如,8位补码的范围是-128到127。

在I2S系统中,提供时钟(SCK和WS)的设备为主设备

AES

AES/EBU接口标准

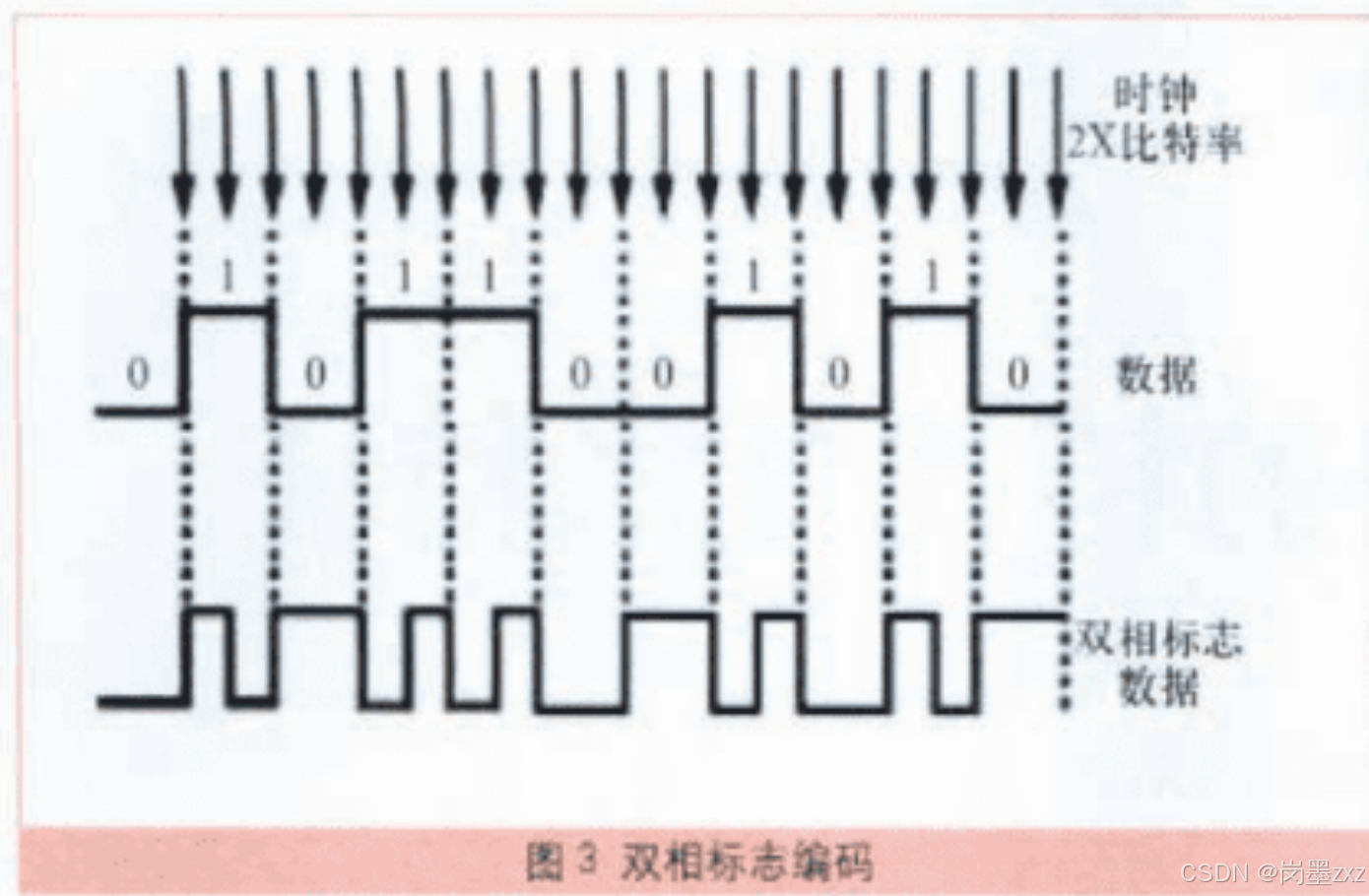

AES和EBU一起开发的数字音频传输接口标准,AES/EBU标准,即AES3-1992,ANSI S4.40-1992,或IEC-958标准。它是传输和接收数字音频信号的数字设备接口协议,规定音频数据必须以2的补码进行编码。传输介质是电缆,允许高带宽容量和并行数据字节的串行传输,串行传输16到20bit的字节时先传输最低有效位。串行后的数据流经格式化器加入字节时钟标志以表明每个样值的开始。格式化后的串行数据流经双向标志码编码器编码后输出,最后传输的数据流为双相标志码码流。

AES/EBU编码器框图和并串转换

AES/EBU接口数据结构

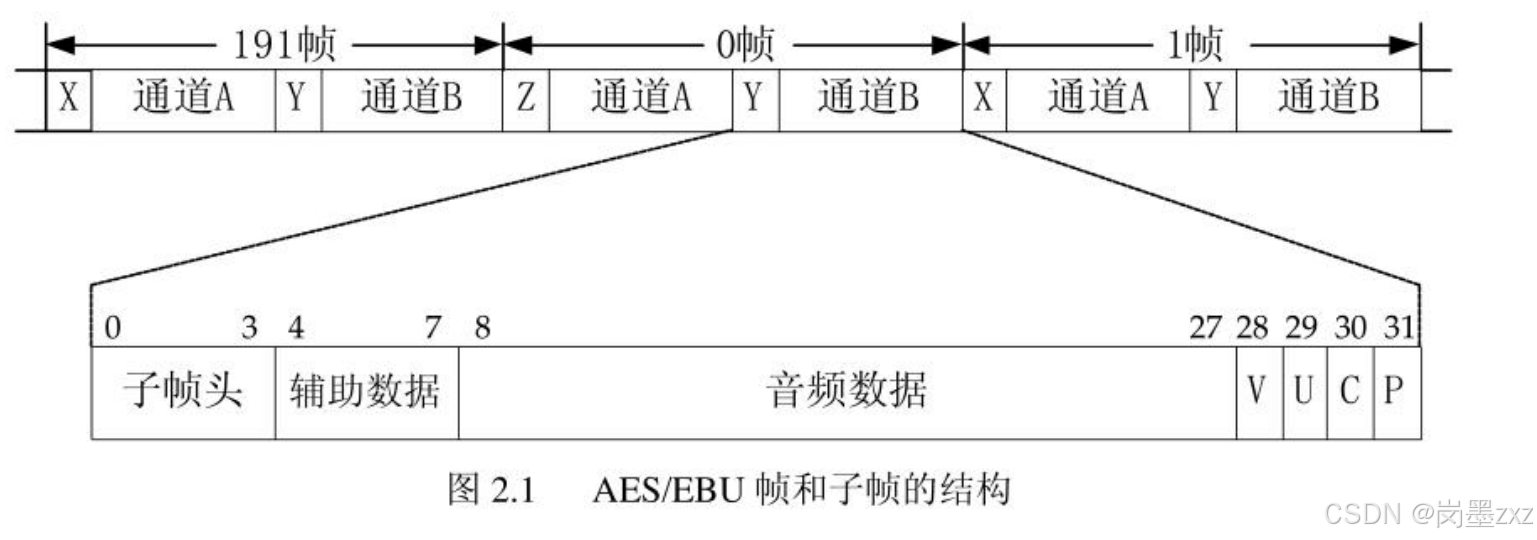

AES/EBU信号的基本数据包是帧(不同于视频信号中帧的概念),一个音频帧包括两个32比特的子帧(子帧1和子帧2)(1个子帧=1个抽样)

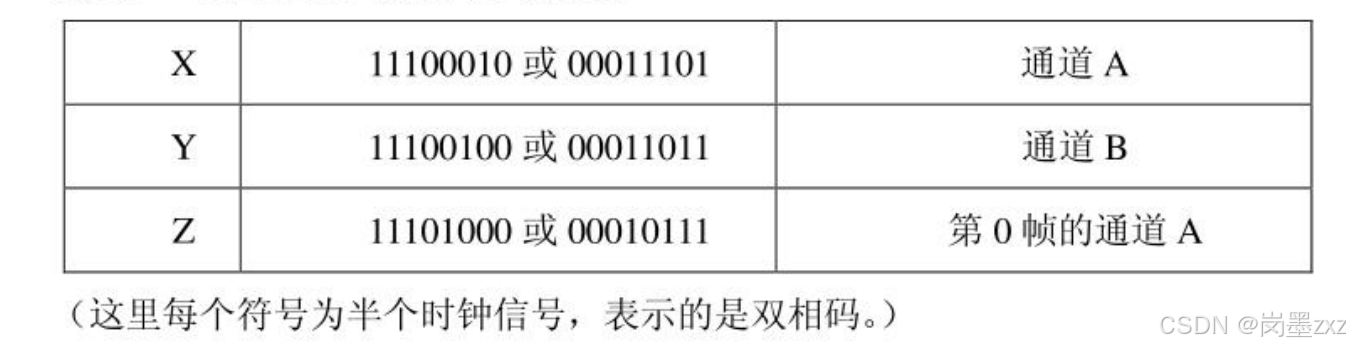

如图第0帧中子帧1为Z+通道A,子帧2为Y+通道B。

一个子帧包括一个音频声道32比特

1、同步数据(子帧的首标):4个比特

X、Y、Z都是子帧头的表示符号,相当于同步信息。每帧的第一个子帧的头用X表示,第二个用Y表示,但是第0帧的第一个子帧头要用Z表示,以表示一个快的开始。

2、辅助数据:4个比特

标准提供24bit放音频数据,实际产品大多数用20bit,所以辅助数据4bit一般用不到

3、音频数据:20比特

有效音频数据

4、有效比特(V):1比特

有效比特(V):样值数据是音频且可进行D/A转换,则此比特置0。否则样值有问题,接收设备将输出静音。

5、用户比特(U):1比特

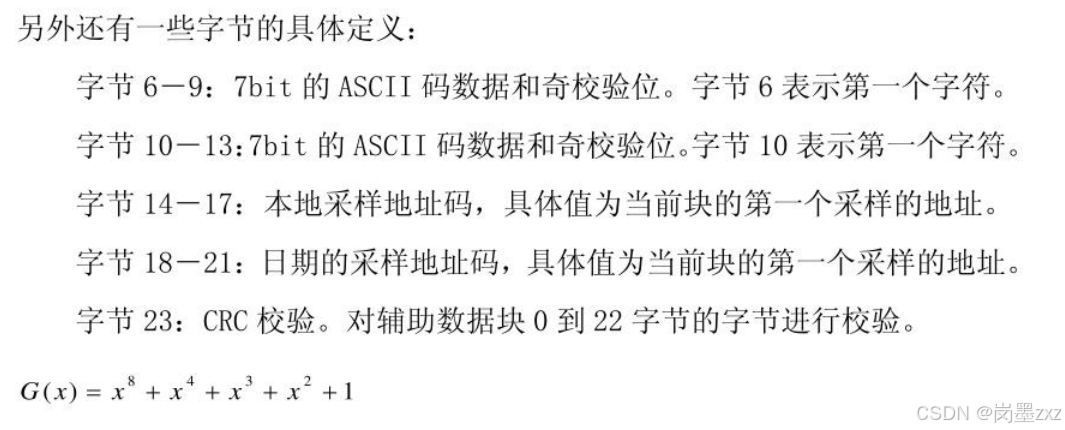

用户比特(U):送至一个28×8bit的存储器。一个音频块中每个声道有192个子帧,因而该存储器中有192个用户比特。

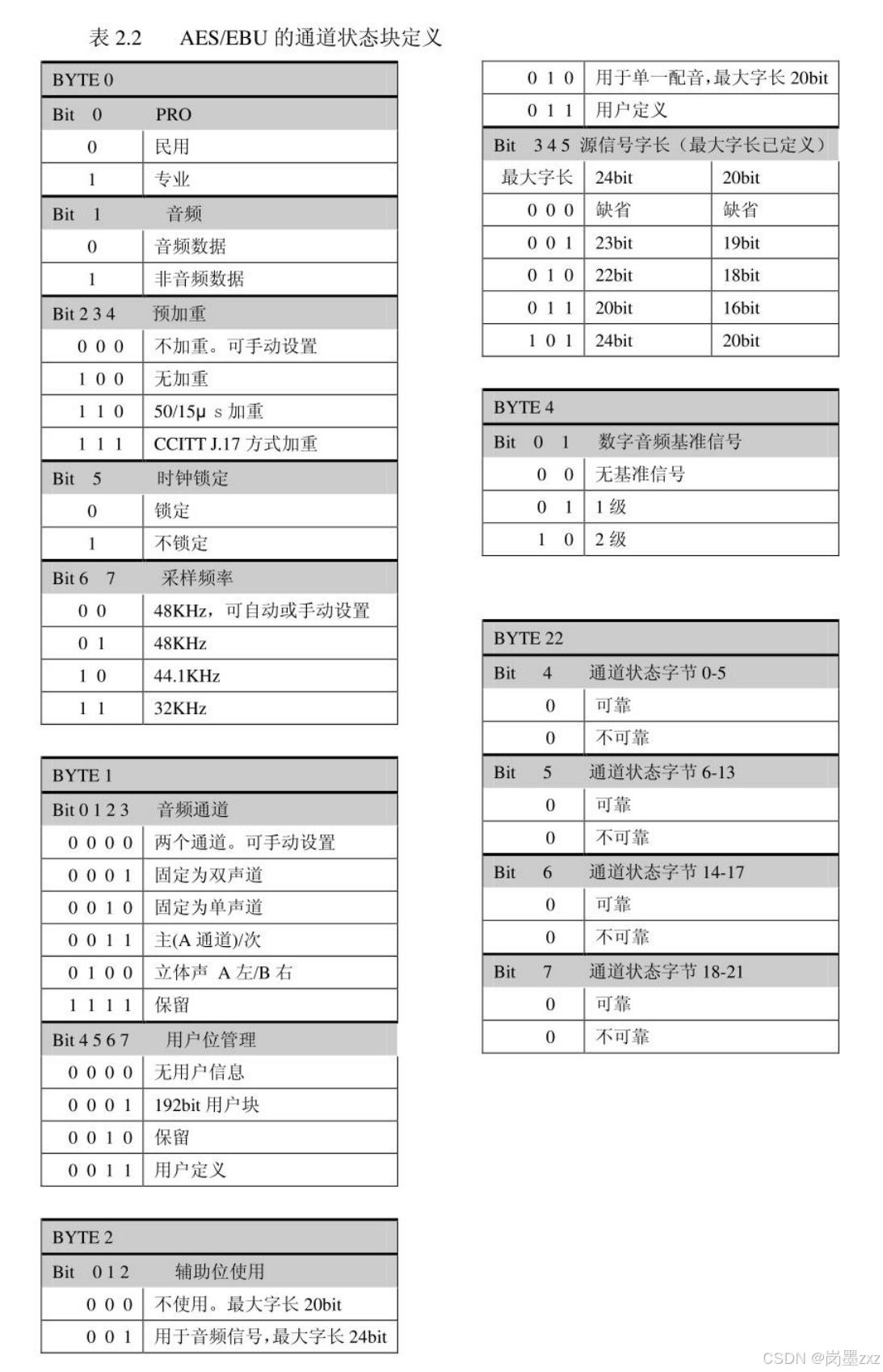

6、声道状态比特(C):1比特

通道比特(C):送到一个28×8bit的通道状态存储器。此比特对于音频数据内容的标识非常重要。

通道状态存储器描述了在AES/EBU数据流通道中比特分配及其含义。

7、奇偶校验比特(P):1比特

奇偶校验比特(P):通常为偶校验。偶校验确保在一个子帧的64个双相标志码元中1的数目是偶数。奇偶校验比特可以检测在传输中发生的奇数个错误。一些设备忽略此比特或者没有正确地处理这种标识。

AES/EBU 取样频率

量化比特16-20bit,取样频率30-50khz,通常采用32kHz,44.1kHz,48kHz三种,44.1kHz用在CD音质,48kHz用在广播电视领域较多。AES实际建议采样频率为48khz。

AES/EBU 数据特性

每192个音频帧构成一个块,在数据流中用标志符Z标识每个块的开始,建议抽样频率为48Khz,在一个48kHz抽样的系统中每个音频帧的时间是20.83um,一个块的时间为20.83us×192= 4000us,250个块构成4000ms x 250=1s。

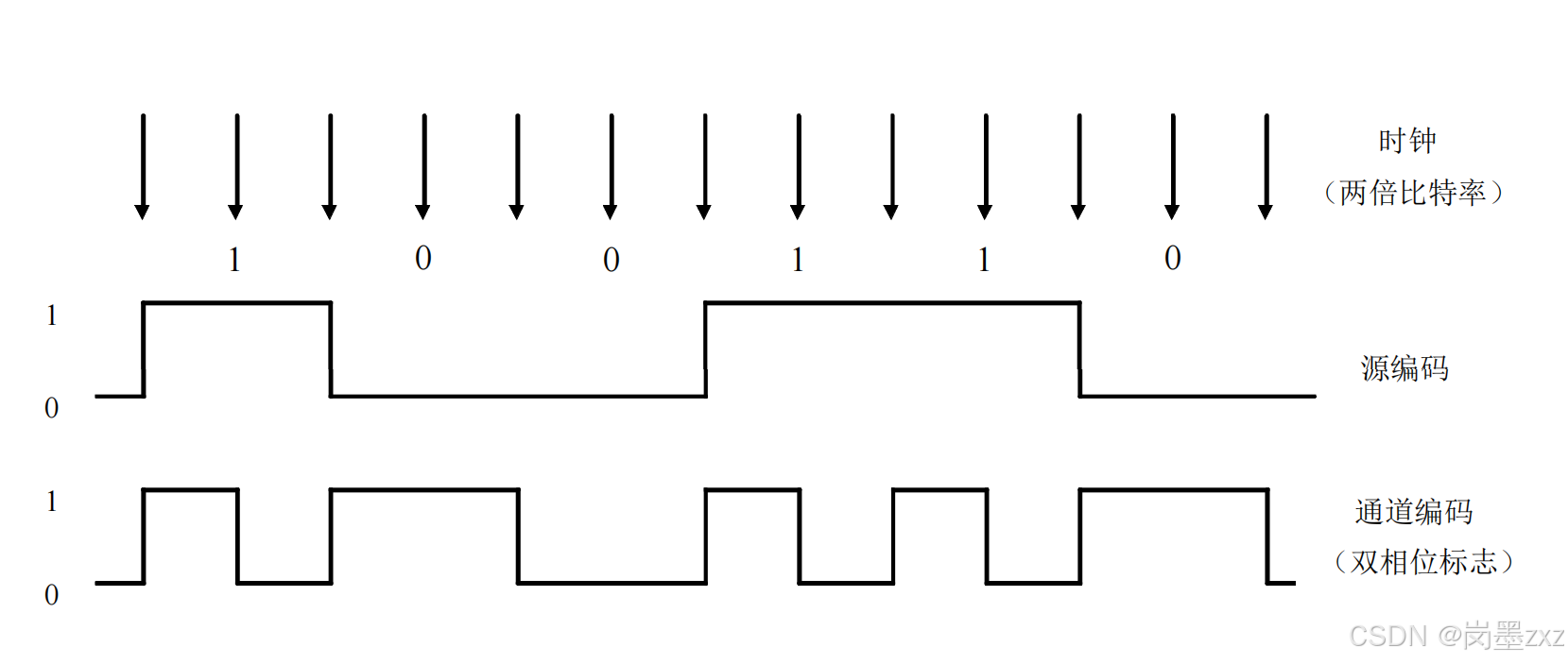

抽样频率为48kHz时总数据率为32×2×48000=3.072Mbps。在双相标志码编码后,数据传输率提高到两倍,6.144Mbps。双相标志码的频谱能量在6.144MHz的倍频处为0。

同步字包括三个低单元和随之而来的三个连续的高单元。在AES/EBU信号频谱中占据一个低的基频,3.072/3=1.024MHz。每个音频帧包括64bit,每20.83us发出一帧,帧中的一个数据比特持续时间为325.5ns,一个双相标志码比特单元时间为163ns,由一些数据流比特叠加产生的眼图眼宽时间为163ns。

AES/EBU 双向标志码编码

AES/EBU接口的电特性

发送端平衡输出

XLR插头

1:GND

2:信号(极性不要求)一般为+

3:信号(极性不要求)一般为-

输出阻抗:110R

不平衡度:<-30db(到6Mhz)

输出信号幅度:在110R负载上2-7Vpp(平衡)

上升和下降时间:5-30ns

抖动:20ns

接收端平衡输入

XLR插头

1:GND

2:信号(极性不要求)一般为+

3:信号(极性不要求)一般为-

输入阻抗:110R

共模抑制比:最高7Vpp,20khz

最大可接受信号电平:7Vpp

电缆规范:屏蔽双绞线,最长100-200米

电缆均衡:可选

1703

1703

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?