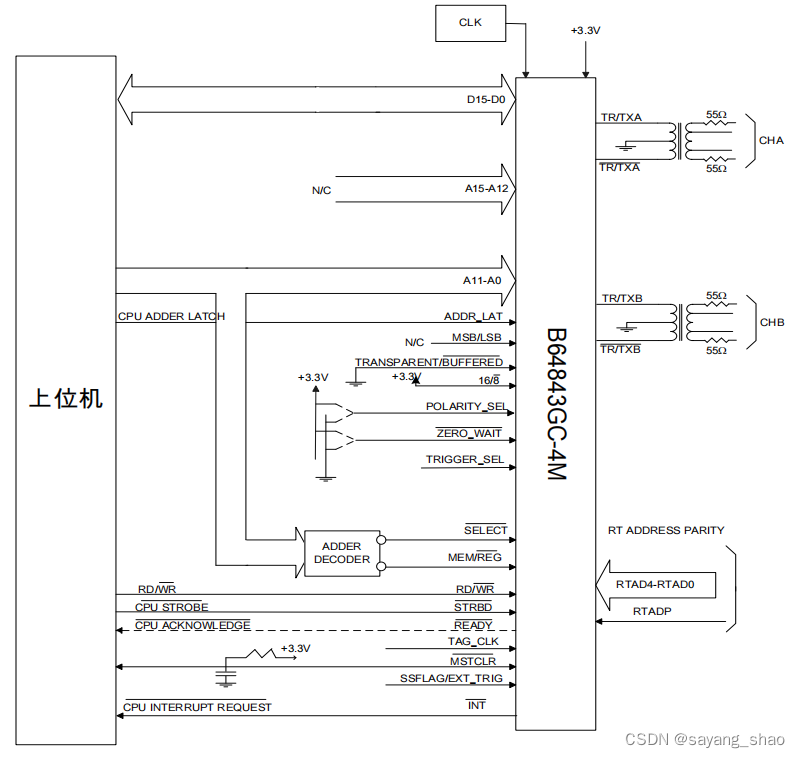

B64843-4M系统架构

注:1、CPU ADDRESS LATCH 信号由带地址/数据复用总线的处理器提供,对不带地址/数据复用总线的处理器,CPU ADDRESS LATCH 信号与 3.3V 信号连接。

2、如果 POLARITY_SEL="1",RD/信号为高时读使能,为低时写使POLARITY_SEL="0"则相 反。

3、ZERO_WAIT 为"1"表示非零等待模式,为“0”表示零等待模式。

4、CPU ACKNOWLEDGE 信号只在非零等待模式有效。

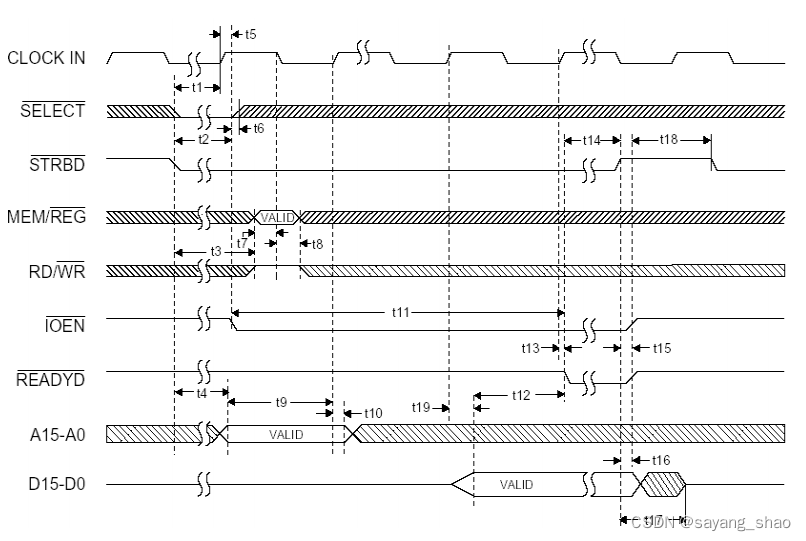

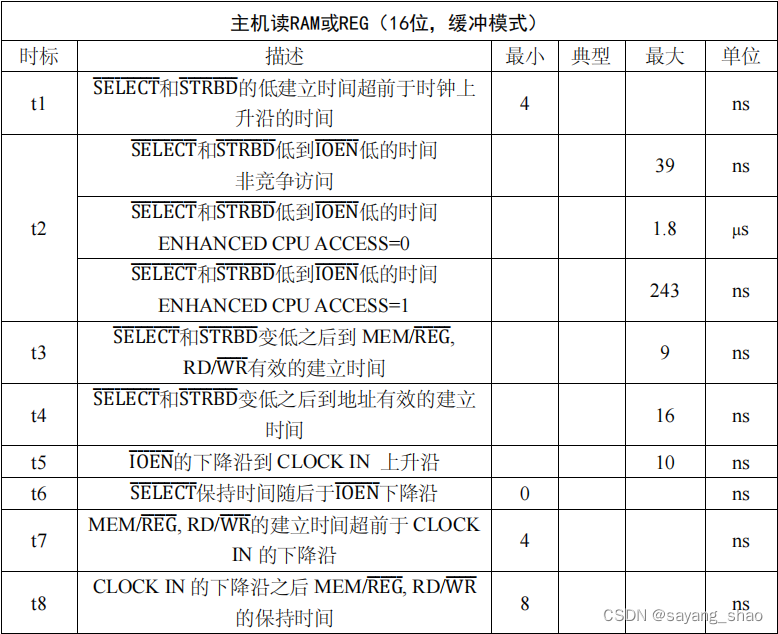

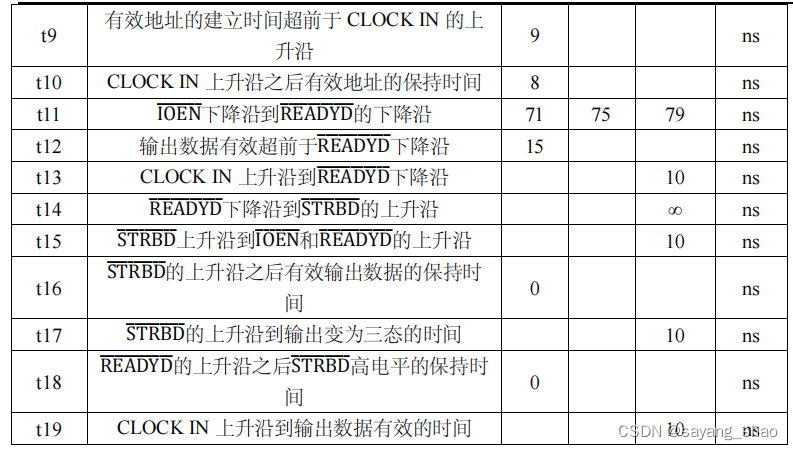

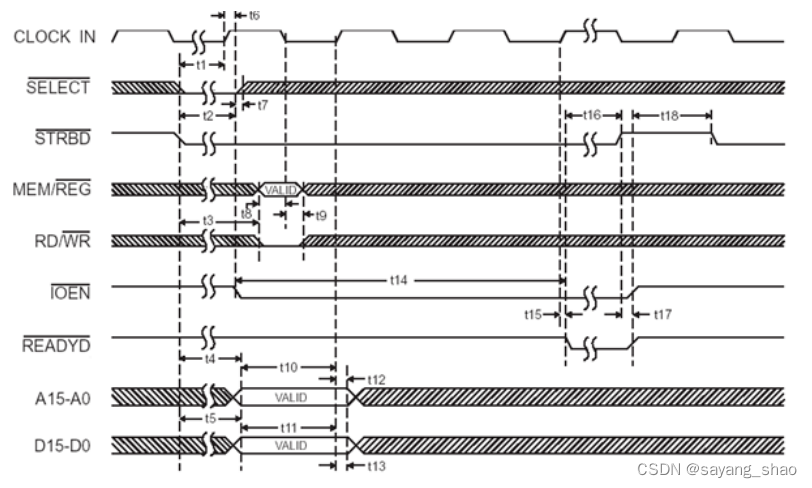

主机读RAM或REG(16位,缓冲模式)

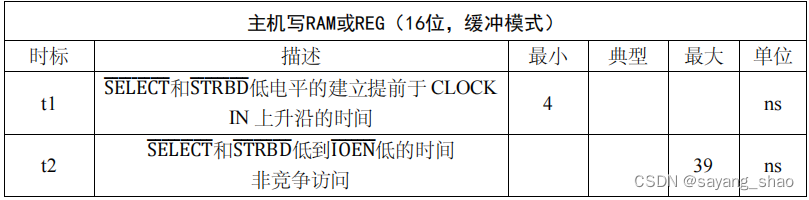

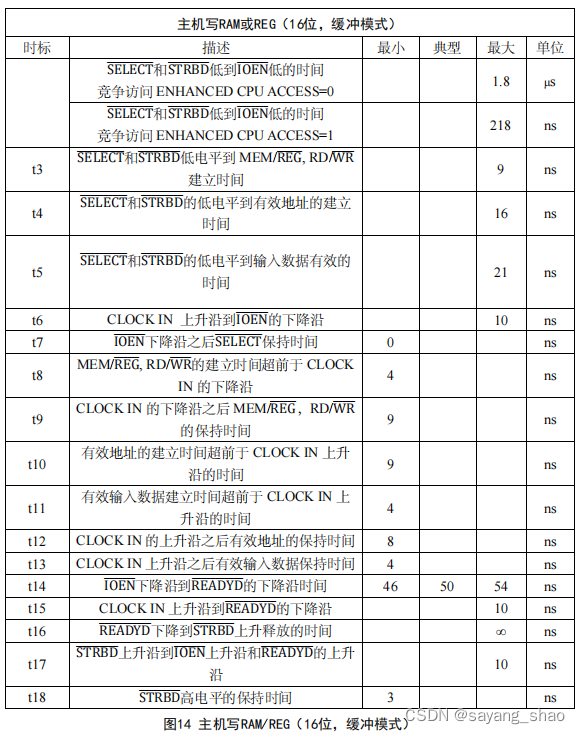

主机写RAM或REG(16位,缓冲模式)

寄存器说明

中断屏蔽寄存器

#1

和

#2:用于使能或禁止各种事件和条件的中断请求。

配置寄存器

#1

和

#2

:主要用于选择电路的操作模式,软件控制 RT 状态字的各个位,

激活存储器空间,BC 消息错误停止,选择 RT 存储器管理模式以及控制时标操作等等。

开始

/

复位寄存器:主要用于“命令”类型的函数,比如软件复位,BC/MT 模式的启动,

中断复位,时标复位,时标寄存器测试,初始化协议自测试,初始化 RAM 自测试,清除自

测试寄存器和清除 RT 停止命令。同时在自动重发模式下,它还能规定 BC 在当前消息发完

或当前信息帧发完的情况下停止。

BC/RT

命令栈指针寄存器:电路在 BC/RT 模式下,用于主机确定当前消息或最近的消

息在存储器中的指针位置。

BC

指令表指针寄存器:通过读该寄存器确定增强 BC 模式下指令指针的当前位置。

BC

控制字

/RT

子地址控制字寄存器:在 BC 模式下,主机可以访问当前 BC 控制字寄

存器。BC 控制字包含的位有:选择激活总线,消息格式,使能掉线自测试,屏蔽状态字位,

使能消息重试和中断,以及指定 MIL-STD-1553A 或 MIL-STD-1553B 出错处理等。在 RT 模

式下,主机能够访问当前或最近的子地址控制字。子地址控制字用于选择存储器空间配置方

式和使能当前消息的中断。

时标寄存器:能够保存实时时钟的值,该寄存器的分辨率可编程为 2,4,8,16,32

和 64μs/LSB。在 BC、RT 和消息监视模式下,消息的起始(SOM)和消息的截止(EOM)

均能促使时标寄存器的当前值写入 RAM 的栈空间。

中断状态寄存器

#1

和

#2:主机能通过一到两个读操作来判断产生中断的原因。两个中

断状态寄存器的中断事件分别映射到两个中断屏蔽寄存器中的相应位。中断状态寄存器#2

中还包含一个中断链(INTERRUPT CHAIN)位,用来指示中断状态寄存器#1 中相应的中

断事件。

配置寄存器#

3

,

#4

和

#5:通过配置这些寄存器可以使能电路的许多先进特性。在 BC、

RT 和 MT 模式下,利用增强模式可以使能配置寄存器 1 中的各只读位。在 BC 模式下,增

强模式特性包括扩展 BC 控制字和 BC 块状态字,错误停止(SOE)和状态停止(SOS)重

置函数,帧自动重试,可编程消息时间间隔,消息自动重发,状态字屏蔽和完成消息发送后

产生中断的能力等。在 RT 模式下,增强模式的特性包括扩展 RT 块状态字,RT/可选择监测

联合模式,循环测试失败时自动重置终端标记(TERMINAL FLAG)状态字,单个接收(广

播)子地址的双缓冲结构,以及交替(完全软件编程)RT 状态字。在 MT 模式下,增强模

式可以使能可选择消息监测,RT/可选择监测联合模式,以及监测触发的能力。

RT/MT

数据栈地址寄存器:为 RT 或 MT 模式存储的上一个数据字提供读/写的指示。

BC

帧时间保持寄存器:为当前 BC 信息帧保留时间提供只读标志。在增强模式下,该

计时器可能用于主从帧控制,或作为 BC 消息序列控制处理器的看门狗使用。该寄存器的计

时分辨率为 100μs/LSB。

BC

消息时间保持寄存器:用于只读标识在一个 BC 帧中消息与消息之间的保持时间。

在增强模式下,该计数器还可作为 BC 消息序列控制处理器的延时(DLY)指令,或主从帧

控制。寄存器的计时分辨率为 1μs/LSB。

BC

信息帧

/RT

上一个命令字

/MT

触发字寄存器:在 BC 模式下,该寄存器用于在帧自

动重试模式下配置 BC 信息帧的时间。其计时分辨率为 100μs/LSB,最大计时数为 6.55 s。

在 RT 模式下,该寄存器用于存储 RT 处理的当前或最近的 1553B 命令字。在 MT 模式下,

该寄存器用于指定一个 16 位的触发(命令)字,该触发字用于启动或停止 MT,或用于产

生中断。

BC

初始化指令指针寄存器:使能主机为增强 BC 指令列表分配起始地址。

RT

状态字寄存器和建立测试(

BIT

)字寄存器:提供 RT 状态字和建立测试字的只读

标识。

配置寄存器

#6

和

#7:用于激活与 J61580R 电路结构相比新增加的特性。这些特性包括:

BC 增强模式,RT 全局循环缓冲(包含缓存大小),RT/MT 中断状态序列(包括有效和无效

的消息滤波),使能 RT 地址的软件分配,时钟频率选择,存储器无数据区基地址,为同步

(无数据)时间标记操作的最低有效位滤波,使能增强 BC 模式序列控制引擎的看门狗时钟。

BC

条件码寄存器:使能主处理器读 BC 增强消息序列控制引擎条件标志的当前值。

BC

通用标志寄存器:允许主处理器重置、清除或反转增强 BC 消息序列控制引擎的任

意通用条件标志。

内建自测试状态寄存器:提供协议状态和 RAM 内建自测试状态的只读访问。

BC

通用序列指针:为 BC 增强模式提供初始化通用序列指针的方法。使能主处理器确

定通用序列指针的当前位置,该指针通过增强消息序列控制引擎内部递增。

RT/MT

中断状态序列指针:为 RT、MT 和 RT/MT 模式提供初始化中断状态序列指针

的方法。使能主处理器确定中断状态序列指针的当前位置,该指针通过 RT/MT 消息处理。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?