一. 这么学DSP比较有效

在开始C6678的架构讲解之前,我想拉出一点篇幅,给大家谈一下,根据我个人的理解,怎么样才能比较快的学好DSP。

(1)学习DSP,首先要与学MCU区分开,毕竟这是两个完全不同的架构,而且DSP与MCU的设计思路完全不一样。MCU是为通用的控制而设计,DSP则是专为高速应用而设计;

(2)从硬件的角度来考虑,要玩转DSP,首先需要仔细阅读其数据手册和用户指南。数据手册中,重点阅读DSP的技术指标,最关键的是对芯片的电源需求做详细的了解,其中对核电压的需求一定要认真了解,这是DSP稳定运行的基本条件;做硬件设计的人,电源设计是最基本的,不仅要考虑电源的电压,更重要的是要考虑电源的抗跌落性能、动态性能。尤其在DSP使用场合,高速电路对电源的要求尤其苛刻,尤其是对于上电时序需要特别注意 ;

(3)在对DSP芯片的电源需求做了深入的了解后,下一步就是要仔细阅读如何启动DSP,前面说了,DSP与MCU不一样,但是有一点又是非常相似的,就是DSP跟MCU一样,需要明确的设置好启动的选项。因为DSP是独立的高速信号应用,DSP的控制程序和算法都是独立的存储在独立的存储空间。所以如何根据产品的需求进行启动的配置,这是非常重要的;

(4)在了解了DSP的启动选项后,还有一个需要密切关注的,就是对于晶体或者TCXO等等的选择,这一点为什么要提出来,本人是做无线通信的,做基站或者终端,都必须根据网络的需要,确定你需要的系统基准时钟的技术指标,如果你选择的晶体或者TCXO等等指标落后于你的网络系统的需要,那么在使用和测试的过程中,将会出现失步的问题。无线通信最严重的通信故障就是失步。尤其是我们国家推行的TD-SCDMA以及TDD-LTE都对网络的同步提出了极为苛刻的要求,在做DSP设计时,尤其需要对DSP的输入时钟根据系统的性能需要,做特别的处理 ;

(5)对于高速DSP,比如我们接下来要讲的8核高速DSP TMS320C6678而言,一个至关重要的硬件设计,就是存储器的设计。尤其是随着性能的提高,都已经从DDR2升级到DDR3了,为了追求极速的性能,一定要考虑存储器的拓扑结构;

(6)进行DSP的产品实际设计前,建议优先采用DSP芯片厂家推荐的开发板或者评估板,做一些技术的准备,从这些开发板的设计资料中,体会设计中需要关注的地方。尤其是8核的TMS320C6678的设计,更加需要关注。这里我提醒大家,做TMS320C6678的设计,最好不要完全按照自己以前的经验进行,一定要按照参考设计进行;

(7)作为DSP软件工程师来说,比硬件工程师就要幸福多了。DSP的软件,与目前主流的MCU差不多,同样也要细分为驱动程序,LINUX,算法以及应用开发等等。对于LINUX的应用和驱动的开发,这里就不说了。重点给大家提示驱动开发需要注意的问题,在LINUX或者ANDROID开发中,有很多的驱动软件,但是DSP的驱动软件开发,需要下的功夫要多得多。除了大家都关心的驱动通用技术,更重要的是鲁棒性;

二.多核DSP的架构

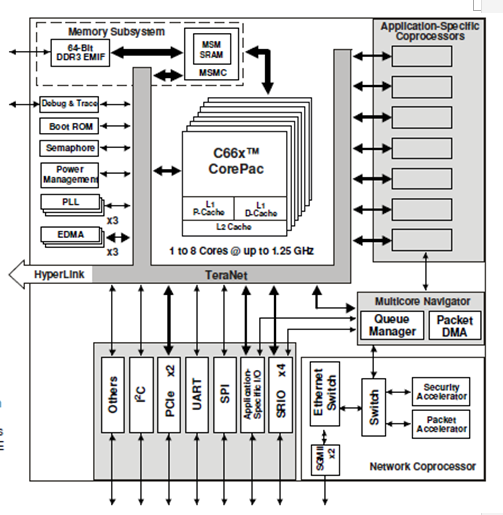

TMS320C6678是KeyStone架构的8核DSP处理器,每个CorePac核的频率最高为1.25 GHz,提供强大的定点和浮点运算能力,同时芯片内部集成了Multicore Navigator、RapidIO、千兆以太网和EDMA等外设,由于芯片处理能力强,外设功能丰富,而且片内集成了大量的硬件加速器,例如Packet Accelerator、Multicore Navigator等,可以广泛地应用在通信、雷达、声纳、火控、电子对抗等领域。从目前的情况看,由于C6678的以上优异的特性,基于TMS320C6678的硬件和软件平台,在未来的5~10年内,将是信号处理平台主流。

TMS320C6678有8个C66x核,典型速度是1GHz,每个核配置为:

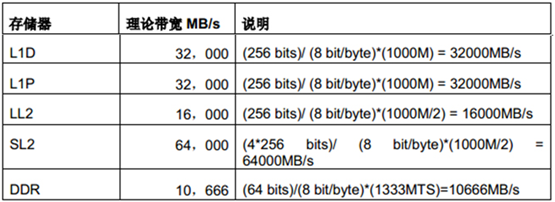

32KB Level 1 Data SRAM,它和DSP 核运行在相同的速度上,可以被用作普通的数据存储器或数据cache;

32KB Level 1 Program SRAM, 它和DSP 核运行在相同的速度上,可以被用作普通的程序存储器或程序cache;

512KB LL2 SRAM, 它的运行速度是DSP 核的一半,可以被用作普通存储器或cache,既可以存放数据也可以存放程序;

所有DSP核共享4MB SL2 SRAM, 它的运行速度是DSP 核的一半,既可以存放数据也可以存放程序。一个64-bit 1333MTS DDR3 SDRAM接口可以支持8GB外部扩展存储器。

C6678 集成一个64-bit 1333MTS DDR3 SDRAM 接口,可以支持8GB 外部扩展存储器,既可以存放数据也可以存放程序。它的总线宽度也可以被配置成32 bits 或16 bits。

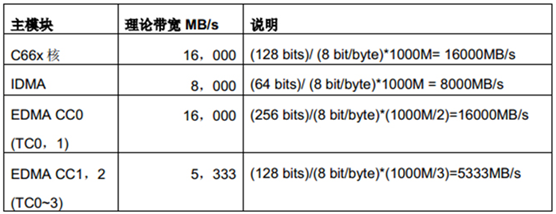

存储器访问性能对 DSP 上软件运行的效率是非常关键的。在 C6678 DSP 上,所有的主模块,包括多个DSP 核和多个DMA 都可以访问所有的存储器。

每个DSP 核每个时钟周期都可以执行最多128 bits 的load 或store 操作。在1GHz 的时钟频率下,DSP 核访问 L1D SRAM 的带宽可以达到 16GB/S。当访问二级(L2)存储器或外部存储器时,访问性能主要取决于访问的方式和cache。

每个 DSP 核有一个内部 DMA (IDMA),在 1GHz 的时钟频率下,它能支持高达 8GB/秒的传输。但IDMA 只能访问L1 和LL2 以及配置寄存器,它不能访问外部存储器。DSP 的内部总线交换网络,TeraNet,提供了C66x 核 (包括其本地存储器),外部存储器, EDMA 控制器,和片上外设之间的互联。总共有 10 个 EDMA 传输控制器可以被配置起来同时执行任意存储器之间的数据传输。芯片内部有两个主要的TeraNet模块,一个用 128 bit 总线连接每个端点,速度是DSP 核频率的1/3,理论上,在1GHz 的器件上每个端口支持 5.333GB/秒的带宽;另一个TeraNet内部总线交换网络用 256 bit 总线连接每个端点,速度是DSP 核频率的1/2,理论上,在1GHz 的器件上每个端口支持16GB/秒的带宽。

在看了上面的介绍后,有三个基本的问题,给大家思考:

(1)如果是拷贝数据,我们应该用DSP核还是DMA?

(2)一个频繁访问存储器的函数会消耗多少时钟周期?

(3)当多个主模块共享存储器时,对某个模块的性能到底有多大的影响?

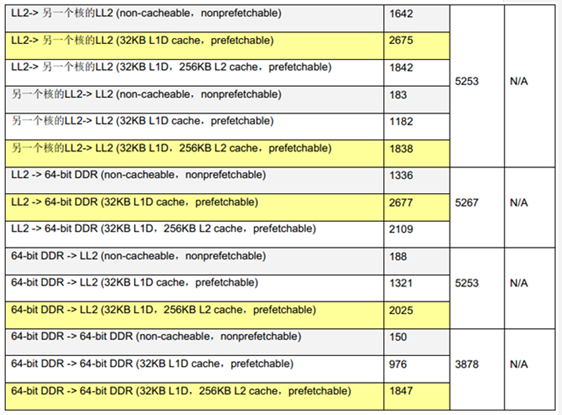

下面的一些测试数据是在EVM上的结果,在这里引用用来作性能评估参考 ,详细的文档在TI技术支持中文网站(www.deyisupport.com)下载:

http://www.deyisupport.com/quest ... e/f/53/t/21924.aspx

(1)1GHz C6678 上C66x 核,IDMA 和EDMA 的理论带宽

(2)1GHz C6678 上各种存储器端口的理论带宽

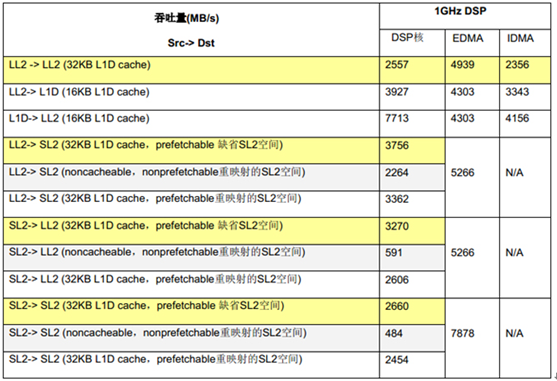

(3)DSP 核,EDMA 和IDMA 数据拷贝的吞吐量比较

从以上测试结果可以得出,DSP核与内部存储器之间数据交换的效率非常高,可是与外部存储器的交换则显得不那么激动人心;IDMA非常适用于DSP核本地存储器 (L1D,L1P,LL2)内连续数据块的传输,但不能访问共享存储器 (SL2, DDR);所以外部存储器的大块数据访问则应尽量使用EDMA。

Cache 配置显著地影响DSP 核的访问性能,预取缓冲器能提高读访问的效率,但对EDMA 和IDMA没有影响。测试结果是在cache和预取缓冲器在测试前被清空。

对DSP 核,SL2 可以通过从0x0C000000 开始的缺省地址空间被访问,通常这个地址空间被设置为cacheable 而且prefetchable。SL2 可以通过XMC (eXtended Memory Controller)被重映射到其它存储器空间,通常重映射空间被用作non-cacheable, nonprefetchable访问(当然它也可以被设置为cacheable 而且prefetchable)。通过缺省地址空间访问比通过重映射空间访问稍微快一点。

前面列出的EDMA 吞吐量数据是在EDMA CC0 (Channel Controller 0) TC0 (Transfer Controller 0)上测得的,EDMA CC1 和EDMA CC2 的吞吐量比EDMA CC0 低一些。

简简单单学TI 多核DSP(1):TMS320C6678的架构

最新推荐文章于 2025-10-13 16:35:27 发布

2412

2412

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?