LS1046A处理器基于QorIQ LS系列架构,将四个Arm® Cortex®-A72处理器内核与数据通路加速和网络、网络连接、网络附加存储、打印和成像以及通用所需的网络、外设接口相结合。

其SerDes 模块功能强大,复用关系稍微复杂,因此本文通过对CPU SerDes通道的复用关系的分析,以及LS1046A 开发板对于SerDes配置的梳理,希望可以帮助用户在使用飞凌嵌入式LS1046A系列OK1046A-C开发板或者自己做底板的时候对SerDes通道的配置有一个清晰的思路。

1、SerDes 配置方法

可通过设置以下寄存器对SerDes进行配置:

■ SerDes 1 Configuration:

· Protocol(s):Selected using RCW[SRDS_PRTCL_S1]

· PLLs: Enabled using RCW[SRDS_PLL_PD_S1]

· PLL Reference Clock: RCW[SRDS_PLL_REF_CLK_SEL_S1]

· (rates are determined by the protocol selection)

■ SerDes 2 Configuration:

· Protocol(s): Selected using RCW[SRDS_PRTCL_S2]

· PLLs: Enabled using RCW[SRDS_PLL_PD_S2]

· PLL Reference Clock: RCW[SRDS_PLL_REF_CLK_SEL_S2]

· Maximum rate: Selected using the following:

· PCIe: RCW[SRDS_DIV_PEX_S2]

· SATA rate selection is done in software

2、SerDes 协议

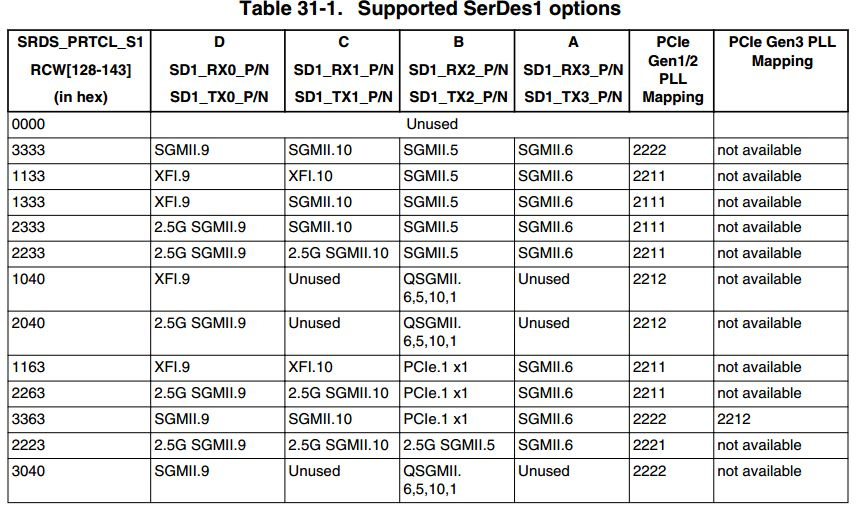

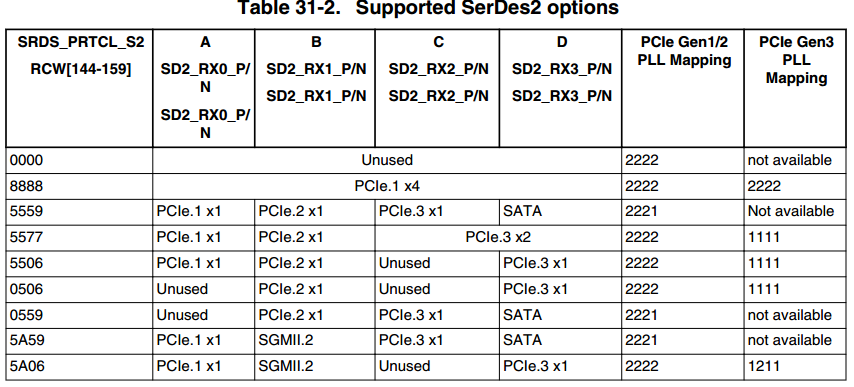

下表展示了SerDes的协议,图中使用了以下符号约定:

■ SGMII notation for frame manager (FMan):

· SGMII.n means SGMII (1 lane @ 1.25 Gbps or 3.125 Gbps)

· “n” indicates which MAC on the FMan.

· For example, “SGMII.9,” indicates SGMII for MAC 9 on FMan.

■ QSGMII notation for frame manager (FMan):

· “n” indicates which MAC on the FMan.

· For example, “QSGMII.1,2,5,6,” indicates QSGMII for MAC1, MAC2, MAC5

■ XFI notation for FMan:

·XFI.n means XFI (1 lane @ 10.3125 Gbps)

·“n” indicates which MAC on the FMan.

·For example, “XFI.9,” indicates XFI for MAC 9 on FMan.

■ PCI Express :

·PCIen (8/5/2.5) means PCI express operating up to 8 or 5 or 2.5 Gbps depending on maximum rate selection and training.

·“n” indicates the nth PCIe

■ SATA:

·SATAn (6/3/1.5) means SATA operating at 6 or 3 or 1.5 Gbps depending on rate selection. The rate of selection is performed by PxSCTL[SPD] register as described in SATA 3.0.

上表中第一列为RCW[SRDS_PRTCL_S1/2]寄存器可配置的值,2~5列为SerDes1/2的四个通道对应的配置,6、7列为A、B、C、D通道对应的PLL通道。其中第6列表示PCIe配置为PCIe Gen1/2时对应的PLL Mapping,第7列表示PCIe配置为PCIe Gen3时对应的PLL Mapping。PCIe Gen1/2/3可通过RCW[SRDS_DIV_PEX_Sn]进行配置。

每一行即为A、B、C、D四个通道对应不同寄存器的配置。

3、 SerDes协议规则

SerDes选择的有效配置取决于以下内容:

· 不允许在SerDes1和SerDes2上同时选择PCIe.1。

· 当SRDS_PRTCL_S1 = 0x3333且SRDS_REFCLK_SEL_S1为0’b0时,必须使用SRDS_PLL_PD_S1关闭SerDes1 PLL1。

· 当SRDS_PRTCL_S2 = 0x8888且SRDS_REFCLK_SEL_S2为0’b0时,必须使用SRDS_PLL_PD_S2关闭SerDes2 PLL1。

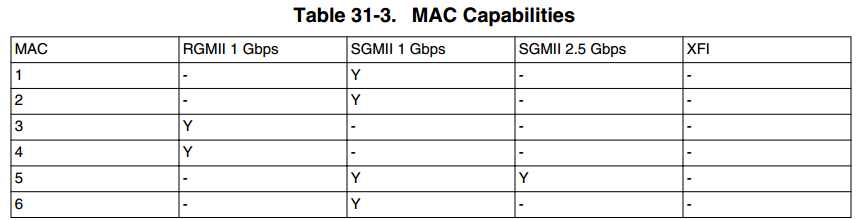

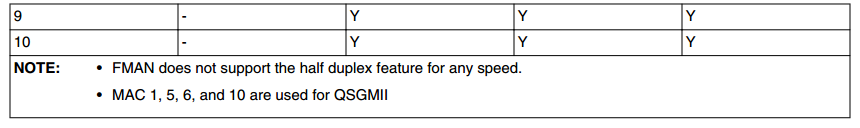

4 、 帧管理器MAC

每个FMan支持8个MAC。这些MAC支持不同的协议,如下表所示。

需要注意的是:

- FMAN不支持任何速度的半双工功能。2. MAC 1、5、6、10被用于QSGMII。

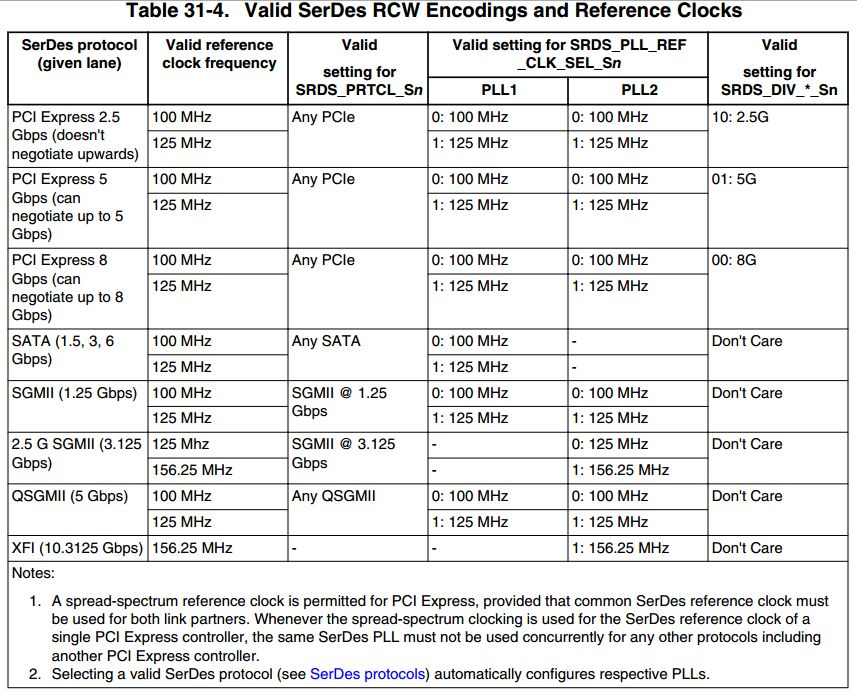

5、 SerDes时钟

每个支持的SerDes协议允许有限的一组有效的SerDes相关RCW字段和参考时钟频率,如下表所示:

6、OK1046A-C开发板相关配置

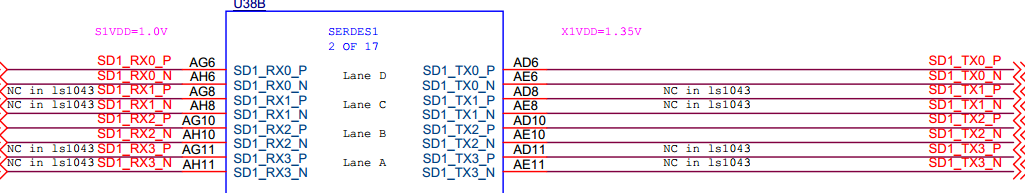

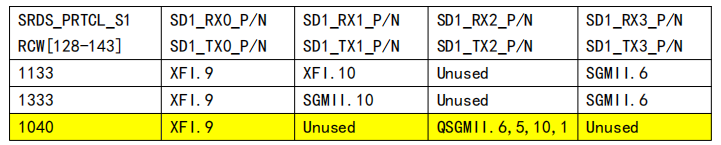

LS1046A核心板SerDes1:

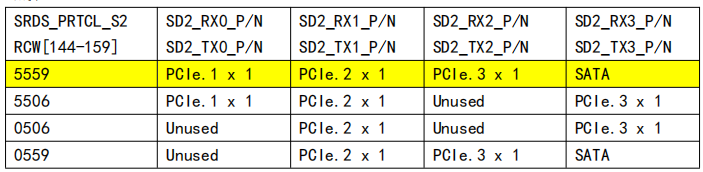

LS1046A核心板SerDes2:

LS1046A底板SerDes1:

LS1046A底板SerDes2:

默认LS1046A开发板SerDes1配置为1014,SerDes2配置为5559。如果客户自己绘制底板,则可以根据自己的需求按照Table31-1与Table31-2来配置SerDes1/2。

有关SerDes的具体描述详见QorIQ LS1046A Reference Manual的Chapter 31 SerDes Module。

</div>

本文深入解析了LS1046A处理器的SerDes模块配置方法,包括通过寄存器进行配置的详细步骤,以及针对PCIe、SATA等协议的配置规则。同时,提供了OK1046A-C开发板的SerDes配置实例,帮助用户理解并应用到实际项目中。

本文深入解析了LS1046A处理器的SerDes模块配置方法,包括通过寄存器进行配置的详细步骤,以及针对PCIe、SATA等协议的配置规则。同时,提供了OK1046A-C开发板的SerDes配置实例,帮助用户理解并应用到实际项目中。

568

568

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?