参考原文链接:

FIR滤波器:https://blog.youkuaiyun.com/bleauchat/article/details/84558355

FPGA数字信号处理(二)并行FIR滤波器Verilog设计:https://blog.youkuaiyun.com/fpgadesigner/article/details/80594627

1.原理

FIR滤波器是非递归型滤波器的简称,又叫有限长单位冲激响应滤波器。带有常系数的FIR滤波器是一种LTI(线性时不变)数字滤波器。冲激响应是有限的意味着在滤波器中没有负反馈。长度为N的FIR输出对应于输入时间序列x(n)的关系由一种有限卷积和的形式给出,具体形式如下:

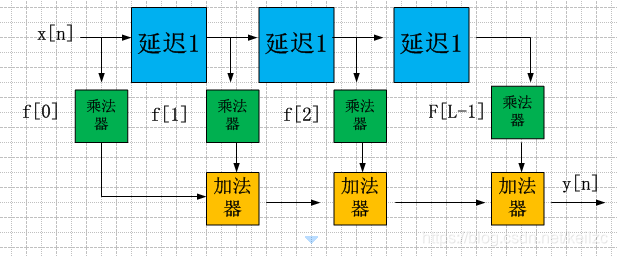

直接形式FIR滤波器图解:

上式表达的是一个N-1阶的FIR滤波器,它有N个抽头(系数)。因此有N个乘法器,N-1个累加器组成。每一个抽头需要消耗逻辑资源的乘法器累加器( Mac )单元。

FIR滤波器结构:

输入信号是有时间性的,随着时间的改变而改变,FIR滤波器最终的输出是各个时刻的输入乘以相应的权重(系数),然后进行叠加输出:

本文深入探讨了FIR滤波器的工作原理,详细解释了其作为非递归型滤波器的特性,以及如何通过有限长单位冲激响应实现信号处理。文章涵盖了FIR滤波器的结构,包括直接形式的图解,以及输入信号与权重系数的卷积过程。

本文深入探讨了FIR滤波器的工作原理,详细解释了其作为非递归型滤波器的特性,以及如何通过有限长单位冲激响应实现信号处理。文章涵盖了FIR滤波器的结构,包括直接形式的图解,以及输入信号与权重系数的卷积过程。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?