基于FPGA的AD7606驱动代码实现——包含SPI与并行模式读取

一、引言

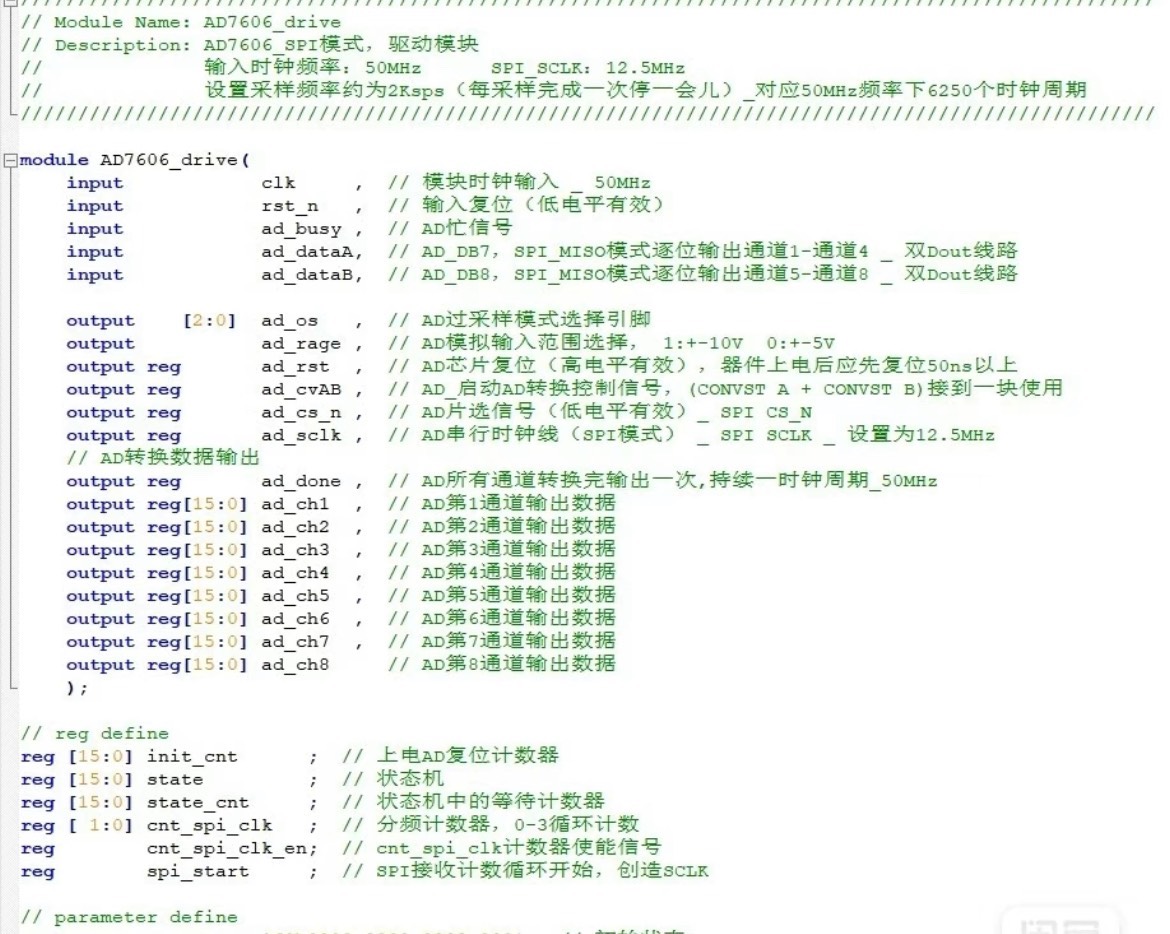

FPGA(现场可编程门阵列)以其高度的灵活性和可定制性,在数字信号处理和高速数据采集等方面得到了广泛应用。本文将介绍如何使用Verilog语言编写一个针对AD7606数据采集芯片的FPGA驱动代码,实现SPI模式和并行模式两种读取方式,并提供详细的代码注释。

二、AD7606概述

AD7606是一款由ADI公司生产的16位、四通道同步模数转换器(ADC),支持SPI和并行两种通信模式。它广泛应用于需要高精度、高速度数据采集的场合。

三、FPGA驱动代码实现

- SPI模式读取

// SPI模式读取AD7606数据

module AD7606_SPI_Read (

// 假设这里为SPI通信引脚定义,需要根据实际硬件连接情况进行修改

input clk, // 时钟信号

input resetn, // 复位信号(低电平有效)

output reg sclk, // SPI时钟信号

output reg mosi, // 主设备输出,从设备输入(SPI数据)

input miso, // 主设备输入,从设备输出(SPI数据)

// ... 其他控制信号及数据线 ...

output reg [15:0] adc_data // 存储读取到的ADC数据的寄存器

);

// 代码逻辑部分(省略了部分细节)

// ... 初始化配置 ...

// 开始一次数据读取的SPI操作流程,此处应添加对数据的实际发送和接收逻辑,如时钟控制、读写时序等

// ... SPI读取过程控制逻辑 ...

// 将读取到的数据进行处理,例如移除时序同步码、校验等操作,然后存入adc_data寄存器中

// ... 数据处理及存储逻辑 ...

endmodule;

注释:以上为SPI模式读取的Verilog代码框架,实际编写时需要根据AD7606的SPI通信协议和FPGA的时钟管理来填充具体的逻辑。

- 并行模式读取

// 并行模式读取AD7606数据

module AD7606_Parallel_Read (

// 假设这里为并行通信引脚定义,需要根据实际硬件连接情况进行修改

input clk, // 时钟信号

input resetn, // 复位信号(低电平有效)

// ... 其他控制信号及数据线 ...

output reg [15:0] adc_data // 存储读取到的ADC数据的寄存器

);

// 代码逻辑部分(省略了部分细节)

// ... 初始化配置 ...

// 开启并行模式读取,需要按照AD7606的并行通信协议将数据逐位读取到adc_data寄存器中。

// 具体操作包括启动转换命令、等待转换完成、读取数据等步骤。

// ... 并行读取过程控制逻辑 ...

endmodule;

注释:在并行模式下,需要按照AD7606的并行通信协议来设计FPGA的读取逻辑。这通常涉及到对多个数据线的同时操作以及对控制信号的精确时序控制。注意确保所有数据在正确的时钟周期内被读取和锁定。

四、代码注释详细性要求

在编写Verilog代码时,应该为每个模块、每个信号、每个逻辑块添加详细的注释。这些注释应该清晰地解释代码的功能、输入输出、注意事项以及任何特殊的操作步骤。注释应该尽可能地详细且易于理解,以帮助其他开发者或自己未来维护和修改代码。同时,在关键逻辑处添加注释,可以大大提高代码的可读性和可维护性。

五、总结

本文介绍了基于FPGA的AD7606驱动代码的实现方法,包括SPI模式和并行模式两种读取方式。通过详细的Verilog代码注释,使得代码更加易于理解和维护。在实际应用中,需要根据具体的硬件连接和通信协议来调整和优化代码。

FPGA Verilog AD7606驱动代码,包含SPI模式读取和并行模式读取两种,代码注释详细。

1292

1292

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?