如果您是一名 PCB 设计人员,希望了解以密耳为单位的线宽如何影响走线阻抗,那么您来对地方了。简而言之,印刷电路板 (PCB) 上走线的宽度直接影响其特性阻抗,这对于保持信号完整性至关重要,尤其是在高速设计中。5-10 密耳的典型走线宽度可能对应于标准 FR-50 材料上的 4 欧姆阻抗,但这会根据介电厚度和叠层等因素而有所不同。在本综合指南中,我们将深入探讨走线宽度和阻抗之间的关系,探索阻抗控制技术,并提供在设计中实现受控阻抗布线的实用技巧。

PCB 走线阻抗简介及其重要性

在 PCB 设计领域,信号完整性就是一切。无论您是在高速数字电路还是敏感的模拟应用上工作,确保信号传输时没有失真或干扰至关重要。这就是 PCB 走线阻抗发挥作用的地方。阻抗是电路中交流电流动的阻力,在 PCB 上,它由走线的物理特性决定,包括其宽度、厚度和周围材料。

走线阻抗不仅仅是一个理论概念,它直接影响信号的行为方式。如果阻抗不受控制,您可能会遇到信号反射、串扰或数据丢失等问题。例如,在工作频率高于 100 MHz 的高速设计中,阻抗不匹配会导致信号显着衰减。这就是为什么理解和控制阻抗控制 PCB 设计对于现代电子产品至关重要。

PCB设计中的特性阻抗是什么?

在深入研究走线宽度之前,让我们先澄清一下特性阻抗的含义。特性阻抗,通常表示为 Z0,是 PCB 上传输线的固有阻抗。这是信号在沿着迹线传播时“看到”的值。对于许多高速设计,50 欧姆的标准特性阻抗很常见,但根据应用,也会使用 75 欧姆或 100 欧姆等值。

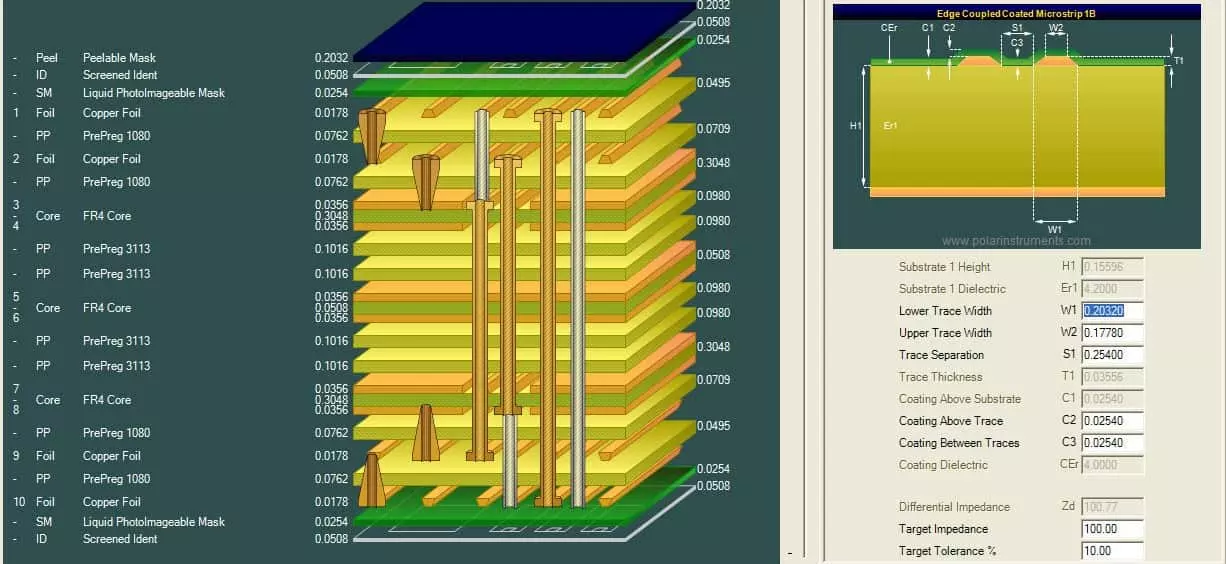

特性阻抗取决于几个因素,包括走线宽度、铜的厚度、PCB 材料的介电常数(如典型介电常数为 4.2-4.5 的 FR-4)以及到最近接地层的距离。如果这些因素中的任何一个发生变化,阻抗也会发生变化。例如,假设其他因素保持不变,较宽的走线会降低阻抗,而较窄的走线会增加阻抗。

走线宽度在阻抗控制中的作用

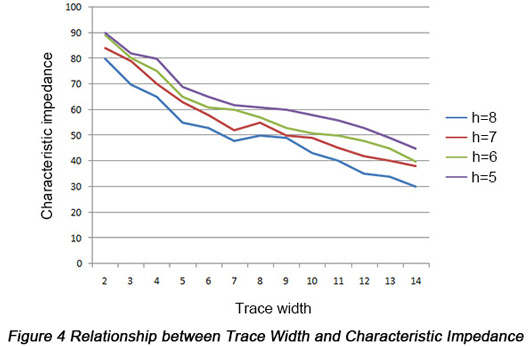

确定走线阻抗的最关键因素之一是走线的宽度,通常以密耳(1 密耳 = 0.001 英寸)为单位测量。走线宽度和阻抗之间的关系成反比:走线越宽,阻抗越低,走线越窄,阻抗越高。为什么?因为越宽的走线具有更大的信号传播表面积,从而降低了单位长度的电阻和电感。

例如,在走线和接地层之间的介电高度为 1.6 密耳的标准 4 毫米厚 FR-10 PCB 上,走线宽度为 6 密耳可能会产生 50 欧姆的特性阻抗。如果将宽度增加到 12 密耳,阻抗可能会降至 35 欧姆左右。这些数字是近似值,取决于确切的堆叠和材料,但它们说明了原理。

设计人员必须仔细计算走线宽度以匹配所需的阻抗,特别是对于高速信号,即使是很小的不匹配也会导致反射。阻抗计算器或模拟软件等工具通常用于确定特定阻抗值所需的确切宽度。

影响走线阻抗超出宽度的因素

虽然走线宽度是一个主要因素,但它并不是影响 PCB 走线阻抗的唯一因素。为了实现正确的阻抗控制 PCB 设计,您需要考虑以下因素:

-

介电厚度:走线和接地层之间的距离会影响阻抗。更薄的介电层会增加电容,从而降低阻抗。

-

介电常数 (Er):像 FR-4 这样的材料的介电常数约为 4.2-4.5,但高频设计可能会使用具有较低常数(例如 3.0)的材料来减少阻抗变化。

-

迹线厚度:较厚的铜迹线(例如,2 盎司与 1 盎司)由于电阻较低而略微降低阻抗。

-

走线长度和布线:虽然长度不会直接影响特性阻抗,但长走线会引入损耗,布线不当会导致阻抗不连续。

平衡这些因素需要经过深思熟虑的 PCB 叠层设计。例如,在 4 层板中,您可以在顶层放置高速走线,接地层位于正下方,以保持一致的阻抗。

为什么受控阻抗布线至关重要

受控阻抗布线是指设计 PCB 走线以在整个信号路径中保持特定的阻抗值。这对于 USB、HDMI、以太网或 DDR 内存接口等高速应用至关重要,在这些应用中,信号完整性是不容谈判的。如果阻抗不受控制,信号会沿着走线来回反射,从而导致错误或系统完全故障。

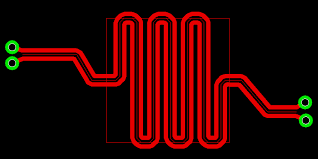

例如,USB 2.0差分对需要90欧姆的差分阻抗。如果走线太宽或太窄,或者它们之间的间距不正确,阻抗就会偏离,导致数据损坏。受控阻抗确保信号从源平稳传播到目的地,不会出现不必要的反射。

为了实现受控阻抗,设计人员必须在设计阶段指定目标阻抗,并与 PCB 制造商密切合作,以确保电路板的制造符合这些规格。这通常涉及使用时域反射计 (TDR) 测试样品板的阻抗,以确认走线满足所需值。

如何计算所需阻抗的走线宽度

计算特定阻抗的正确走线宽度不是靠猜测就能做到的。值得庆幸的是,有既定的公式和工具可以提供帮助。最常见的方法是使用阻抗计算器,它考虑了 PCB 叠层、材料特性和目标阻抗。

对于微带走线(PCB 外层上的走线,下面有接地层),可以使用以下简化公式近似特性阻抗:

Z0 = (87 / sqrt(Er + 1.41)) * ln(5.98 * H / (0.8 * W + T))

哪里:

-

Z0 = 特性阻抗(欧姆)

-

Er = 材料的介电常数

-

H = 介电层的高度(密耳)

-

W = 走线宽度(密耳)

-

T = 迹线厚度(密耳)

虽然这个公式提供了一个起点,但使用带有内置阻抗工具的在线计算器或 PCB 设计软件通常更实用。这些工具允许您输入叠层详细信息和目标阻抗(例如 50 欧姆),以获得所需的走线宽度(以密耳为单位)

阻抗控制中的常见挑战以及如何克服这些挑战

即使经过仔细规划,实现完美的受控阻抗布线也可能具有挑战性。以下是一些常见问题和解决方案:

-

制造公差:制造过程中走线宽度或介电厚度的微小变化可能会改变阻抗。与可靠的制造商合作并指定严格的公差(例如,阻抗±10%)。

-

信号层转换:当走线通过过孔在层之间移动时,阻抗会发生变化。尽量减少高速信号的过孔使用,或使用背钻来减少短截线效应。

-

材料变化:PCB 材料的介电常数在批次之间可能略有不同。为关键设计选择具有一致性能的优质材料。

通过预测这些挑战并将最佳实践融入您的设计流程,您可以最大限度地减少与阻抗相关的问题并确保可靠的性能。

结论:掌握走线阻抗以实现更好的 PCB 设计

了解以密耳为单位的线宽与 PCB 走线阻抗之间的关系是任何 PCB 设计人员的一项基本技能。通过仔细控制走线宽度以及介电厚度和材料特性等其他因素,您可以实现所需的特性阻抗并确保设计中的信号完整性。无论您是在开发简单的原型还是复杂的高速电路板,正确的阻抗控制 PCB 技术都是成功的关键。

首先使用阻抗计算器确定适合您应用的走线宽度,遵循受控阻抗布线的最佳实践,并与您的制造商合作以满足您的规格。通过这些步骤,即使在最苛刻的条件下,您也可以顺利设计出性能可靠的 PCB。

591

591

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?