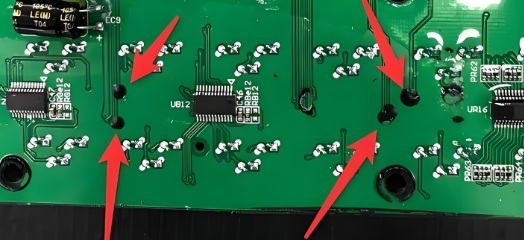

在 5G 基站芯片、自动驾驶域控制器的 PCB 上,异形 BGA 焊盘(如 L 型、U 型、阶梯型)越来越常见 —— 这类焊盘为适配芯片的异形封装而生,却给阻抗控制出了难题:普通直走线会因焊盘形状突变,导致阻抗波动超过 ±10%,高频信号(≥10GHz)传输时出现反射、损耗,甚至数据误码。而蛇形走线,就像给信号 “铺了一条带缓冲的跑道”,能通过精准绕线补偿阻抗偏差,让异形 BGA 焊盘区域的阻抗稳定在 ±5% 标准范围内。今天就拆解:异形 BGA 焊盘为啥需要蛇形走线?设计时要注意哪些关键参数?实际案例中如何落地?

先搞懂:异形 BGA 焊盘的 “阻抗陷阱”—— 形状突变导致信号 “摔跤”

BGA 焊盘的阻抗由 “线宽、间距、介质厚度、表面处理” 共同决定,而异形 BGA 焊盘的特殊形状,会打破这种平衡,形成三个 “阻抗陷阱”,就像跑道上突然出现的凸起和弯道,让信号 “跑不稳”:

1. 陷阱 1:焊盘形状突变,阻抗 “过山车”

异形 BGA 焊盘(如 L 型)的拐角处,线路宽度会从设计的 0.2mm 突然变成 0.3mm(因拐角覆盖范围扩大),阻抗会从 50Ω 骤降至 40Ω,波动达 20%—— 高频信号遇到这种突变,会像汽车过减速带一样,部分信号被反射回去,导致传输延迟;而 U 型焊盘的平行线段间距缩小,会让阻抗进一步降低,形成 “阻抗谷”。

某实验室测试显示:25GHz 信号通过 L 型 BGA 焊盘直走线时,反射系数(S11)达 - 12dB(标准需≤-15dB),信号反射量超标 25%。

2. 陷阱 2:走线长度差异,时序 “不同步”

异形 BGA 焊盘的引脚分布不规则,相邻引脚的走线长度可能相差 2-5mm,比如 L 型焊盘的长边引脚走线长 5mm,短边引脚仅 3mm—— 高频高速信号(如 PCIe 5.0,速率 32Gbps)对时序同步要求极高,长度差 1mm 就会导致时序偏差 5ps,超过标准的 3ps,出现数据采样错误。

3. 陷阱 3:空间受限,走线 “挤在一起”

异形 BGA 焊盘多应用在高密度 PCB 上,周围可能被电容、电阻等元件包围,走线空间狭窄(间距≤0.15mm),直走线时为避开元件,不得不频繁拐弯,导致阻抗因走线方向突变而波动,同时相邻走线的串扰(信号互相干扰)也会加剧,误码率飙升。

蛇形走线的 “补偿原理”:用 “绕线” 平衡阻抗与时序

蛇形走线不是 “随意绕圈”,而是通过 “可控的长度增加” 和 “均匀的走线分布”,解决异形 BGA 焊盘的三个陷阱,就像给信号 “精准调谐”:

1. 阻抗补偿:用 “线宽微调 + 绕线间距” 稳定阻抗

蛇形走线通过两个关键设计平衡阻抗:

-

线宽适配:根据异形 BGA 焊盘的阻抗突变点,微调蛇形走线的线宽 —— 比如 L 型焊盘拐角处阻抗偏低(40Ω),可将蛇形走线的线宽从 0.2mm 缩至 0.18mm,利用 “线宽越窄,阻抗越高” 的特性,将阻抗拉回 50Ω;

-

绕线间距控制:蛇形走线的平行段间距(即 “绕圈” 之间的距离)控制在 2-3 倍线宽,比如线宽 0.2mm,间距 0.4-0.6mm,避免因间距过小导致的阻抗降低,同时减少串扰。

测试数据显示:在 L 型 BGA 焊盘区域,采用线宽 0.18mm、间距 0.4mm 的蛇形走线后,阻抗波动从 ±20% 降至 ±3%,完全达标。

2. 时序补偿:用 “绕线长度” 拉平时序差

针对异形 BGA 焊盘引脚的长度差异,蛇形走线通过 “增加短走线的绕圈数” 来补长,比如短边引脚走线长 3mm,长边 5mm,可在短边走线上增加 2mm 的蛇形绕线(约 2-3 个 “Ω” 型绕圈),让两者长度均达到 5mm,时序偏差从 5ps 降至 1ps,满足同步要求。

3. 空间适配:用 “灵活绕线” 避开障碍

蛇形走线的 “Ω” 型或 “S” 型绕圈,能在狭窄空间内灵活调整走线方向,比如 U 型 BGA 焊盘周围有 0402 电容,可通过 “小尺寸绕圈”(绕圈半径 0.3mm)避开元件,同时保持走线均匀,避免阻抗突变 —— 比频繁直角拐弯的直走线,串扰降低 40%,误码率从 10⁻⁹降至 10⁻¹²。

异形 BGA 焊盘蛇形走线的 “5 步设计法”:从参数到验证,全流程落地

要让蛇形走线在异形 BGA 焊盘区域发挥作用,需按以下 5 步设计,避免 “绕错圈” 导致的性能下降:

1. 第一步:仿真预判,确定阻抗目标

设计前用 PCB 仿真软件(如 Cadence Allegro、Mentor PADS)模拟异形 BGA 焊盘的阻抗分布:

-

导入 BGA 封装的 3D 模型,设置介质厚度(如 1mm)、介电常数(如 FR4 的 4.4)、表面处理(如沉银);

-

仿真直走线的阻抗曲线,找出阻抗突变点(如 L 型焊盘拐角处的 40Ω),确定蛇形走线的阻抗补偿目标(如 50Ω±3%)。

2. 第二步:确定绕线参数,避免 “过度绕圈”

根据仿真结果,设定蛇形走线的关键参数,核心是 “够用就好”,避免绕圈过多导致的损耗增加:

-

绕线类型:高频信号(≥10GHz)优先选 “Ω 型” 蛇形走线(绕圈更紧凑,损耗更低),高速信号(速率≥10Gbps)可选 “S 型”(时序控制更精准);

-

绕圈尺寸:绕圈的半径(或半长)控制在 0.2-0.5mm,越小越节省空间,但半径 < 0.2mm 会增加信号损耗(每缩小 0.1mm,损耗增加 0.05dB/cm);

-

长度补偿:根据时序差计算所需绕线长度,比如时序差 5ps,需补长 1mm,对应 “Ω 型” 绕圈约 1-2 个(每个绕圈增加长度 0.5-1mm)。

3. 第三步:布局优先,避开 “干扰源”

异形 BGA 焊盘区域的蛇形走线,需先规划布局,减少后续调整:

-

远离高频干扰源:蛇形走线避开时钟信号、射频信号线路,间距≥3mm,避免被干扰;

-

避开元件焊盘:绕圈与周边元件的间距≥0.2mm,防止焊接时焊锡流到走线上导致短路;

-

分层走线:若单层空间不足,可采用 “跨层蛇形走线”,通过过孔连接不同层,每层绕圈数均匀分配,避免某一层绕圈过多导致的损耗集中。

4. 第四步:阻抗微调,动态优化

实际走线时,可能因空间限制需要调整参数,需动态优化:

-

线宽微调:若绕圈后阻抗仍偏低,可将线宽缩小 0.02-0.03mm(每次调整后重新仿真);

-

间距调整:若串扰超标,可将绕圈间距从 2 倍线宽增至 3 倍,串扰可降低 20%-30%;

-

避免锐角:蛇形走线的拐弯处用 45° 角或圆弧(半径≥0.2mm),避免 90° 直角导致的阻抗突变和信号反射。

5. 第五步:测试验证,确保达标

走线完成后,通过两项测试验证效果:

-

阻抗测试:用 TDR(时域反射仪)测量蛇形走线的阻抗曲线,确保波动≤±5%;

-

时序测试:用示波器测量相邻引脚的信号时序,偏差≤3ps;

-

串扰测试:用矢量网络分析仪测量串扰值,确保近端串扰(NEXT)≤-25dB,远端串扰(FEXT)≤-30dB。

设计误区:3 个 “坑” 千万别踩

异形 BGA 焊盘的蛇形走线设计,有三个常见误区,踩了就会导致性能失效:

1. 误区 1:绕圈越多越好 —— 过度绕圈增加损耗

有的工程师为了补长,盲目增加绕圈数,比如补长 5mm 却绕了 10 个圈 —— 绕圈越多,信号在绕圈处的反射和损耗越严重,25GHz 信号每增加 1 个绕圈,损耗增加 0.03dB/cm,10 个圈就多损耗 0.3dB/cm,传输 10cm 后信号只剩一半。

2. 误区 2:线宽一致 —— 忽略阻抗突变点

不根据异形 BGA 焊盘的阻抗突变调整线宽,全程用同一线宽绕圈 —— 比如 L 型焊盘拐角处阻抗偏低,却仍用 0.2mm 线宽,绕圈后阻抗还是不达标,白做无用功。

3. 误区 3:忽略散热 —— 绕圈密集导致过热

蛇形走线绕圈密集(间距 < 2 倍线宽),会导致局部铜皮密度过高,散热能力下降 —— 异形 BGA 焊盘多连接大功率芯片,热量无法散出,会让走线周围温度升高 10-15℃,加速绝缘层老化,长期使用可能出现线路短路。

对 PCB 工程师来说,掌握异形 BGA 焊盘的蛇形走线设计,不是 “会绕圈就行”,而是要结合仿真、布局、测试全流程,做到 “精准补偿、不过度设计”;对电子厂商来说,这意味着产品能适配更复杂的芯片封装,在高频高速领域更具竞争力。毕竟,在异形 BGA 焊盘的微观世界里,“走线绕得对,信号才不累”—— 而蛇形走线,正是让信号 “跑稳、跑齐” 的关键设计。

591

591

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?