在电子设计领域,时间就是金钱。你是否曾为等待 PCB 样板而焦急? 24 小时能拿到 PCB 样板吗?在追求快速打样的过程中,避免错误至关重要。

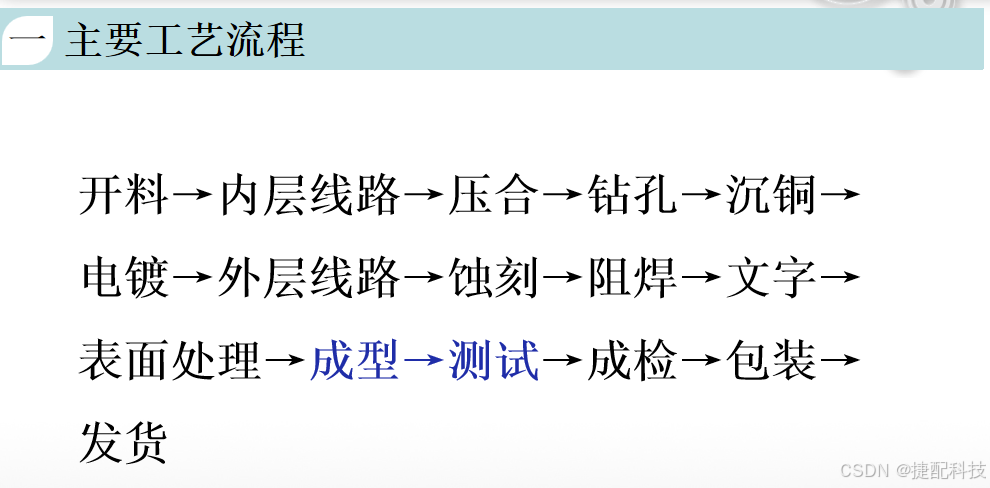

PCB快速打样流程示意图

PCB快速打样流程示意图

原理图设计陷阱

- 信号接入问题 :ERC 报告管脚未接入信号,这可能源于封装创建时 I/O 属性定义不当,或是元件放置时 grid 属性不一致,以及 pin 方向错误。而初学者常因未建立工程文件导致此问题。

- 元件摆放与网络表调入 :元件跑到图纸界外,多是因未在元件库图表纸中心创建。工程文件网络表只能部分调入 PCB,是因为生成 netlist 时未选择 global。使用自创多部分元件时,切忌使用 annotate。

PCB 设计误区

- 网络载入故障 :网络载入时报告 NODE 未找到,可能是原理图元件封装在 PCB 库中缺失、名称或 pin number 不一致。

- 打印与 DRC 问题 :打印无法一页完成,或是因 PCB 库未在原点创建,或是板界外有隐藏字符。DRC 报告网络分段,需通过查看报告文件和选择 CONNECTED COPPER 查找原因,复杂设计尽量避免自动布线。

PCB 制造错误

- 焊盘与图形层问题 :焊盘重叠会导致重孔等不良后果。图形层使用不规范,如元件面与焊接面设计颠倒,或存在设计垃圾,都会影响制造和使用。

- 字符与单面焊盘设置 :字符不合理会妨碍检测和焊接,其大小需控制在合适范围。单面焊盘孔径设置不当,会在钻孔数据生成或电地层数据输出时出现问题。

- 其他制造问题 :用填充块画焊盘无法生成阻焊数据;电地层散热盘与信号线设计混乱;大面积网格间距过小增加加工难度;图形距外框太近影响外观质量;外形边框设计不明确给厂家带来困扰;图形设计不均匀影响电镀效果;异型孔尺寸不合理无法加工;未设计铣外形定位孔;孔径标注不清;多层板内层走线不合理;埋盲孔板设计不当则无法发挥其优势。

239

239

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?