一 嵌入式存储器结构由一列 列 BRAM(块 RAM)存储器模块组成,通过对这些 BRAM 存储器模块进行配置,可以实现各种存储器的 功能,例如:RAM、移位寄存器、ROM 以及 FIFO 缓冲器。

RAM和ROM区别是: RAM 是一种随机存取存储器,不仅仅可以存储数据,同时支持对存储的数据进行 修改;而 ROM 是一种只读存储器,也就是说,在正常工作时只能读出数据,而不能写入数据。

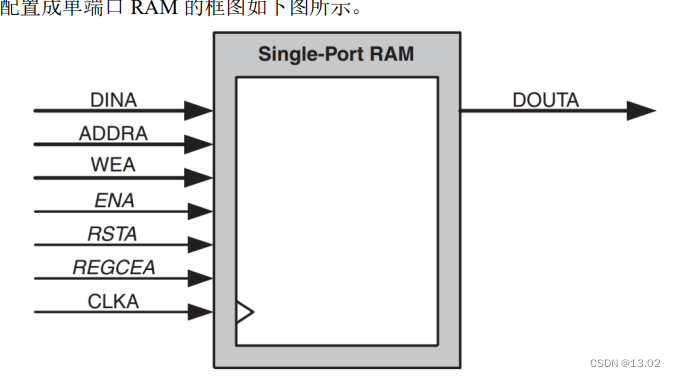

三种端口:BRAM 全部是真双端口 RAM(True Dual-Port ram,TDP),这两个端口都可 以独立地对 BRAM 进行读/写。但也可以被配置成伪双端口 RAM(Simple Dual-Port ram,SDP)(有两个 端口,但是其中一个只能读,另一个只能写)或单端口 RAM(只有一个端口,读/写只能通过这一个端口来 进行)。

DINA:RAM 端口 A 写数据信号。 ADDRA:RAM 端口 A 读写地址信号,对于单端口 RAM 来说,读地址和写地址共用同该地址线。 WEA:RAM 端口 A 写使能信号,高电平表示向 RAM 中写入数据,低电平表示从 RAM 中读出数据。 ENA:端口 A 的使能信号,高电平表示使能端口 A,低电平表示端口 A 被禁止,禁止后端口 A 上的读 写操作都会变成无效。另外 ENA 信号是可选的,当取消该使能信号后,RAM 会一直处于有效状态。 RSTA:RAM 端口 A 复位信号,可配置成高电平或者低电平复位,该复位信号是一个可选信号。 REGCEA:RAM 端口 A 输出寄存器使能信号,当 REGCEA 为高电平时,DOUTA 保持最后一次输出 的数据,REGCEA 同样是一个可选信号。 CLKA:RAM 端口 A 的时钟信号。 DOUTA:RAM 端口 A 读出的数据。

二 实验任务:本节实验任务是使用 Xilinx BMG IP 核,配置成一个单端口的 RAM,然后对 RAM 进行读写操作,通 过在

本文介绍了FPGA中RAM的结构,包括BRAM类型如TDP、SDP和SP,并详细阐述了RAM端口的操作信号。实验任务是通过Xilinx BMG IP核创建一个单端口RAM,进行读写操作,并通过Vivado仿真器及ILA在线调试验证设计正确性。

本文介绍了FPGA中RAM的结构,包括BRAM类型如TDP、SDP和SP,并详细阐述了RAM端口的操作信号。实验任务是通过Xilinx BMG IP核创建一个单端口RAM,进行读写操作,并通过Vivado仿真器及ILA在线调试验证设计正确性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4097

4097

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?