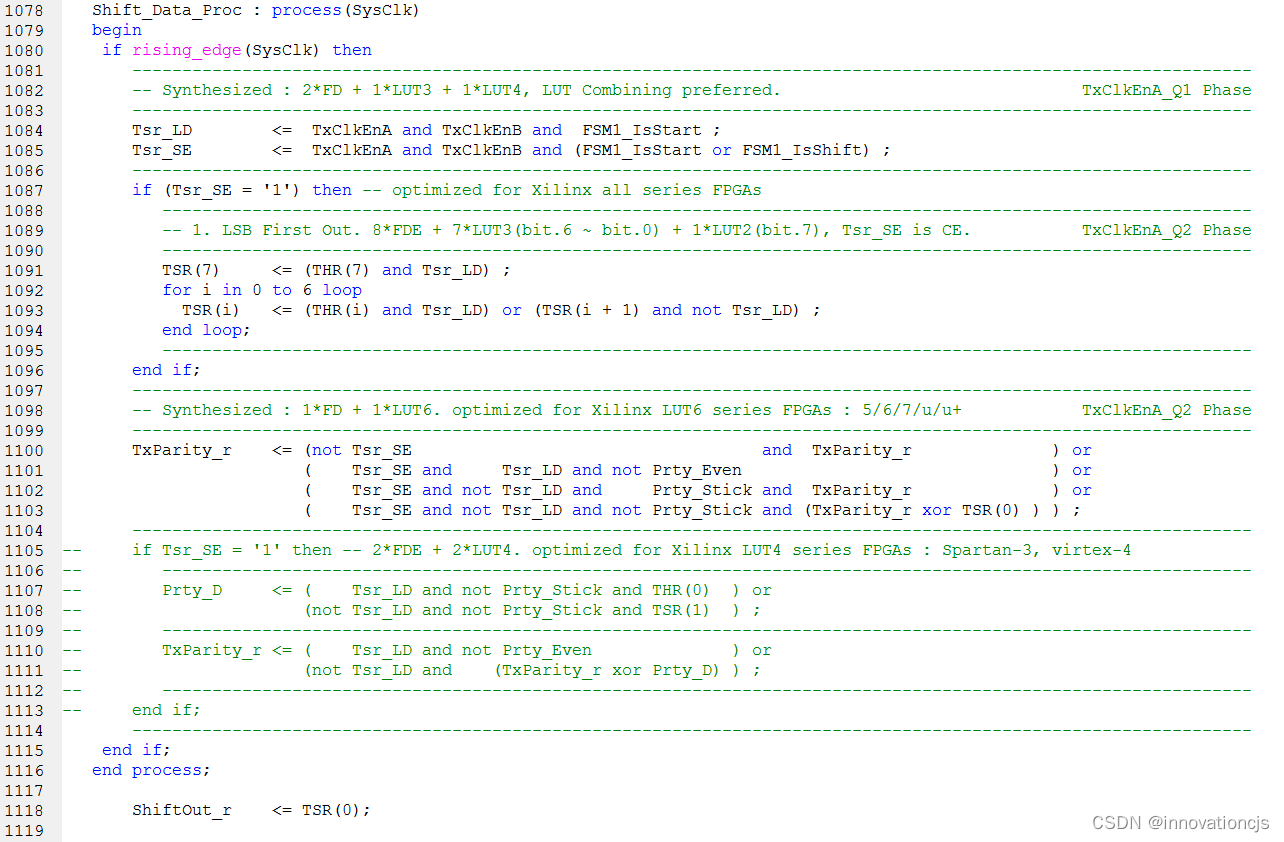

信号说明:

- 本部分电路移位输出ShiftOut_r(数据位)和TxParity_r(校验位)两个信号;

- TxClkEnA为2x比特时钟使能信号,TxClkEnB为1x比特时钟使能信号;

- FSM1_IsStart、FSM1_IsShift为状态机逻辑的状态信号,分别表示"起始位"、"数据位(含校验位)"状态;

- THR[7:0]为IP外部输入的待发送数据;

- Prty_Even, IP内部根据外部控制信号生成的奇偶校验设定值;

- Prty_Stick, IP内部根据外部控制信号生成的强制奇偶校验设定值

针对什么平台?

针对Xilinx全系列FPGA:Spartan-3、Virtex-4、Virtex-5、Spartan-6、Virtex-6、7系、UltraScale/UltraScale+。

优化了什么?

全流水线设计,时序性能,只有时序性能。

- Spartan-3、Virtex-4系列基于LUT4,校验位的生成采用注释掉的那段代码。整个移位寄存器及校验位生成可确保1个逻辑层级(Logic Level)实现;

- Xilinx 6系及以上的FPGA基于LUT6,整个移位寄存器及校验位生成可确保1个逻辑层级(Logic Level)实现;

- Xilinx LUT6支持在5输入范围内,同一LUT实现两个独立的功能,分别从其O6/O5输出,TSR[7:0]的设计满足相邻两位共5个输入的关系,6系之后的FPGA,均可实现用1个Slice完成此8位TSR的设计。

88

88

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?