Verilog语言基础学习(侧重于设计用的语法)

目录

前言

一、总述

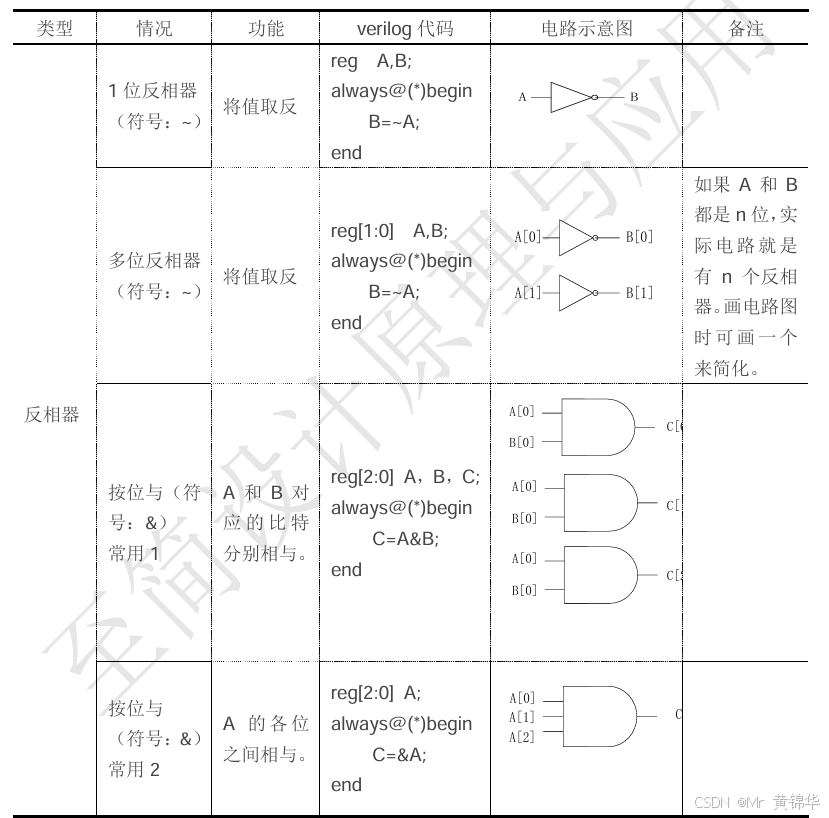

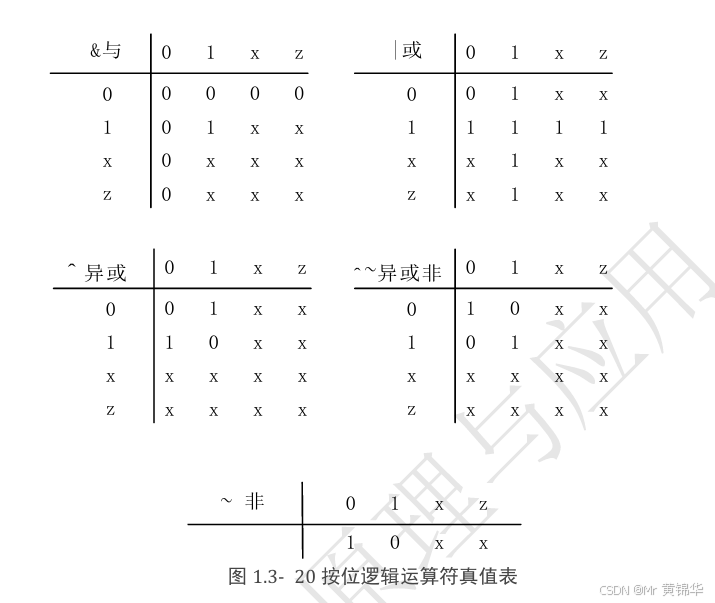

在Verilog HDL语言中有下面几种按位运算符:

~(一元非):(相当于非门运算)

&(二元与):(相当于与门运算)

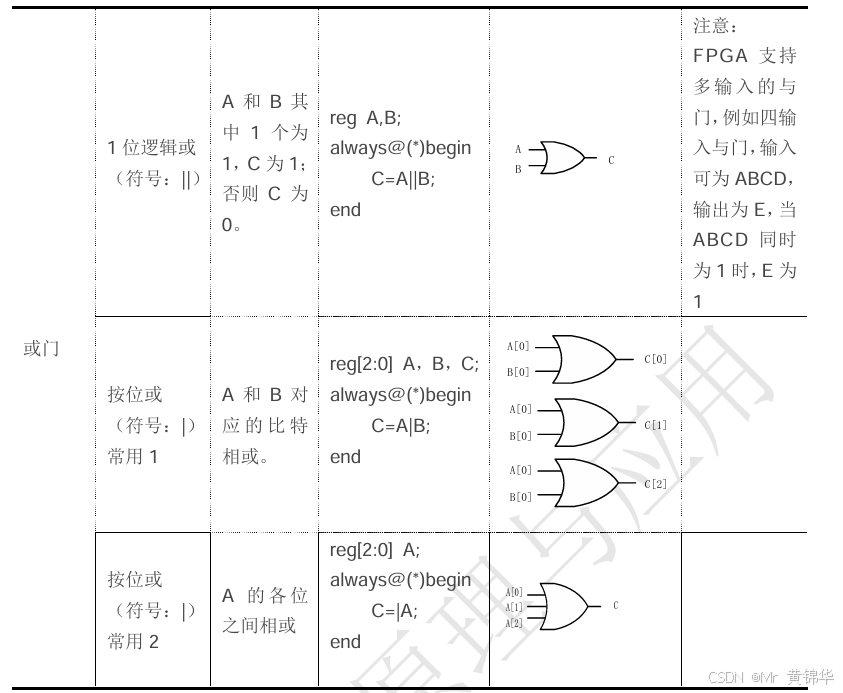

|(二元或):(相当于或门运算)

^(二元异或):(相当于异或门运算)

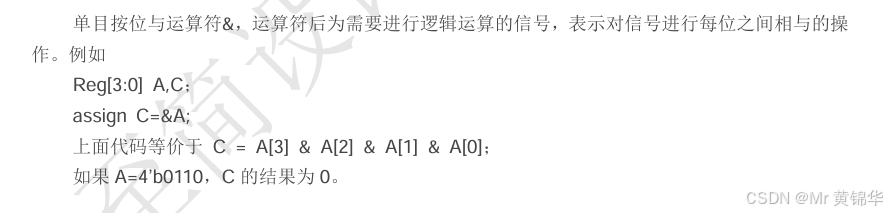

二、单目按位与

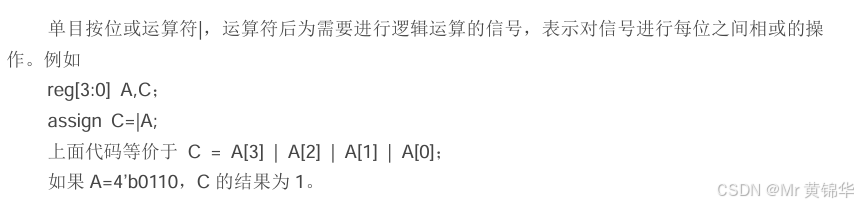

三、单目按位或

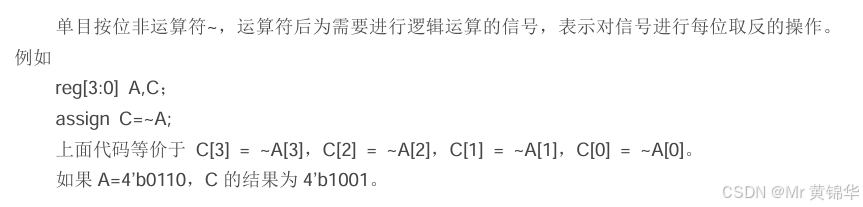

四、单目按位非

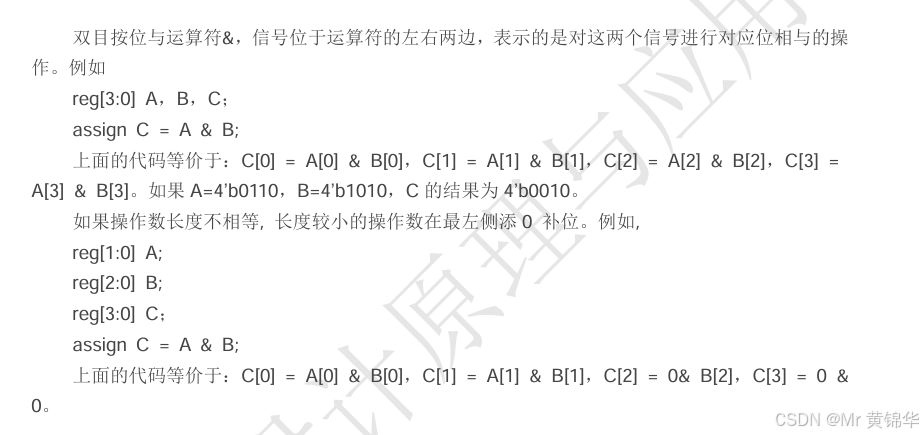

五、双目按位与

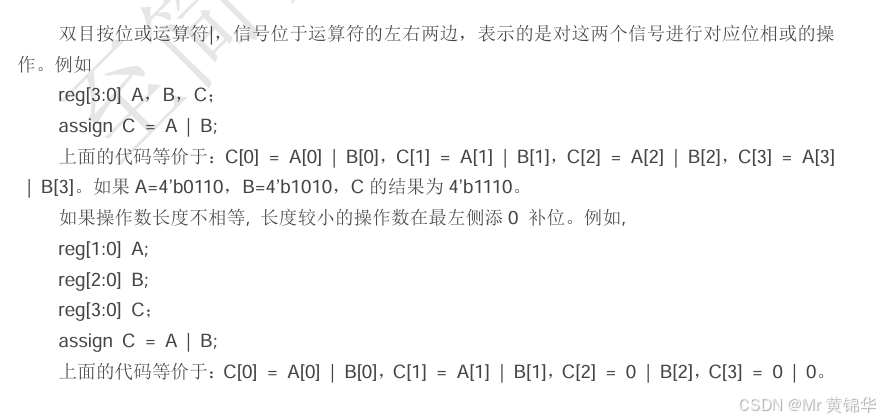

六、双目按位或

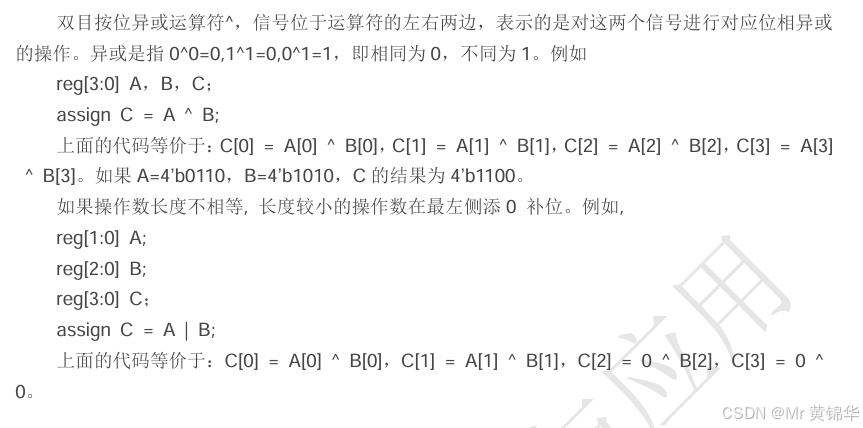

七、双目按位异或

八、经验总结

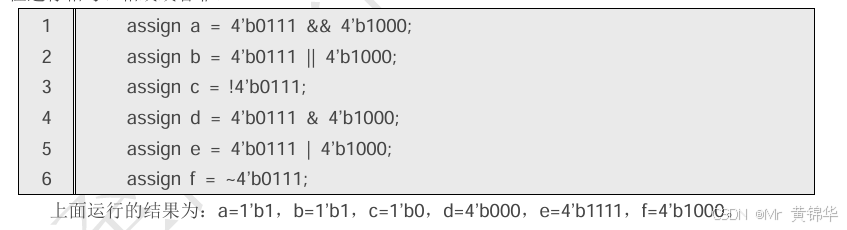

1.逻辑运算符和位运算符有什么区别呢?

将逻辑与“&&”和按位与“&”进行对比可以看出,逻辑与运算符的运算只有逻辑真或逻辑假两 种结果,即1或0;而“&”是位运算符,用于两个多位宽数据操作。对于位运算符操作,两个数按 位进行相与、相或或者非。

867

867

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?