将上一篇中,使用start方法发送item/sequence的过程,封装成了uvm_do系列宏。

上一篇链接:UVM-使用start发送item,sequence

需要了解的是,本篇文章的这些uvm_do系列宏,只能在sequence中使用!

例如想在test中发送sequence请使用start

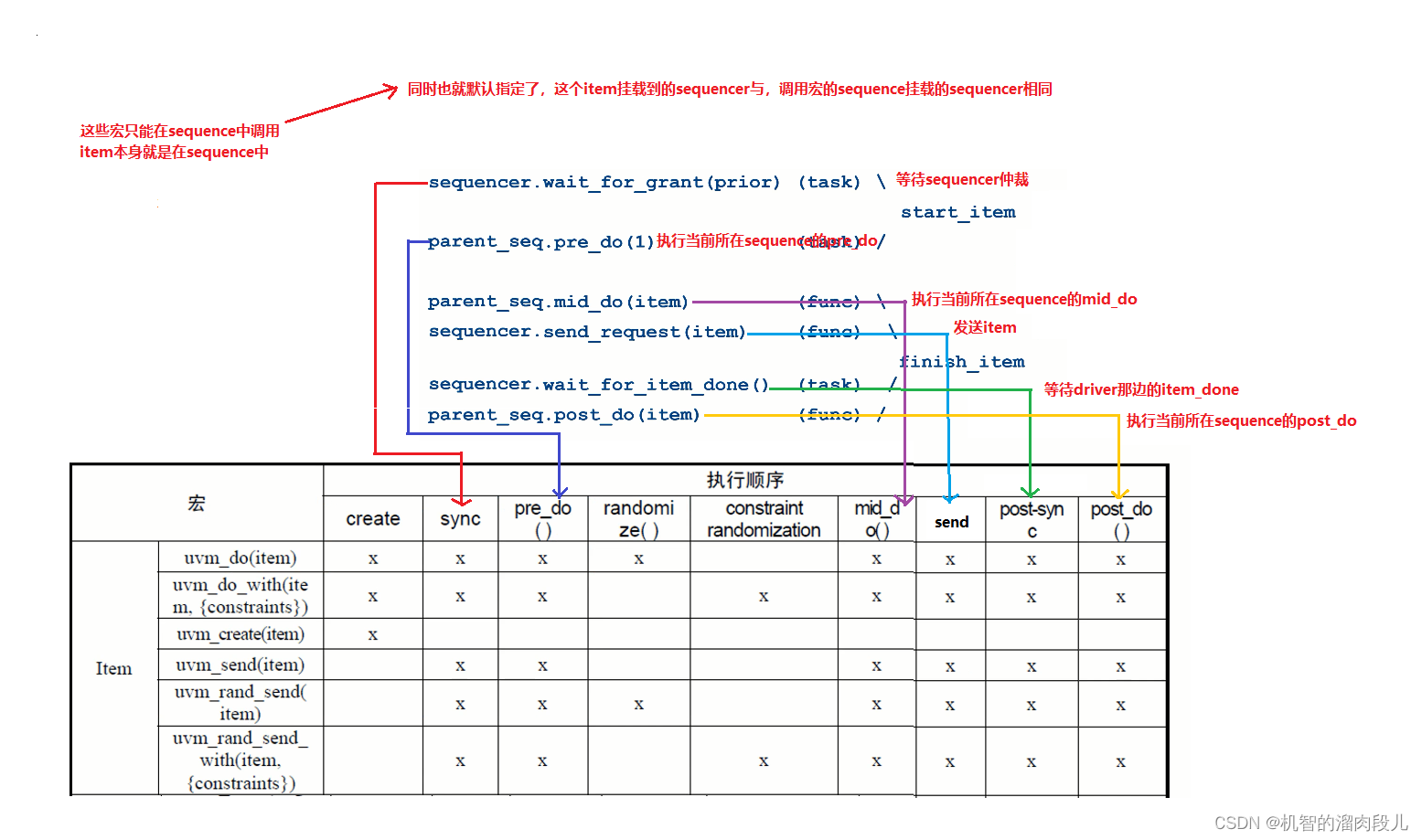

1#item do系列

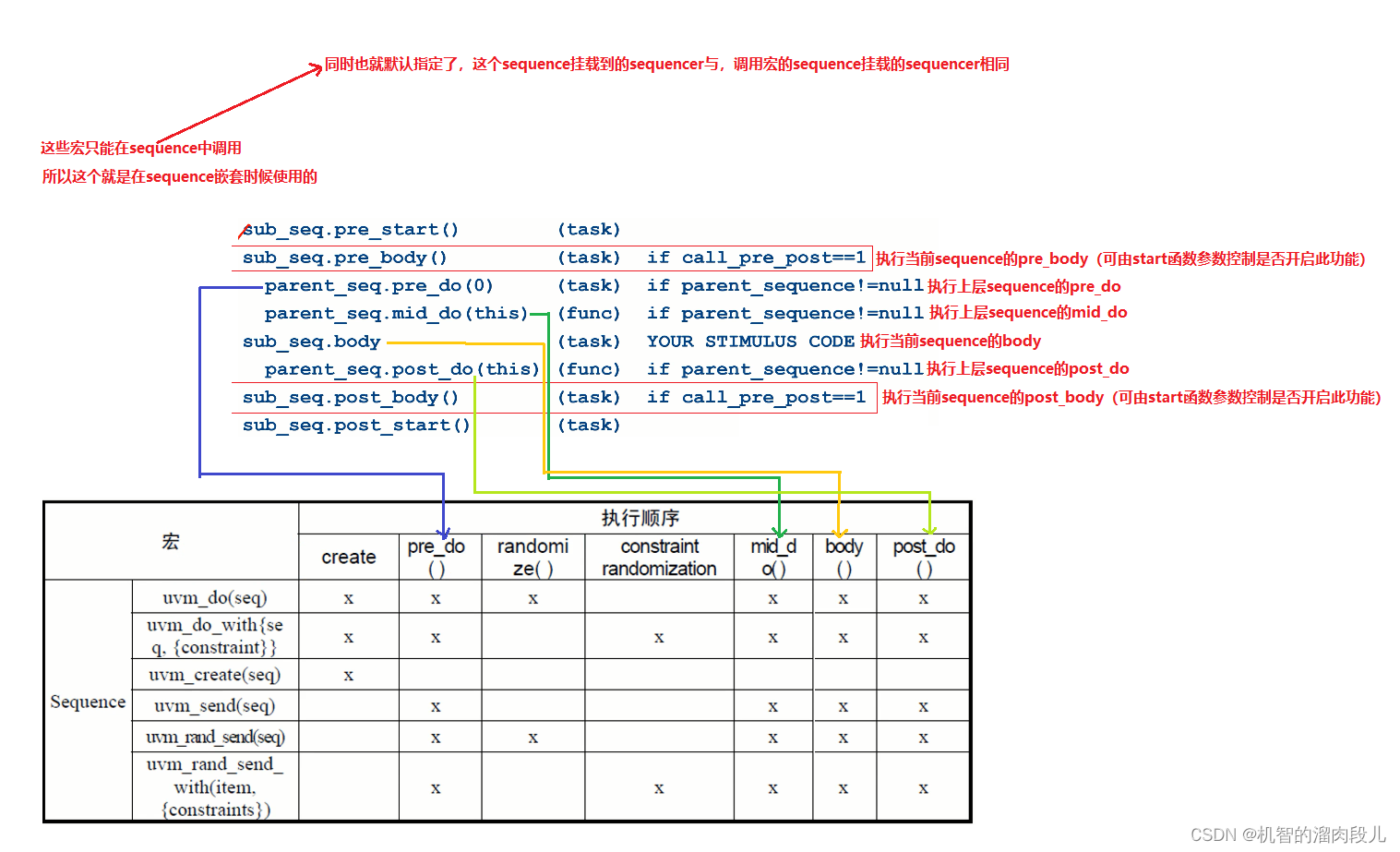

2#sequence do系列

还有一部分宏,可以设置并发sequence时候,sequencer仲裁sequence的优先级,将在下一节讲述

链接如下:UVM-sequencer的仲裁

示例

package pack1; //pack1头

import uvm_pkg::*; //+UVM

`include "uvm_macros.svh"//+工厂

class item extends uvm_sequence_item;

rand int data_auto;

`uvm_object_utils_begin(item)

`uvm_field_int(data_auto,UVM_ALL_ON)

`uvm_object_utils_end

function new(string name = "item");

super.new(name);

endfunction

endclass

//===========相比上一节,此代码只对这两个sequence做出了改动==================

//底层sequence

class child_seq extends uvm_sequence;

`uvm_object_utils(child_seq)

function new(string name = "child_seq");

super.new(name);

endfunction

task body();

item req;

`uvm_do_with(req,{data_auto == 66;})//对item进行:实例化+随机+发送

endtask

endclass

//顶层sequence

class top_seq extends uvm_sequence;

`uvm_object_utils(top_seq)

function new(string name = "top_seq");

super.new(name);

endfunction

task body();

item req;

child_seq cseq;

`uvm_do_with(req,{data_auto == 99;})//对item进行:实例化+约束+发送

`uvm_do(cseq)//sequence进行:实例化+发送

endtask

endclass

//===========================================================================

class seqr extends uvm_sequencer;

`uvm_component_utils(seqr)

function new(string name = "seqr", uvm_component parent = null);

super.new(name, parent);

endfunction

endclass

class dri extends uvm_driver;

`uvm_component_utils(dri)

function new(string name = "dri", uvm_component parent = null);

super.new(name, parent);

endfunction

task run_phase(uvm_phase phase);

uvm_sequence_item temp ;

item req;

forever begin

seq_item_port.get_next_item(temp);

void'($cast(req,temp));

`uvm_info("driver","driver already recive item", UVM_LOW)

`uvm_info("data_auto",$sformatf("%d",req.data_auto), UVM_LOW)

//只告诉完成,不发送响应(response)

seq_item_port.item_done();

end

endtask

endclass

class env extends uvm_env;

seqr seqr0;

dri dri0;

`uvm_component_utils(env)

function new(string name="env" ,uvm_component parent = null);

super.new(name,parent);

endfunction

function void build_phase(uvm_phase phase);

seqr0 = seqr::type_id::create("seqr0",this);

dri0 = dri::type_id::create("dri0",this);

endfunction

function void connect_phase(uvm_phase phase);

dri0.seq_item_port.connect(seqr0.seq_item_export);

endfunction

endclass

class test1 extends uvm_test;

env env0;

`uvm_component_utils(test1)

function new(string name = "test1", uvm_component parent = null);

super.new(name, parent);

endfunction

function void build_phase(uvm_phase phase);

super.build_phase(phase);

env0 = env::type_id::create("env0",this);

`uvm_info("test1",$sformatf("build"), UVM_LOW)

endfunction

task run_phase(uvm_phase phase);

top_seq seq0;

phase.raise_objection(this);

`uvm_info("test1",$sformatf("run"), UVM_LOW)

seq0 = new();

seq0.start(env0.seqr0);

phase.drop_objection(this);//退出run_phase需要先落手

endtask

endclass

endpackage

//--------------------------------------module---------------------------------

module hardware1;

import pack1::*;

import uvm_pkg::*; //+UVM

initial begin

run_test("test1");

end

endmodule

本文详细介绍了UVM_do宏在System Verilog中的应用,特别是如何使用itemdo和sequencedo系列宏来简化测试序列的创建过程。通过示例展示了如何在不同层级的sequence中运用这些宏来实现item和sequence的实例化、随机化及发送。

本文详细介绍了UVM_do宏在System Verilog中的应用,特别是如何使用itemdo和sequencedo系列宏来简化测试序列的创建过程。通过示例展示了如何在不同层级的sequence中运用这些宏来实现item和sequence的实例化、随机化及发送。

8511

8511

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?