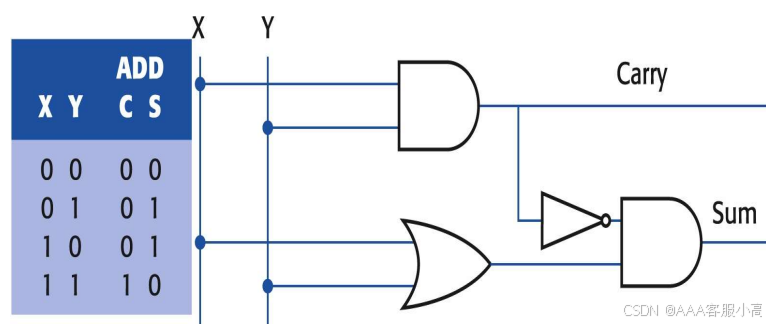

Half-Adder(半加器)设计

• 功能:

• 用于两个单比特(二进制位)数字的加法。

• 输入:X, Y。

• 输出:

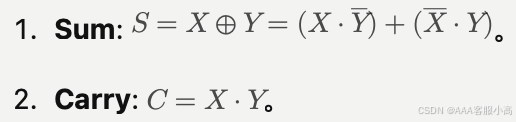

• Sum(和):用 XOR 实现。

• Carry(进位):用 AND 实现。

逻辑表达式

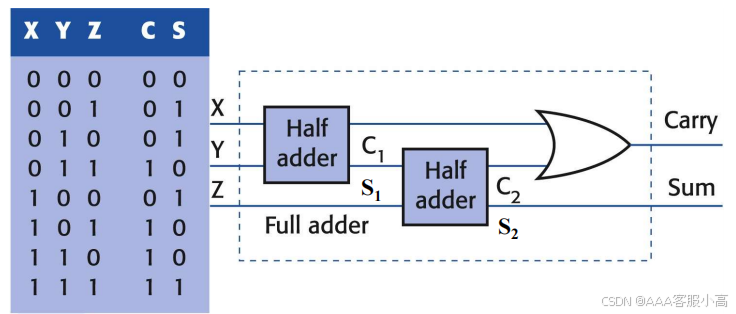

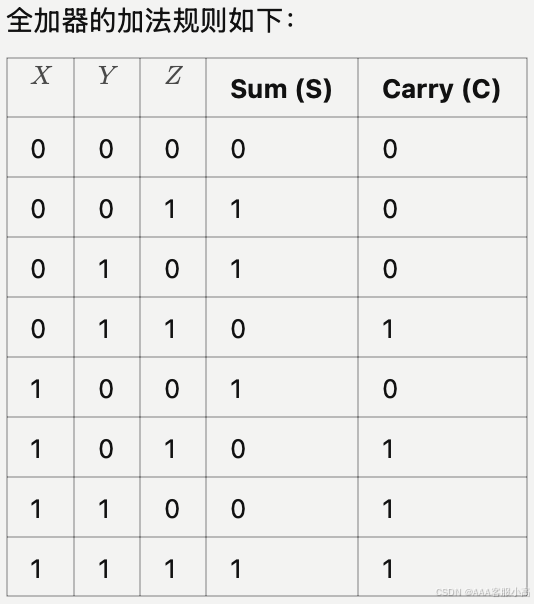

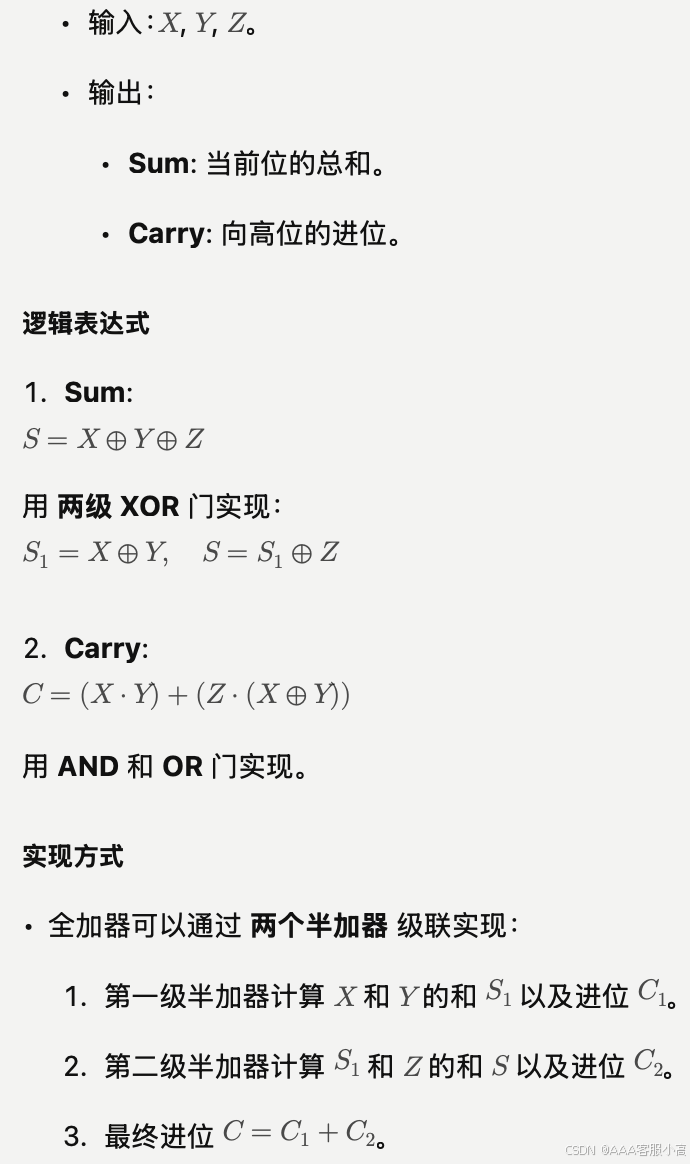

Full-Adder(全加器)设计

• 功能:

• 用于处理三比特加法,第三比特通常是从前一级进位而来的 Carry-In。

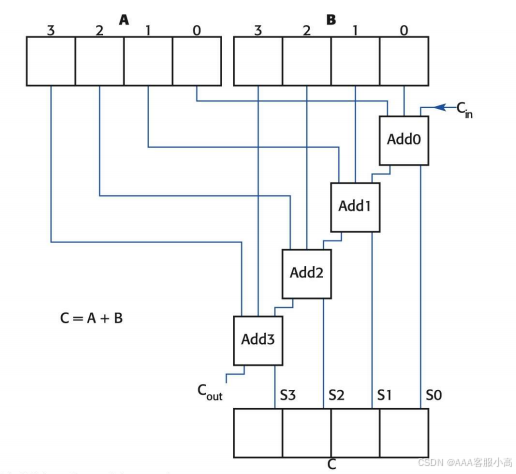

扩展 4 位全加器至 8 位全加器

原理:

• 全加器的级联设计允许多位加法。

• 对于 8 位全加器:

1. 将 8 个全加器串联,每个全加器处理一位的加法。

2. 最高位的进位 C_{\text{out}} 由前面的加法器产生。

实现方法:

1. 使用 8 个全加器模块。

组合逻辑电路与时序逻辑电路

组合逻辑电路:Combinational (combinatorial) logic circuits

• 定义:

• 输出仅依赖于当前的输入。

• 没有记忆功能。No memory

• 特点:

• 所有之前学过的加法器、选择器等都是组合逻辑电路。

• 优点:速度快。

• 缺点:无法处理序列化任务。

时序逻辑电路:Sequential logic circuits.

• 定义:

• 输出依赖于输入和当前的电路状态。

• 具有记忆功能。memory

• 特点:

• 需要存储器件(如触发器)。

• 优点:可以处理时序任务,例如计数器和寄存器。

• 缺点:设计更复杂,速度较慢。

总结

• Half-Adder 和 Full-Adder 是加法器设计的核心组件。

• 多位加法器可以通过级联多个全加器模块实现(如 4 位扩展至 8 位)。

• 组合逻辑和时序逻辑的差异主要在于是否有记忆能力,前者用于瞬时计算,后者用于复杂时序任务。

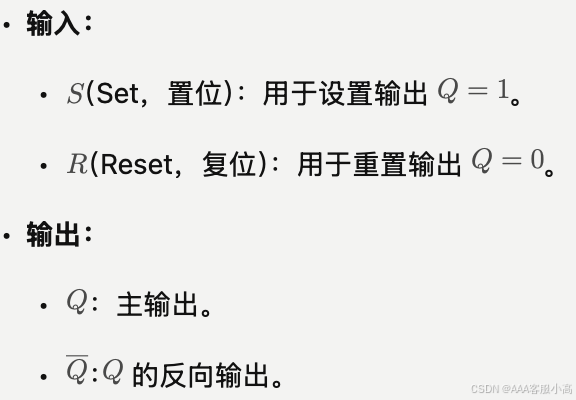

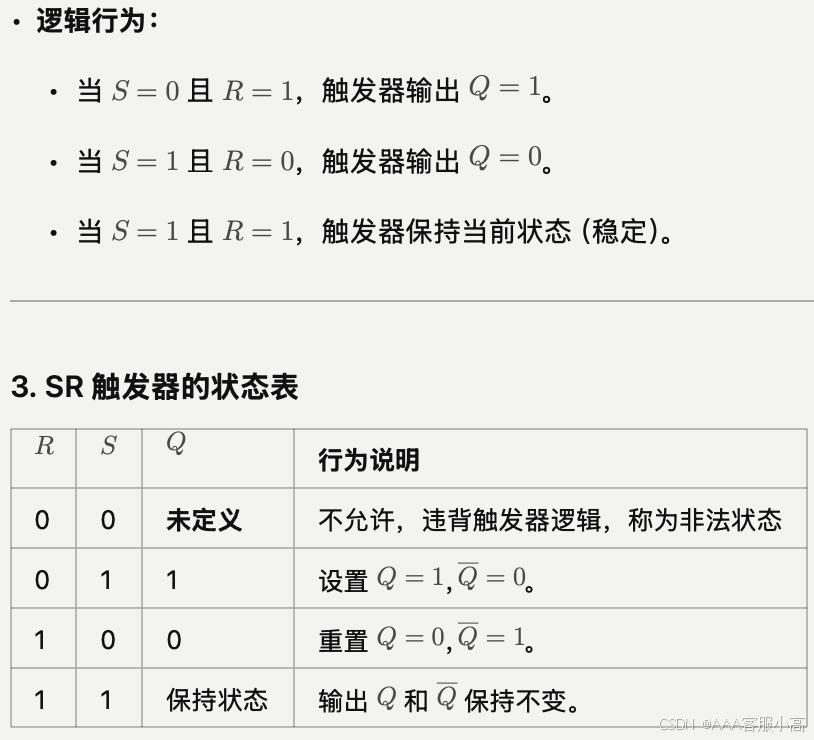

SR 触发器(Set-Reset Flip-Flop)

1. 什么是 SR 触发器?

• SR 触发器是一种简单的 存储单元,是时序电路的基本元件。

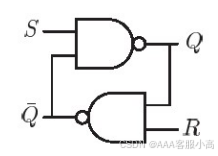

• 它由两个逻辑门(通常是 NAND 或 NOR 门)交叉连接组成。

SR 触发器的实现

NAND 门实现

• 图中显示了用两个 NAND 门实现的 SR 触发器。

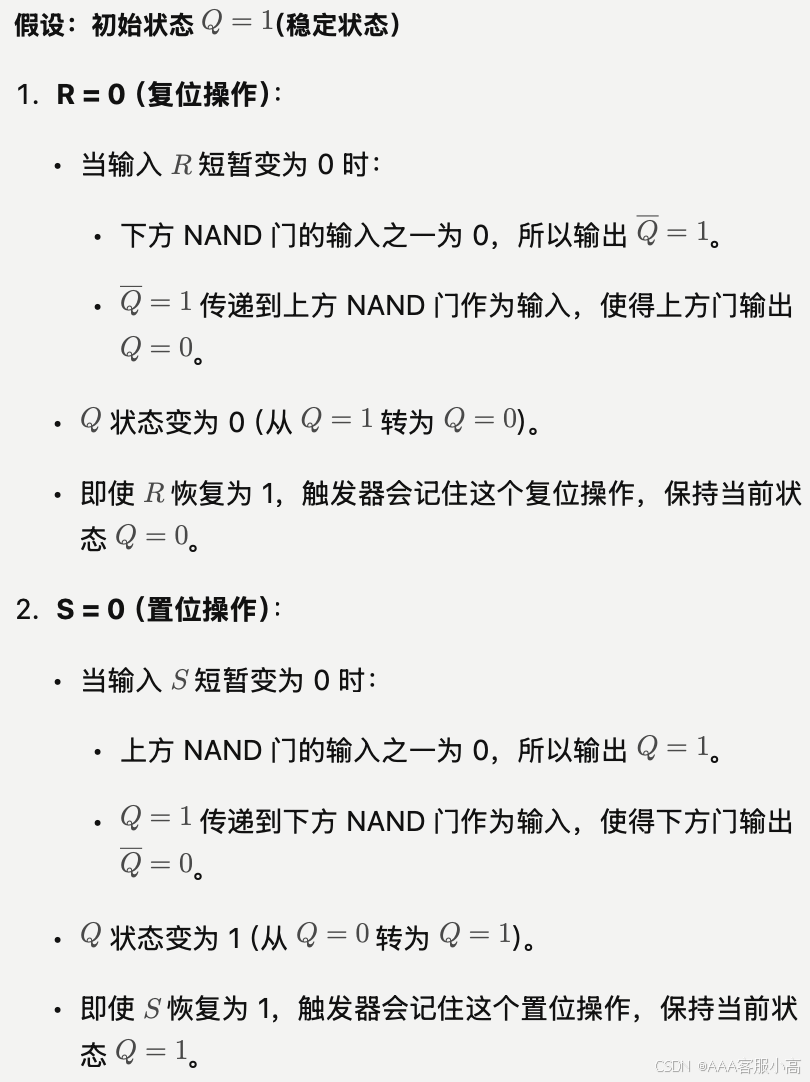

SR 触发器的稳定状态

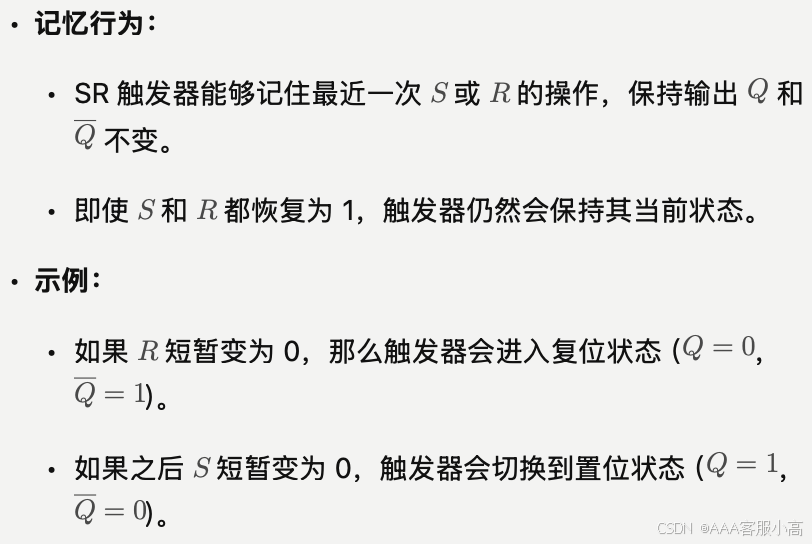

• 当 S = 1,R = 1时,触发器保持其当前状态,称为稳定状态。

• 当S 或 R被短暂设置为 0 时,触发器的状态会被切换到新的稳定状态。

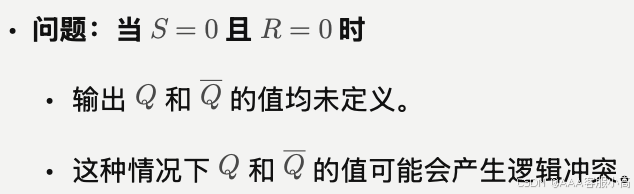

特殊情况:非法状态

逻辑行为示例

状态切换过程

SR 触发器的记忆特性

• 记忆功能:

• SR 触发器可以记住最后一个 Set 或 Reset 的操作状态。

• 用途:

• 用于存储单比特数据。

• 是更复杂时序电路(如寄存器、计数器等)的核心元件。

SR 触发器是更高级触发器(如 D 触发器和 JK 触发器)的基础。

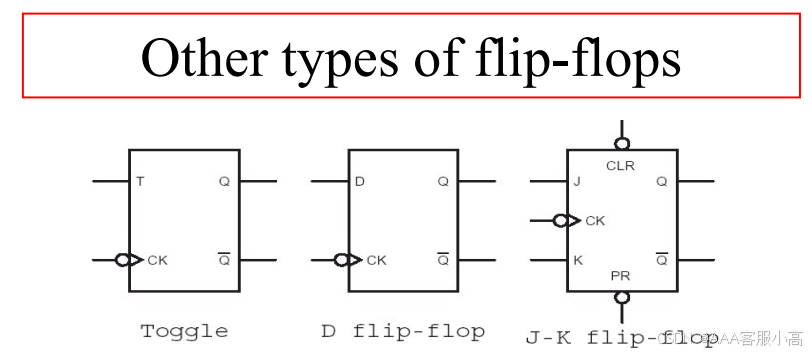

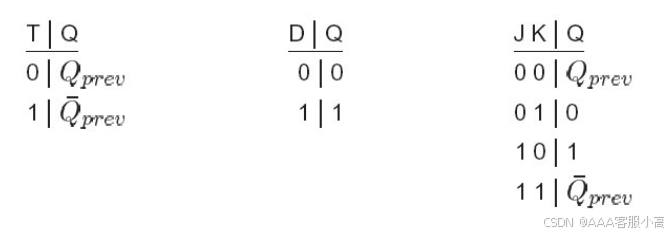

所有的触发器(flip-flops)都有一个标记为时钟(clock)的输入端。当时钟端接收到脉冲信号,即从高电平(1)短暂地变为低电平(0)时,触发器会产生新的输出。另外,CLR(清除)和PR(置位)输入端被用来将触发器初始化到已知的值(CLR为0,PR为1)。

1. 触发器(Flip-flops):触发器是一种数字电路组件,它能存储一位二进制信息。在接收到特定的时钟信号后,它会改变其输出状态,常用于构成存储器和计数器等数字系统。

2. 时钟(Clock):在数字电路中,时钟信号是周期性的脉冲波形,用来同步电路中不同部分的操作。触发器利用时钟信号的上升沿或下降沿(本例中为从1到0的变化)来触发状态的改变。

3. 清除(Clear, CLR)和置位(Preset, PR):CLR和PR是触发器的两个控制输入端,用于将触发器的状态设置为预定义的值。CLR通常用于将触发器的输出设置为0,而PR则用于将输出设置为1,这在电路初始化或复位时非常有用。

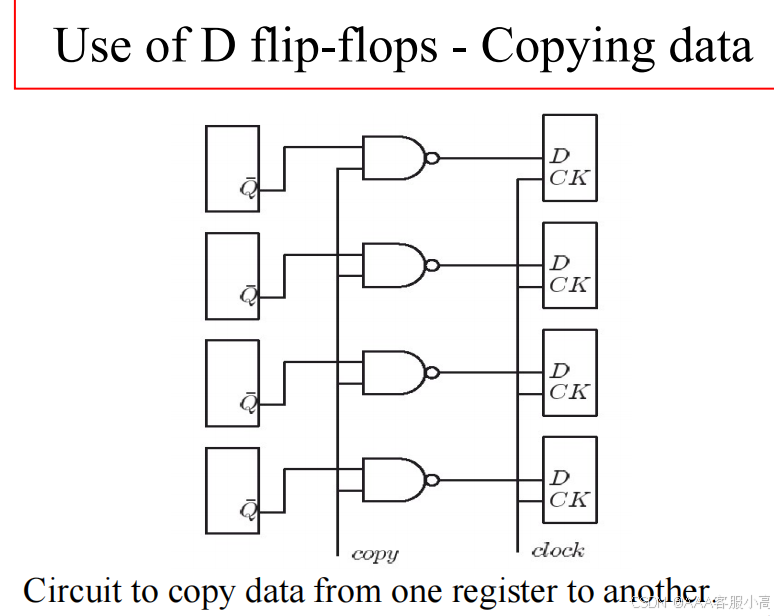

D触发器用于寄存器:

• 图示展示了多个 D触发器连接在一起,用于实现数据从一个寄存器复制到另一个寄存器。

Q1: 什么类型的触发器有非法状态?

• SR触发器(Set-Reset Flip-Flop):

• 当 S = 0, R = 0 时,输出 Q 和 \overline{Q} 都为 1,这种状态是非法的。

Q2: 什么类型的触发器允许我们复制数据?

• D触发器(Data Flip-Flop):

• 通过输入 D 和时钟信号 CK,可以将输入 D 的值存储到输出 Q 中,从而实现数据的复制。

Q3: 哪种电路具有“记忆”功能?

• 时序逻辑电路:

• 包含触发器(如 SR、D、T、JK 触发器)的电路具有“记忆”功能。

• 它们能够记住输入信号的历史状态。

总结

• T 触发器:用于计数器设计。(多个 T触发器级联可以实现二进制计数)

• D 触发器:用于数据同步与存储,是寄存器的核心元件。

• JK 触发器:功能最强大,适合多种应用。

• SR 触发器:简单但受限于非法状态,需要注意设计约束。

1263

1263

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?