面向77–81吉赫调频连续波雷达工作的低功耗有源标签设计

M. 萨迪赫·达达什 , IEEE学生会员, 于尔根·哈施, IEEE高级会员, 帕斯卡尔·舍瓦利耶, IEEE会员, 安德烈亚·卡特林, IEEE高级会员, Ned Cahoon, 和 Sorin P. Voinigescu, IEEE会士

摘要—本文详细讨论了基于硅的低功耗毫米波(mm‐wave) 有源标签的系统级和晶体管级设计。分别在55纳米SiGe BiCMOS和45纳米SOI CMOS工艺中设计并制造了两个具有相同系统架构、焊盘框和芯片尺寸的有源毫米波标签。该标签包含三级低噪声放大器(LNA)、唤醒检测器、BPSK调制器以及两级可变增益输出级,每级驱动一个独立的发射天线并以反相方式工作。唤醒检测器可用于关闭除LNA和检测器以外的所有模块,从而进一步降低功耗。实测结果显示,SiGe和SOI芯片的性能非常接近:增益分别为19 dB和20 dB,噪声系数为9 dB和8 dB,功耗分别为 25/10.8毫瓦(工作/空闲状态)和18毫瓦。SiGe标签通过倒装方式安装在带有1个接收天线和2个发射天线的微型PCB上,并在5米距离内进行了系统级功能测试。实测的SiGe标签唤醒灵敏度为 −62 dBm,与仿真结果高度一致。

索引术语—有源标签,天线,BPSK调制器,检波器,调频连续波雷达, 低噪声放大器(LNA),毫米波(mm‐wave),SiGe BiCMOS,SOI CMOS,唤醒功能。

引言

近年来,我们见证了配备在77–81 吉赫兹频段运行的 FMCW远距和中距雷达的车辆迅速普及。随着自动驾驶车辆即将投入使用,这些雷达系统将变得无处不在。因此,在该频段运行的低功耗毫米波(mm‐wave)标签(也称为后向散射器或反射器)[1],[2]可作为自主导航中目标识别的非常有用的辅助手段。

在图1所示的潜在使用场景中,安装在车辆中的调频连续波雷达充当基站。它首先询问标签,然后读取由标签放大并用本地信息调制后的返回信号。最初,标签处于空闲模式,功耗很低。

一旦它对 incoming FMCW信号进行预放大并检测到该信号,便会启动以对该信号进行调制并进一步放大,然后再将其“反射”回基站。

其他可能的应用包括用于自主割草机、吹雪机和类似自主机器人的边界定义。

直到最近,除了一个工作在34 GHz、功耗为122 毫瓦的有源标签外,毫米波频段内报道的均为无源标签。尽管无源标签具有超低功耗的优点,但它们存在信号损耗和灵敏度差的问题,严重限制了其工作距离。最近,我们展示了两款基于55纳米SiGe BiCMOS和45纳米SOI CMOS工艺制造的77–81吉赫超低功耗有源标签,并采用了专用的毫米波后端布线(BEOL)。

本文在第二节中讨论了这些标签的系统级规格,并在第三节中探讨了哪种工艺后端和晶体管优值系数(FoMs)决定了最小功耗。第四节介绍了低功耗电路拓扑结构和设计方法,并比较了在55‐nm SiGe BiCMOS和 45‐nm SOI CMOS工艺中每个电路模块的具体实现。第五节简要回顾了制造和封装,而第六节详细介绍了裸片级别和封装内的实验表征,并报告了在消声室内进行的超过 5米的系统级实验。

二、无线电链路预算

设计目标是利用现有的FMCW远距和中距雷达系统以及一个具有最低功耗的超小型标签,建立一条10米链路。

假设基站的发射输出功率PTX为10 dBm,天线增益GTRX为20 dBi,接收机噪声系数为10 dB。标签的天线增益指定为6 dBi,接收机噪声系数为9 dB,增益

表 I 基站和有源标签系统参数

| 参数 | 基站 | 有源标签 |

|---|---|---|

| 发射功率 (PTX) | 10 dBm | - |

| 天线增益 (GTRX/Gtag) | 20 dBi | 6 dBi |

| 接收机噪声系数 | 10 dB | 9 dB |

| 增益 | - | 20 dB |

| 调制带宽 | - | 10–100 kHz |

| 3 dB 带宽 | - | ≥5 GHz |

20 dB,调制带宽为10–100千赫兹。标签的3分贝带宽必须至少为5 GHz,覆盖77–81吉赫频段并留有一定余量。

需要明确的是,在空闲模式下,标签作为低噪声辐射计运行。唤醒功能灵敏度由低噪声放大器(LNA)‐检测模块的响应度(RESP)和噪声等效功率(NEP)决定。

较大的射频带宽会降低其灵敏度。假设标签的唤醒功能灵敏度优于 −62 dBm。基站和有源标签在链路预算分析中所使用的参数汇总见表 I。

可以使用弗里斯传输方程来计算标签在下行链路中接收到的信号功率

$$

PR,tag= PTXGTRXGtagλ^2 / (4πd)^2

$$

(1)

其中 λ是自由空间波长,d是基站与标签之间的距离。

对于在25米距离上传播的77吉赫兹信号,自由空间损耗 (FSL)变为

$$

FSL= 20× \log( 4πd / λ)= 98 \text{ dB}.

$$

(2)

利用(1)和(2),可计算标签处的接收信号功率

$$

PR,tag= PTX+ GTRX+ Gtag −FSL= −62 \text{ dBm}.

$$

(3)

该值等于唤醒检测器的灵敏度,并限制其下行链路操作。

因此,给定标签增益Atag为20 dB时,其输出功率变为

$$

PT,tag= PR,tag+ Atag \quad \text{if} \quad PR,tag > −62 \text{ dBm}.

$$

(4)

基站接收机中的可检测最低功率电平Si可以表示为

$$

Si= −174 \text{ dBm}+ \text{SNR}

{\text{min}}+ \text{NF}

{\text{RX}}+ 10 \log(\text{BW}_{\text{mod}})

$$

(5)

其中SNRmin表示基站接收机所需的最小信噪比,N FRX为其接收机噪声系数,BW mod 为标签的基带调制频率。对于给定的

图2展示了在两种不同的标签调制带宽下,最大链路距离随基站接收机信噪比的变化情况,包含和不包含唤醒功能的情形。

如果标签中的所有电路始终处于激活状态,则在10千赫调制带宽和14分贝信噪比下,链路距离可超过20米。然而,在需要唤醒功能且标签大部分电路处于空闲状态的情况下,最大链路距离由标签在下行链路中的唤醒功能灵敏度决定。

根据先前发表的研究[7],[8],,标签的唤醒灵敏度预计主要受标签响应度和噪声等效功率的影响。因此,必须在唤醒检测器前放置一个具有高增益(超过25分贝[8])和低噪声系数的低噪声放大器,以改善噪声等效功率。此外,标签的响应度必须足够大,以满足所需的唤醒功能灵敏度。

III. W波段工艺性能指标

采用意法半导体的55纳米SiGe BiCMOS技术和格芯的45纳米SOI CMOS技术实现毫米波有源标签集成电路的物理设计。

第一种工艺采用55纳米MOSFET,具有高、低Vt以及完全布线的 n型MOSFET,其fT/fMAX达到280/300 GHz;同时包含三种类型的发射极宽度为100纳米的SiGe HBT,其完全布线的fT /fMAX达到300/330 GHz;此外,还具备九层金属后端互连工艺,包含厚度为3‐μm的顶层铜层和厚度为1.4‐μm的铝电容层[13]。

部分耗尽型SOI‐CMOS工艺的后端互连工艺包含11个金属层,其中包括两层1.2‐μm厚的顶层铜层和2.1‐μm厚的 Alucap。测得栅指宽度为770 nm、最小栅长为40 nm的完全布线n型MOSFET的fT和fMAX均为250 GHz [9]。

两种技术均采用电阻率为 10−×cm的硅p型衬底。

由于该应用中的一个关键设计目标是最小化标签的功耗,因此最重要的技术品质因数是:1)最小尺寸放大器级的功率增益;2)W波段匹配网络的品质因数。后者取决于后端互连工艺和硅衬底的电阻率。

A. 最小尺寸共源共栅结构的功率增益

对于给定的偏置电流,共源共栅结构相比共发射极/源极和共基极/栅极拓扑结构可提供超过3分贝的更高增益和更好的隔离度。图3比较了在两种工艺中,不同最小尺寸共源共栅级在80 GHz时的模拟最大可用增益(MAG)随偏置电流的变化情况。在55纳米SiGe BiCMOS工艺中,HBT–HBT和 MOS–HBT共源共栅结构在0.5毫安时分别表现出15分贝和 12.5分贝的最高峰值增益。在所有小于1毫安的偏置电流下,它们的增益均高于45纳米SOI‐CMOS和55纳米MOSFET共源共栅结构。45纳米SOI CMOS共源共栅结构在0.7毫安时的峰值稳定功率增益为11.5分贝,而55纳米MOS‐MOS共源共栅结构在0.5毫安时为11分贝。所有MOSFET器件的栅指均采用两侧接触,以最小化栅极电阻并最大化fMAX。

如前所述,为了最小化功耗,人们可能会倾向于在所有电路模块中使用最小尺寸的HBT和MOSFET。然而,图4表明,由于寄生电容和边缘电容等周边效应,最小尺寸HBT的功率增益显著降低。采用较大尺寸HBT共源共栅结构可在所有偏置电流下获得更高的增益。这一效应在 MOS‐MOS共源共栅结构中较不明显,其最大可用增益仅取决于固定为770纳米的栅指宽度,而不受并联栅指数量的影响。上述所有仿真均在提取版图寄生参数后进行。

B. 匹配网络品质因数Q对共源共栅级增益的影响

图5 总结了图4中 共源共栅结构 的 输入和输出阻抗 值以及每种情况下进行 级间匹配 所需的 电感 值。显然,除了较低的 增益 外,最小尺寸的 共源共栅结构表现出非常大的级间阻抗和很高的品质因数Q。相应的匹配网络需要非常大的电感值,这在80 GHz下无法实现足够高的自谐振频率(SRF)。

为了评估两种后端工艺(BEOL)的性能并了解其局限性,采用准三维电磁仿真器对在两种BEOL中使用相同布局、形成于最上三层金属层的210 pH垂直串联叠堆电感进行了仿真。该电感布局的直径为30‐μm,金属线宽为 4‐μm,如图6所示。从仿真得到的S参数中提取的有效电感L和品质因数Q随频率的变化曲线示于图7。尽管这两种BEOL的顶层金属厚度和总介质厚度略有不同,但在 SiGe BiCMOS和SOI技术中分别获得了相似的峰值品质因数16.5以及自谐振频率155/160 GHz。有效Q在70–75 GHz处达到峰值。此外还增加了一组曲线,表示当SOI衬底电阻率从 10 ×cm变为高电阻率选项 1000 × cm时的情况。可以看出,衬底电阻率对这些毫米波电感设计实际上几乎没有影响。

因为电感占位面积小且采用了垂直耦合。该L × SRF 乘 积为 32 GHz×nH。由于电感的自谐振频率必须至少为其使用频率的两倍,因此在这些技术中,在80 GHz下不应使用大于200皮亨的电感值。

最后,如果在电感设计中使用2‐μm宽的金属线,则在 SiGe BiCMOS工艺中可实现更好的L × SRF乘积,达到 36 GHz×nH,同时保持相近的峰值Q值为15。对于相同的 210皮亨电感值,电感占位面积减小至直径 26 μm,使自谐振频率提高到180吉赫。

在80 GHz下,匹配网络的品质因数对SiGe HBT‐HBT 和SOI CMOS共源共栅级增益的影响在图8中作为偏置电流的函数进行了仿真。当电感器Q从10增加到20时,最大可用增益提高了3 dB以上。同样值得注意的是,当电感器Q为20时,采用无限Q电感器的HBT‐共源共栅的增益从图4中的23 dB 下降到17 dB。当匹配网络Q从无穷大变为20时,SOI MOSFET共源共栅的最大可用增益退化可忽略不计。后者可通过检查图5表格中的数据来解释。SOI MOS‐MOS共源共栅的输出阻抗的品质因数为3,而

HBT–HBT共源共栅的输出阻抗具有Q值为15。因此, HBT共源共栅的最大可用增益对输出匹配网络的品质因数变化更为敏感。

IV. 超低功耗晶体管级设计

所提出的毫米波标签的框图如图9所示。接收到的 FMCW信号经三级低噪声放大器放大后,同时送入检波器和BPSK调制器。BPSK调制器的p和n输出连接到两个不同的可变增益输出级,每个输出级分别驱动一个极性相反的发射天线。如果低噪声放大器输入焊盘处的信号大于 −62 dBm,检波器输出电压将触发,可用于唤醒BPSK调制器和两个处于睡眠模式且无偏置的可变增益输出级。

由于两个发射天线上的信号为180°反相,并且具有独立可调的幅度,因此可以抵消或至少最小化泄漏到接收天线的信号,从而避免正反馈和可能的振荡。通过适当的天线间距和方向,可以进一步降低天线间隔离度。在实际应用场景中,处理器芯片将与标签共封装。该处理器将读取检波器输出信号,并向标签提供偏置唤醒、调制以及增益控制信号。

每个电路模块的设计与实现将在第四节A至D部分中更详细地讨论。SOI标签由单一的1.2伏电源供电,而 SiGe标签设计为在1.8至2.5伏的电源电压下工作。

A. 低噪声放大器

三阶SiGe和SOI低噪声放大器的电路图完全相同,分别在图10和图11中重现。输入级采用并串联变压器反馈,以实现宽带阻抗和噪声匹配。450飞法和500飞法电容器的作用是在电源节点以及每个共源共栅级的顶层异质结双极晶体管/金属氧化物半导体场效应晶体管的基极/栅极处提供低电感的交流接地。在SiGe低噪声放大器中,采用电阻式发射极退化技术,以在温度和工艺变化下稳定直流工作点,并使其对版图接地电阻不敏感。所产生的噪声由发射极退化电阻在高频时被500飞法电容器旁路。

在SOI低噪声放大器中,无需使用电阻退化,因为金属氧化物半导体场效应晶体管的偏置电流对地电阻变化的敏感性较低,这是由于漏极电流与VGS呈线性(而非指数)关系。根据第三节的分析,所有异质结双极晶体管的发射极长度均设计为1.18 μm,并在1.3 mA/μm的峰值‐fMAX集电极电流密度下偏置,以实现最大增益。在SOI低噪声放大器中,所有晶体管均采用40纳米物理栅长和770纳米栅指宽度,并在0.3 mA/μm的峰值‐fMAX电流密度下偏置,以在最大化增益的同时最小化噪声系数。此外,输入级略大于后续各级,以利于输入噪声匹配。对于硅锗低噪声放大器,未通过增大输入异质结双极晶体管共源共栅结构的尺寸来改善噪声匹配,从而优化噪声系数。

B. BPSK调制器

BPSK调制器采用双平衡Gilbert单元结构实现,如图 12(a)和(b)所示。使用变压器实现单端到差分的转换,并将调制器输入阻抗共轭匹配至前一级的输出。为了在功耗与匹配网络可实现性之间取得折衷,在SiGe和SOI标签中分别采用了接近最小尺寸、发射极长度为0.5‐μm的SiGe HBT以及四指nMOSFETs。混频四边形电路中的所有晶体管均偏置在峰值fMAX电流密度的一半,以最大化开关速度和增益[14]。

C. 检测器

对于SiGe标签,唤醒检测器与BPSK调制器的输入端并联连接[图12(a)]。它采用共发射极差分对,并使用宽摆幅pMOSFET电流镜负载实现差分到单端的转换。电流镜输出驱动一个2.5 V厚氧化层CMOS反相器,该反相器开启或关闭BPSK调制器以及两个可变增益输出级中的偏置电流。该差分对采用最小尺寸HBT,以最大化检测器响应度。有源共源共栅负载提供高增益,在最小电流消耗下最大化检测器响应度。在给定电源电压的情况下,该结构相比电阻负载具有更高的输出电阻,因而响应度更高 [7],[8]。然而,pMOSFET负载会增加1/f噪声拐点。

270‐fF MoM电容器的作用是滤除任何泄漏到检测器输出端的毫米波信号。

在SOI标签中,唤醒检测器嵌入在调制器级中,并采用共栅差分拓扑结构,插入虚拟BPSK调制器以实现对称性和电源抑制。该检测器放大输入差分对源极处形成的共模信号,该信号与输入信号功率成正比。由于纳米级 CMOS检测器在毫米波频率下的噪声等效功率和响应度明显劣于硅锗

HBT器件[7],[8],在CMOS检测器后增加了一个增益级,以进一步提高其响应度。由于金属氧化物半导体场效应晶体管尺寸较小且具有额外的增益级,CMOS检测器对偏移电压较为敏感。这在SiGe HBT检测器中不是问题。

图13中模拟了两种标签的响应度和噪声等效功率,结果显示硅锗版本具有明显优势,符合预期[8]。

图14展示了仿真检测器输出波形随接收输入信号功率的变化。SiGe标签在 −62 dBm时唤醒,而SOI版本在 −56 dBm时触发,由于其响应度较低,需要更长时间才能稳定。

D. 可变增益放大器

SiGe和SOI可变增益放大器(VGA)的电路图如图 15所示。前者采用共基极拓扑,而后者采用共源共栅拓扑

采用SOI工艺实现。通过将电流从主放大器路径 steering 至交流接地,利用经典拓扑结构实现增益控制, Q1,经 Q2实现。在SOI版本中,一个尺寸更小的n型 MOSFET Q2与主共栅晶体管 Q1并联放置。为了最小化 Q2的电容寄生效应并保持对称布局,将 Q2的有源区与 Q1的有源区合并。仅在 Q1的两侧各增加两个额外的栅指。

通过电阻分压器将 Q2的栅极电压固定在0.85 V,而 Q1的栅极电压则连接到外部焊盘以实现增益控制。

V. 芯片制造与封装

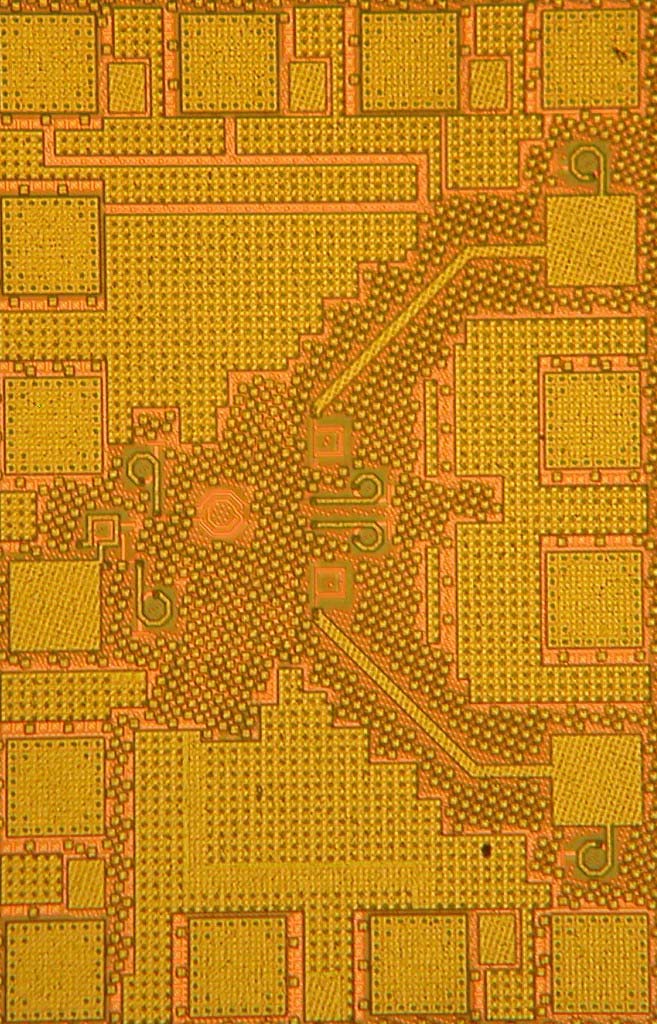

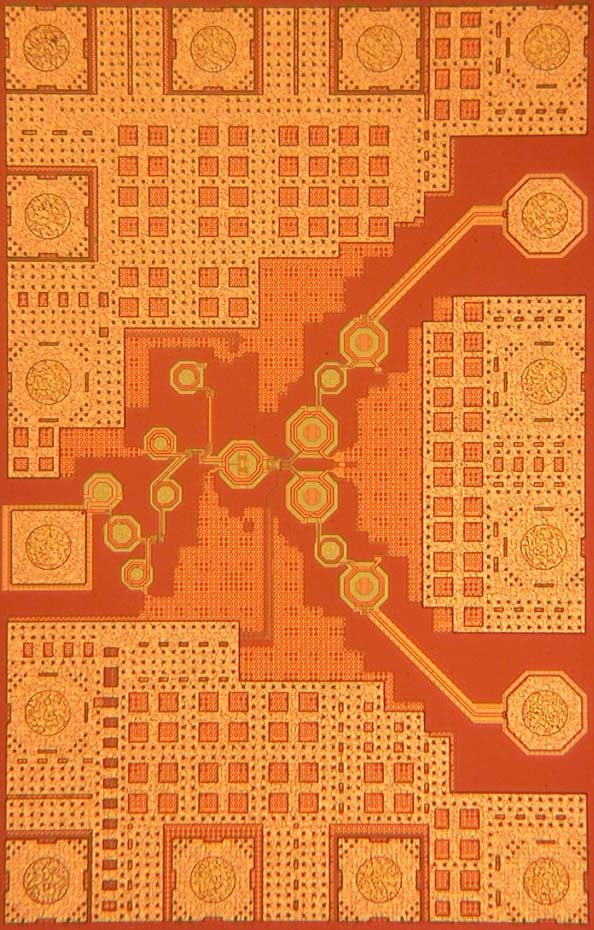

SiGe和SOI标签的芯片显微照片如图16所示。这些芯片具有相同尺寸和焊盘框,占据0.57 × 0.88 mm²。输入焊盘位于底部,两个输出焊盘位于顶部。

采用55纳米SiGe BiCMOS工艺,(b) 采用45纳米SOI CMOS工艺。两款芯片的尺寸均为0.57 × 0.88 mm²。)

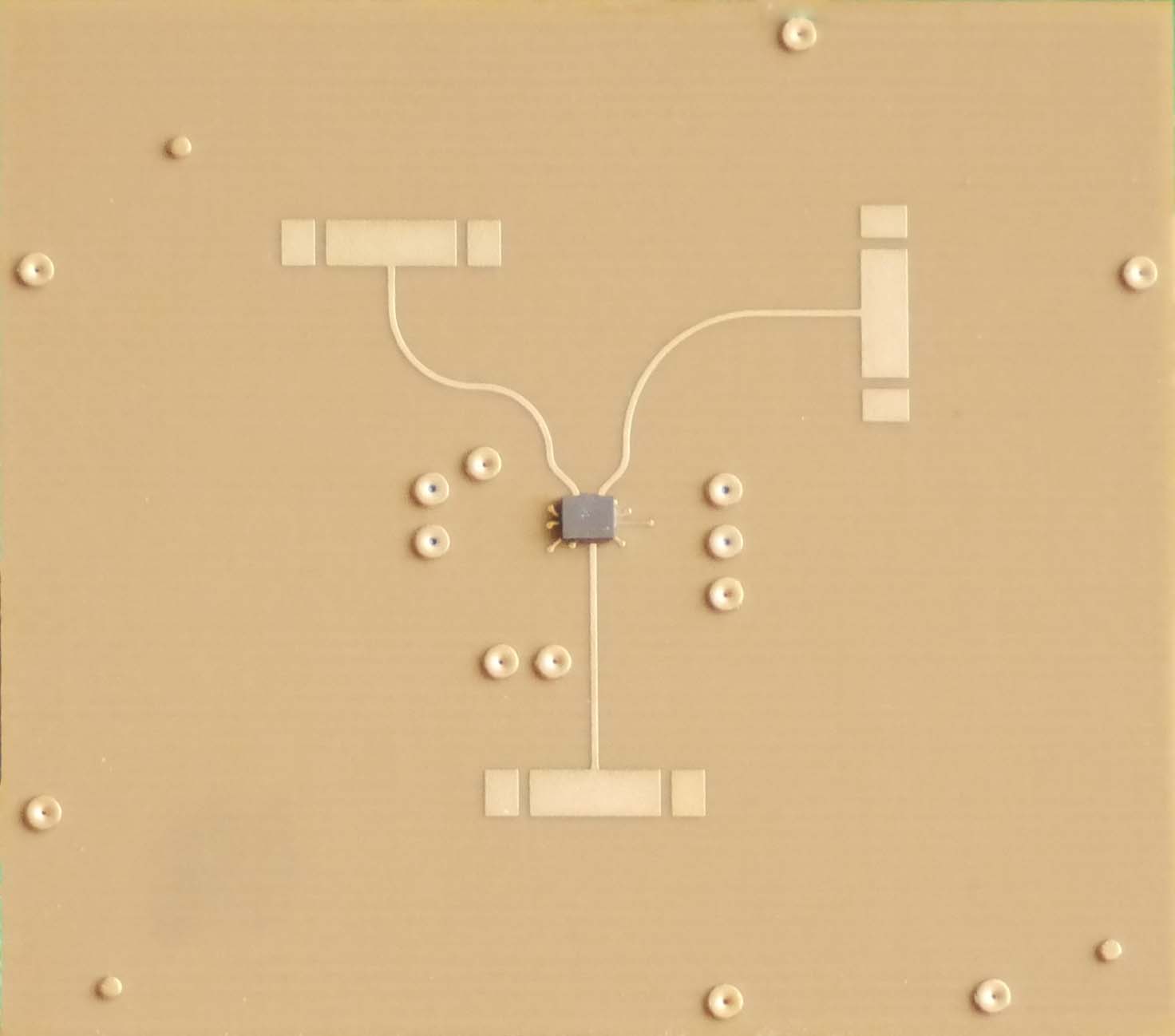

芯片采用倒装芯片安装在一块 23 × 20 mm²的微型PCB上,该PCB包含接收和两个发射天线。

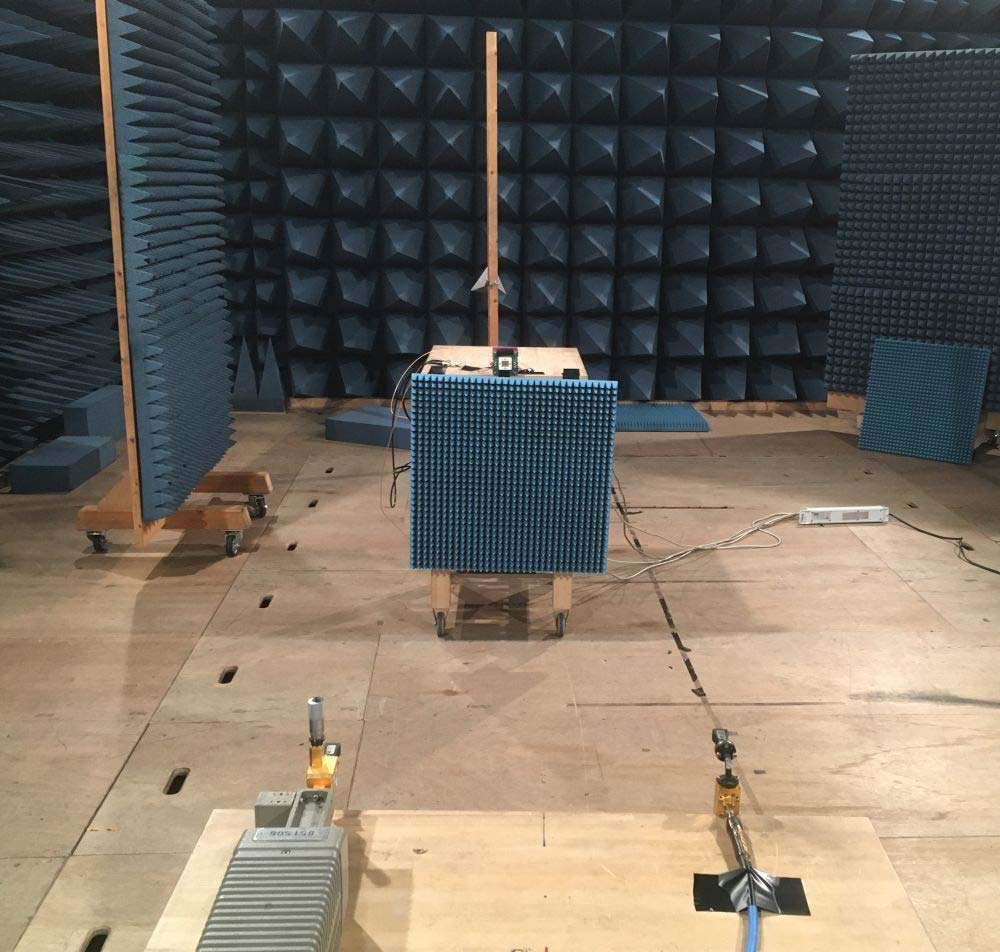

如图17所示。为了提高增益和隔离度,天线之间的间距更大,且方向不同于[5]和[6]中 7 × 7 mm²柔性中介层上的设计。

六、实验结果

首先在晶圆上对SiGe BiCMOS和SOI标签进行了探针测试。仅在SiGe标签中验证了唤醒检测器的功能。SOI检测器的输出即使在没有输入信号的情况下也被激活。怀疑是检测器中MOSFET差分对的失调电压过大,触发了CMOS反相器。链路演示实验仅在封装后的硅锗双极互补金属氧化物半导体标签上进行。

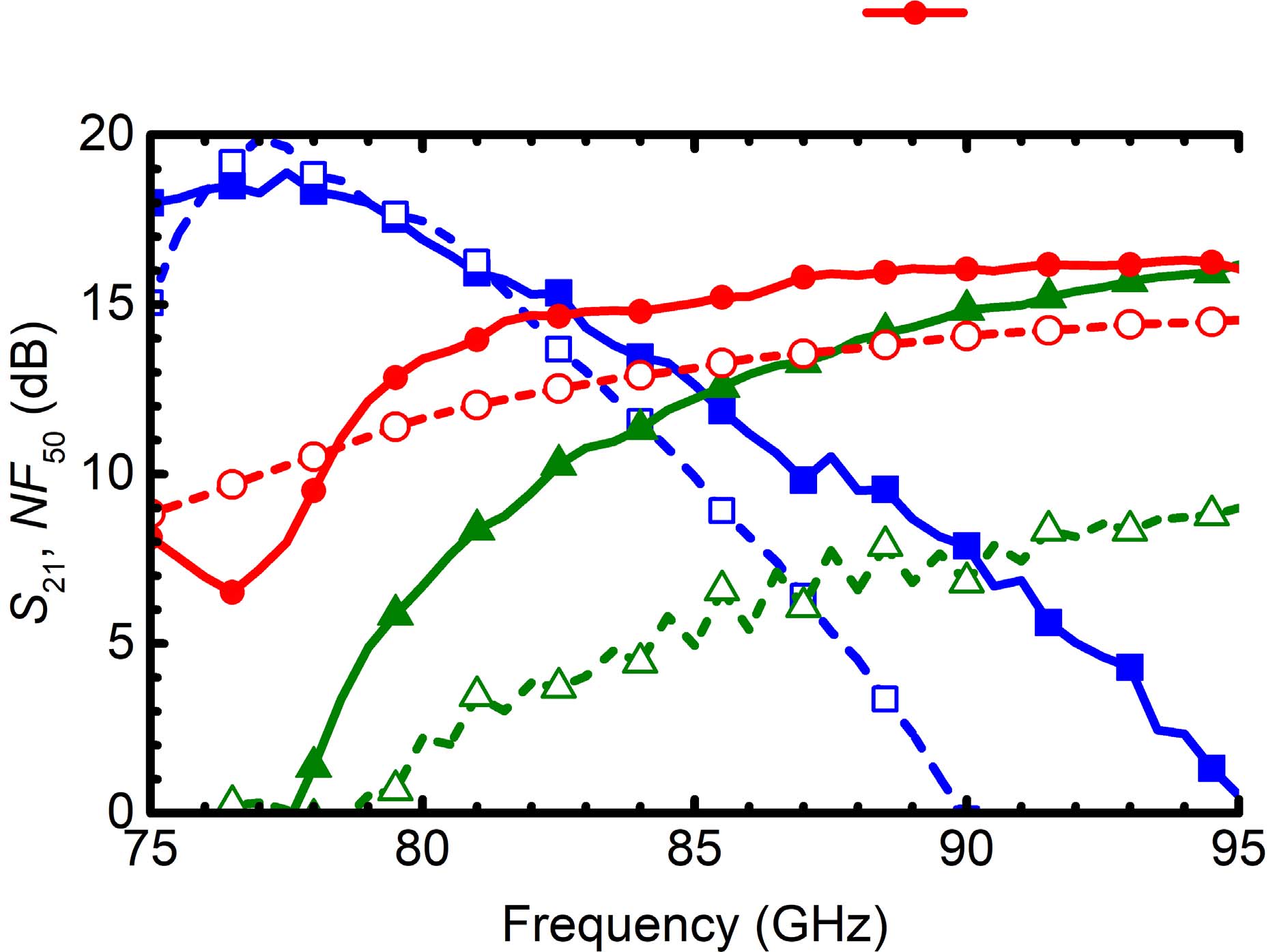

A. 芯片级测量

图18汇总了两个标签测得的S参数和50‐噪声系数,NF50。测量时使用安捷伦75‐88 GHz N8975A‐K88单边带下变频器和N8975A噪声系数分析仪,并结合带有内置隔离器的ELVA W波段噪声源来测量NF50。在这些测量中,SiGe标签从2.5 V电源消耗10 mA电流,而SOI标签则在1.2 V电源下偏置电流为15 mA。SiGe和SOI标签具有几乎相同的性能,在低噪声放大器输入与每个可变增益放大器

输出之间分别具有19 dB和20 dB的增益。输入反射系数S11,

在75至81 GHz和75至86 GHz范围内,SiGe和SOI标签的值分别保持低于 −15 dB。

尽管可用的矢量网络分析仪(VNA)未覆盖67–75 GHz范围,但在[5]和[6]中报告的67 GHz以下的测量结果表明,SiGe标签的3‐dB带宽为9 GHz,SOI标签的 3‐dB带宽为5 GHz。测得的50‐噪声系数分别小于9和 8 dB。图19给出了SiGe BiCMOS和SOI CMOS标签的实测与仿真噪声系数的比较,显示测量结果与仿真结果具有良好的一致性。然而,SOI标签的仿真噪声系数最小值出现的频率略高于实测噪声系数的最小值频率。

还加工并测试了一个硅锗低噪声放大器的 breakout 版本。在 2.5 V 电源电压下,其表现出优异的S11和S22特性,峰值增益达到 30 dB,功耗为 11.25 mW。当电源电压降至 1.8 V 时,低噪声放大器的增益下降至 26 dB,功耗降低至 8.1 mW [5]。

为了说明增益、噪声系数和功耗之间的权衡,图20和 图21分别显示了SiGe和SOI标签在79 GHz和78 GHz时输入共源共栅电流密度变化下的实测增益和NF50。SiGe和 SOI标签的最佳噪声系数对应的电流密度分别为1.15和 0.3 mA/μm。图20和图21还表明,功耗可以

如果将标签增益降低至15分贝,则噪声系数的劣化极小,同时可使功耗几乎减半。

增益控制在图22和图23中进行了演示。两款芯片均支持超过20 dB的增益控制,尽管实际平衡输出仅需其中一小部分范围。

当77.4吉赫的输入信号被500千赫正弦波进行BPSK调制时, SOI标签芯片的实测输出频谱如图24所示。载波抑制超过35分贝

可以观察到,表明寄生幅度调制可忽略不计。

图25显示了SiGe标签在Pin= −61.2 dBm时的检测器输出,与图25中的仿真结果非常吻合。

B. 封装内测量

图26中的测量装置用于验证封装式SiGe标签的功能和链路距离。该装置包括一个W波段倍频信号源,其输出功率为0分贝毫输出功率,以及一个20分贝各向同性增益喇叭天线作为FMCW

基站发射机,以及第二个20分贝各向同性增益喇叭天线连接到一个W波段谐波下变频混频器作为基站接收机。封装式SiGe标签放置在距离FMCW源5米的位置。

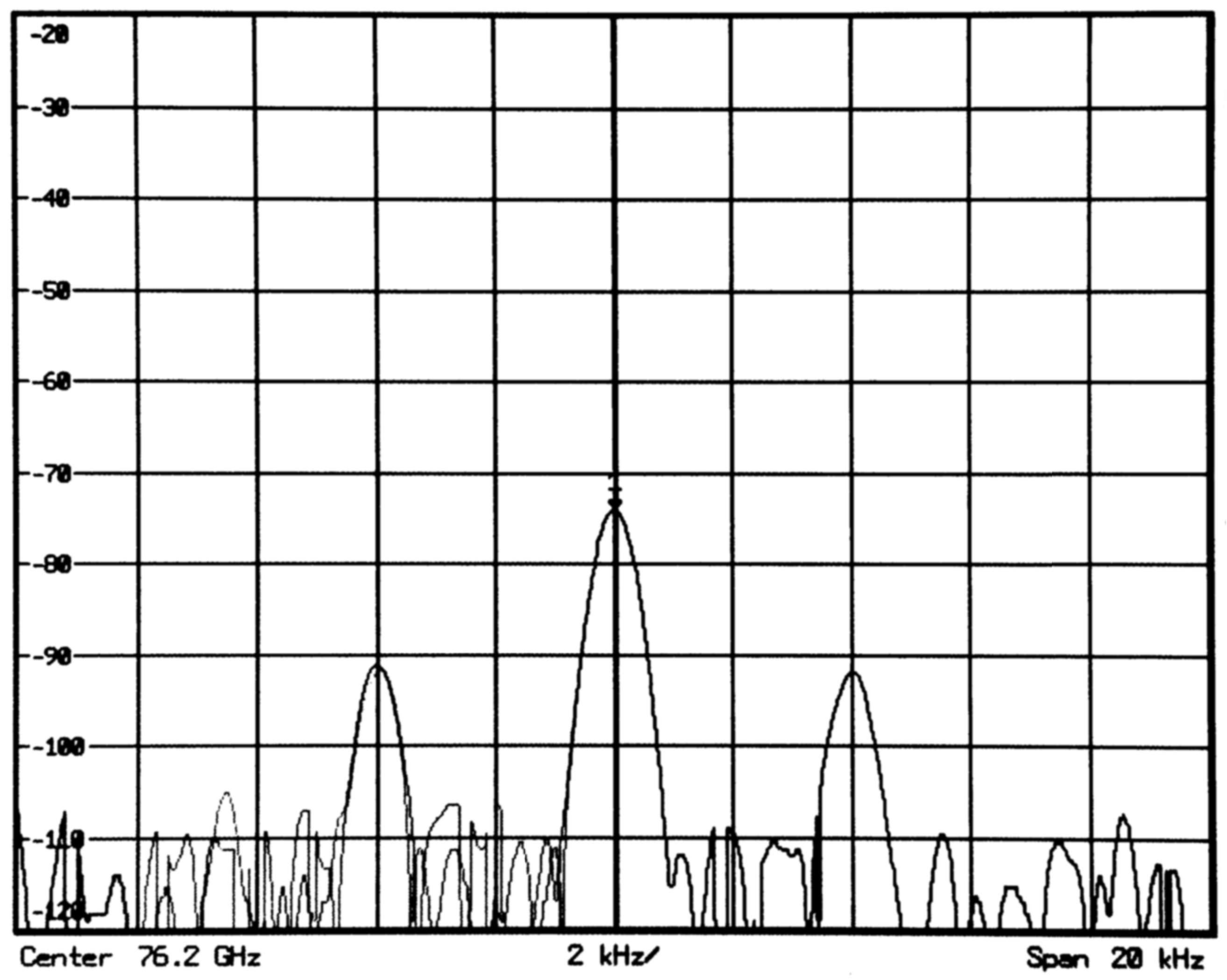

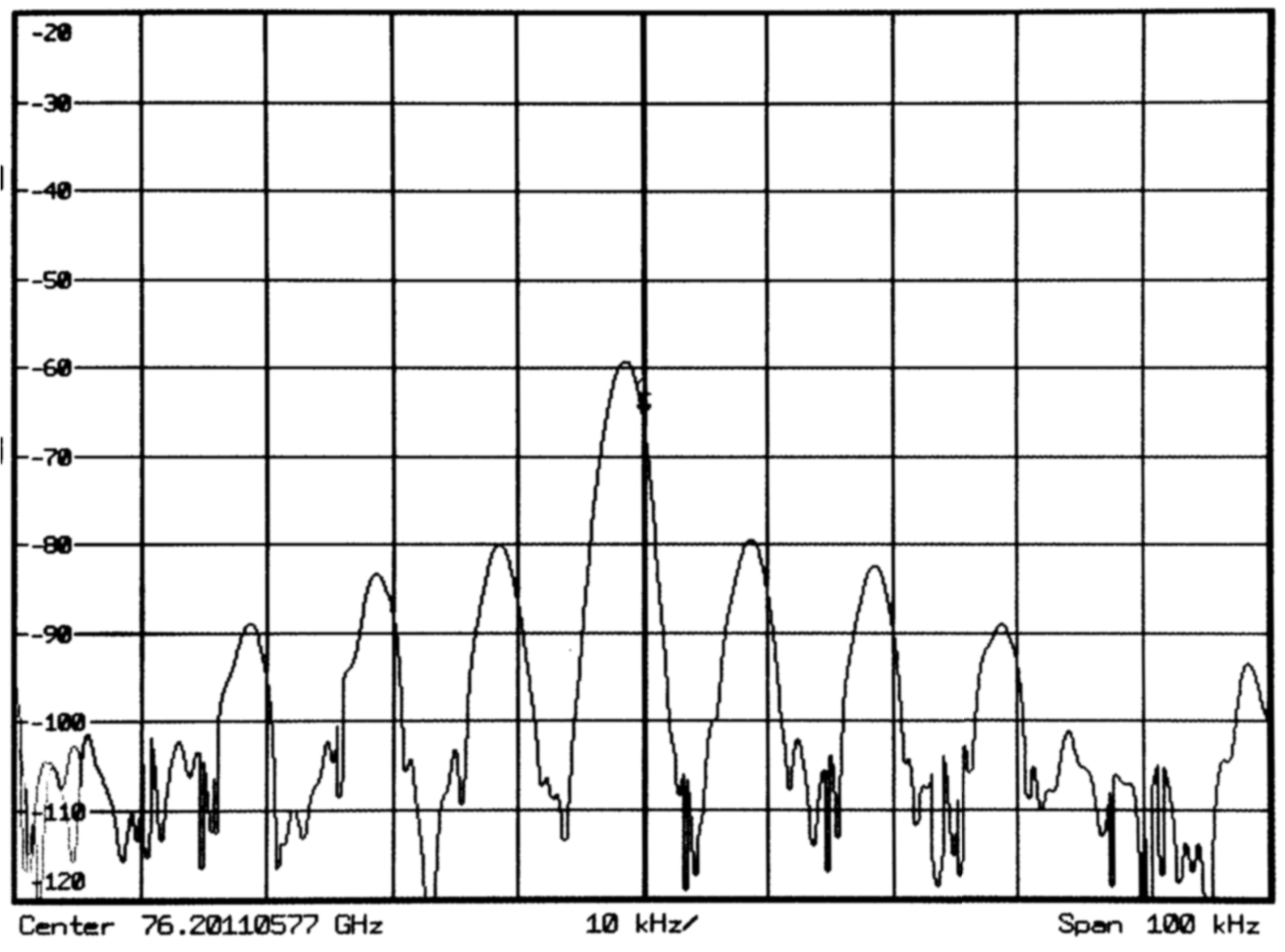

传播实验采用4千赫的BPSK调制和10千赫的AM调制。在这两种情况下,载波频率均为76.2吉赫。AM调制施加于可变增益垫片上。通过连接到基站接收机的频谱分析仪捕获的相应频谱分别如图27和图28所示。两种情况下的信噪比均优于18分贝,与第二节中的系统链路仿真结果一致。

最后,图29展示了SiGe标签对76.2吉赫载波使用4千赫正弦波进行BPSK调制后,基站接收到的边带功率随标签与基站之间距离的变化关系。文中给出了同极化和交叉极化天线测量结果,并与理论进行了比较。再次验证了实测结果与基于弗里斯传输方程的理论功率计算值高度吻合。

表II总结了两个标签的性能,并将其与现有技术水平进行了比较。该55纳米SiGe BiCMOS

标签具有最高功能,其增益、噪声系数和功耗与在相同频率范围内工作的45纳米SOI CMOS标签相似。它包含一个唤醒其功能灵敏度为 −62 dBm。在空闲模式下,仅低噪声放大器(LNA)和检测器处于开启状态,从1.8 V电源消耗10.8毫瓦功率。当输入信号超过 −62 dBm时,唤醒检测器的输出改变逻辑状态,并激活标签中的所有模块。在激活模式下, SiGe标签从2.5 V电源消耗25毫瓦功率,具有19 dB增益、9 dB噪声系数以及以77 GHz为中心的9 GHz带宽。

表II 与现有技术的比较

| 文献 | 工艺 | 频率 (GHz) | 功能 | 增益 (dB) | NF (dB) | 功耗 (mW) | 唤醒功能 |

|---|---|---|---|---|---|---|---|

| [3] | SiGe | 77 | 有源反向散射 | 15 | 10 | 122 | 否 |

| [4] | CMOS | 60 | 半无源 | 10 | 15 | 3.5 | 否 |

| 本文 (SiGe) | 55 nm SiGe BiCMOS | 77–81 | 有源标签 | 19 | 9 | 25/10.8 (工作/空闲) | 是 |

| 本文 (SOI) | 45 nm SOI CMOS | 77–81 | 有源标签 | 20 | 8 | 18 (常开) | 否 |

七、结论

首次在W波段研究并演示了采用55纳米SiGe BiCMOS和45纳米SOI CMOS商用技术实现的具有一个接收通道和两个发射通道的有源毫米波反射器。对SiGe HBT与SOI CMOS共源共栅拓扑结构进行了对比研究,并分析了无源匹配网络的品质因数对放大器增益和功耗的影响,以确定两种技术中最佳的系统架构和电路拓扑结构。

仿真和片上测量结果证实,SiGe和SOI标签可实现相似性能。SiGe和SOI标签的测量结果显示增益分别为19 dB和 20 dB,带宽分别为9 GHz和5 GHz,噪声系数分别为9 dB和8 dB,每个发射通道均具备20 dB的独立增益控制能力。SiGe标签内置的唤醒检测器输入灵敏度水平为 −62 dBm,可用于将标签置于激活模式或空闲模式,在 FMCW雷达基站无询问信号时进一步节省功耗。

1254

1254

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?