一.算法原理

计算公式:H(2,2)= f(2,2) - 1/9*滑框均值 + 100

假设一幅图大小为302 * 302 * 8 bit 那么 在3*3的模板 滤波次数 就为 (302-3+1)*(302-3+1)= 300*300

二.在FPGA中的原理

1.原理介绍

图像输入以CameraLink协议为例,向FPGA输入300*300的图像,由于需要将图像的首行首列尾行尾列进行滤波,所以需要将图像没采集之前,将补0fifo写入302个0也就是第一行的数据。随后采集到图像的第一行,在第一个像素加一个0,第一行的末尾也添加一个0,直到最后一行采集结束,再补302个0.这样确保补0fifo中图像大小永远是302*302大小。

随后,当补0FIFO够302个点开始读出数据,同时写入FIFO_LINE2。当FIFO_LINE2够302个点且补0FIFO够302个点的时候,开始读出FIFO2的数据同时写入FIFO_LINE1。当三个FIFO都够302个点时,开始同时读出数据,进入L1第一级缓存区,以此类推至L3级。再依次进行计算输出。

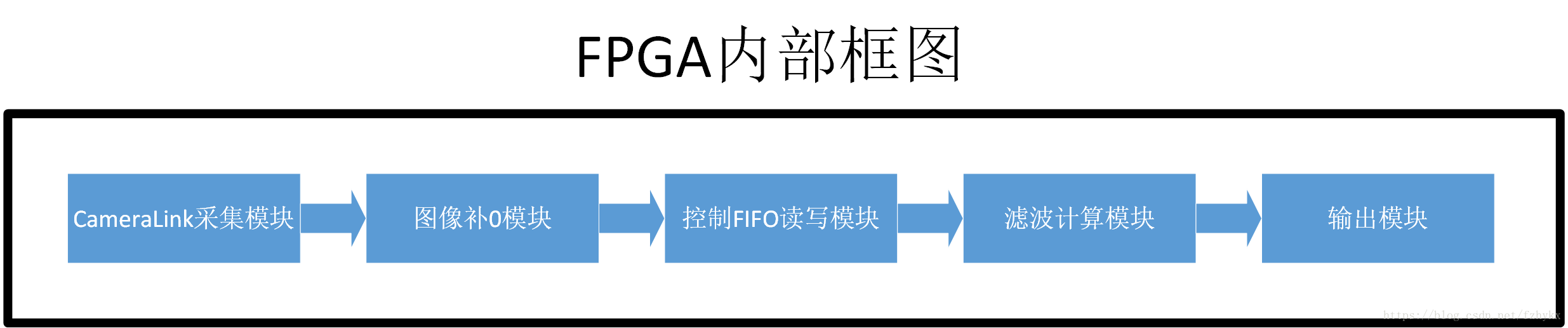

2.内部框架介绍

本文详细介绍了基于FPGA的高通滤波算法实现,包括算法原理、FPGA内部工作流程以及具体设计中遇到的问题。通过CameraLink协议输入图像,利用3*3模板进行滤波,通过多个FIFO的读写操作实现图像处理,并在FPGA内部进行了多层次的缓存设计。在实际操作中,针对FIFO读写时序控制等细节问题进行了调整和优化。

本文详细介绍了基于FPGA的高通滤波算法实现,包括算法原理、FPGA内部工作流程以及具体设计中遇到的问题。通过CameraLink协议输入图像,利用3*3模板进行滤波,通过多个FIFO的读写操作实现图像处理,并在FPGA内部进行了多层次的缓存设计。在实际操作中,针对FIFO读写时序控制等细节问题进行了调整和优化。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1302

1302

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?