一、中断简介

什么是中断?程序运行过程中,系统外部、系统内部或者现行程序本身若出现更高优先级事件,处理机立即中止现行程序的运行,自动转入相应的处理程序(中断服务程序),待处理完后,再返回原来的程序运行,这整个过程称为程序中断。中断提升了系统的实时性,提升了系统的工作协调能力及工作效率。

广义的中断概念包括以下几个关键要素:

- 中断请求(Interrupt Request,IRQ): 外部设备或系统内部产生中断时,会向计算机发送中断请求。每个中断源通常有一个唯一的IRQ号。

- 中断向量表(Interrupt Vector Table,IVT): 计算机维护一个中断向量表,其中存储了每个可能中断的处理程序的地址。当中断发生时,计算机通过查找中断向量表找到相应中断的处理程序。

- 中断服务程序(Interrupt Service Routine,ISR): 中断服务程序是一段特定的代码,用于处理特定中断类型。当中断发生时,控制权会转移到相应中断的ISR,执行相关操作。

- 中断控制器(InterruptController): 中断控制器负责管理和协调各个中断源,确保按照优先级处理中断。常见的中断控制器包括 PIC(Programmable Interrupt Controller)和 APIC(Advanced Programmable Interrupt Controller)。

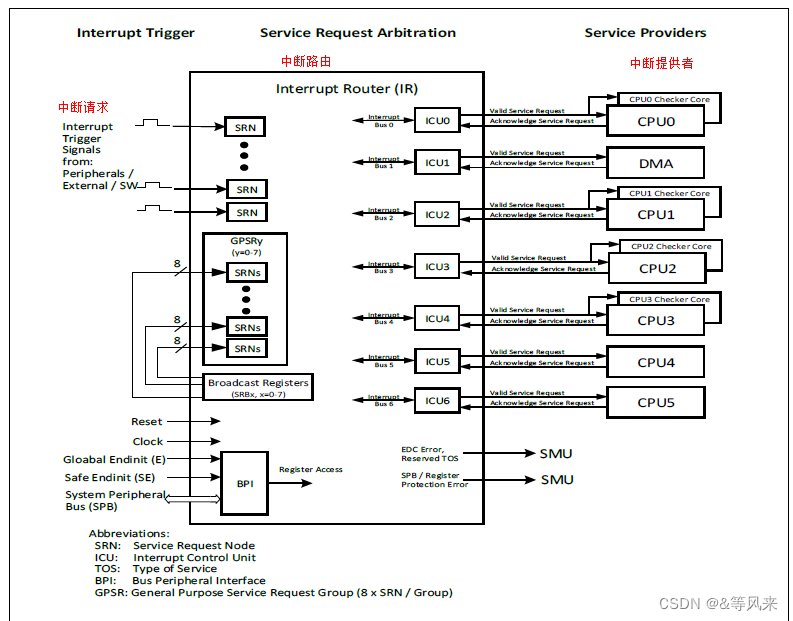

TC3XX系列MCU中断采用中断路由的方式,将硬件中断源和CPU、DMA进行灵活的连接,具有较高的中断实时性。

二、功能介绍

中断系统

TC3XX的中断系统涉及到中断控制器,CPU,DMA,外设。

中断系统框图如上图所示:主要包含以下三部分:

- 中断请求:可以外设/外部信号/软件来触发;

- 中断路由:根据配置的中断优先级进行中断仲裁,主要包含服务请求节点SRN,中断控制单元ICU,外设总线接口BPI。

- 中断提供者:中断的服务对象,可以是CPU(中断服务),也可以是DMA(使能通道转换),当服务对象是DMA时,就可以解放CPU的算力,例如ADC/SPI中断触发DMA搬运。

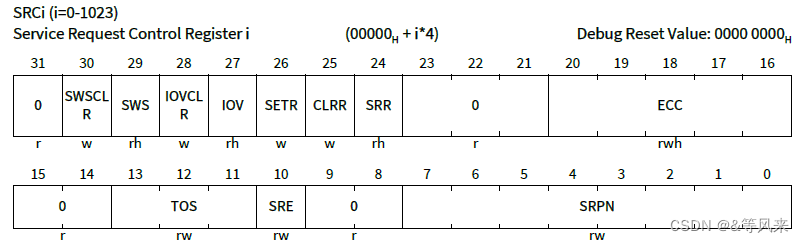

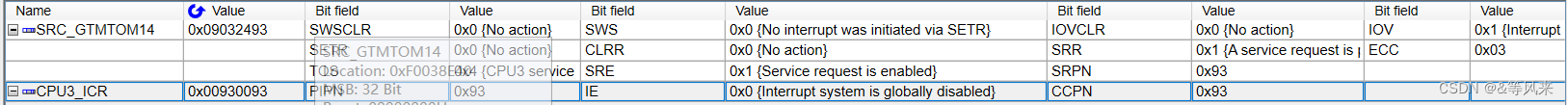

服务请求控制寄存器SRC

每个服务请求节点SRN对应一个中断请求。每个SRN都有一个服务请求控制寄存器SRC,可以说是IR中最重要的寄存器,调试时也时常为我们提供帮助。

- SRPN(Service Request Priority Number):服务请求优先级,它决定了服务请求在IR中仲裁的结果;当服务提供者是DMA时,它表示的是DMA通道号;

- SRE(Enable Bit):中断使能位,决定IR是否将该请求路由到对应的服务提供者,如果使能位没有打开,也可以通过软件轮询SRR中断状态位来执行对应服务例程;

- TOS(Type-Of-Service Control):服务类型控制,也就是选择将服务路由到哪个ICU中,是CPU还是DMA;

- SRR(Service Request Flag):中断标志位,该位在服务提供者响应服务的时候会自动清除,所以不需要软件去清除中断标志位,但如果没有打开SRE使用的轮询,则需要每次执行后用CLRR清除中断标志位;

- CLRR(Clear Bits):中断标志清除位,用来清除SRR,读的话一直是0;

- SETR(Set Bits):软件中断请求位,通过软件请求一次中断;

- IOV(Interrupt Trigger Overflow Bit):中断溢出标志位,如果一个中断没有被接收或者清除,又进行了一次触发,则该位会置位;

- IOVCLR(Interrupt Trigger Overflow Clear Bit):中断溢出标志清除位,清除中断溢出标志,读的话一直是0

- SWS(SW Sticky Bit):软请求粘滞位,如果调用过SETR接口进行过软触发,则该位会置位直到清除;

- SWSCLR(SW Sticky Clear Bit):软请求粘滞清除位,用来清除软请求粘滞位,读的话一直是0;

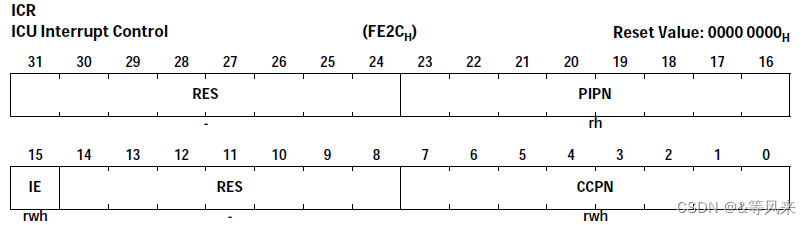

中断控制寄存器ICU

每个SRN的服务请求会路由到一个ICU中,一个ICU连接一个CPU或者DMA,共7个ICU。每个ICU内部进行服务请求的仲裁,并将仲裁的结果发送到相应的服务提供者。

ICU中断控制寄存器ICR

ICR是CPU主要的中断控制寄存器,包括全局中断使能位IE,当前CPU中断优先级CCPN,以及等待中断优先级位PIPN,RES为保留位。

- IE(Global Interrupt Enable Bit):全局中断使能位,我们所使用的关闭所有中断操作,就是将该位置0,因为每个CPU是独立的,也有自己的ICR控制器,所以IE只控制当前核的中断开关;

- CCPN(Current CPU Priority Number):当前CPU中断优先级,在非中断程序执行时,该位为0,进入中断时,该位会被硬件设置为所触发中断的优先级;

- PIPN(Pending Interrupt Priority Number):等待中断优先级,表征当前CPU收到IR路由但还未处理的中断优先级;

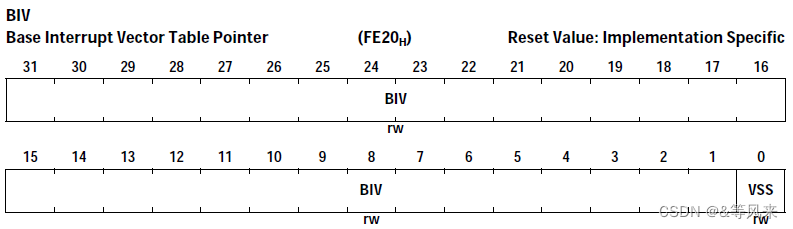

中断向量表

介绍中断向量表之前先介绍一下中断向量表指针BIV

- BIV(Base Address of Interrupt Vector Table):中断向量表基址,中断向量表是存放在Flash中的连续地址,该寄存器来表示向量表基地址;

- VSS(Vector Spacing Select):向量空间选择位,该位表征每个中断向量所占的内存空间,0表示每个中断向量占据32字节,1表示8字节,默认为32字节;

TC3XX的中断向量表存放在PFlash(代码段)中的一段连续地址中,默认一个向量的存储空间是8 word(32字节)(Tricore 1.6可以选择32还是8 Byte, Tricore 1.3只能32 Byte),BIV指向基地址。VSS为0时,中断的向量地址为:BIV+N*32。(N表示中断优先级)。一般情况下,32字节向量空间用来放置跳转指令。另一种方式是代码量不大,通过占据连续的优先级方式,节省一次跳转,如下图,优先级2中断触发,3-5的位置也被占用了。

三、实战演练

MCAL配置

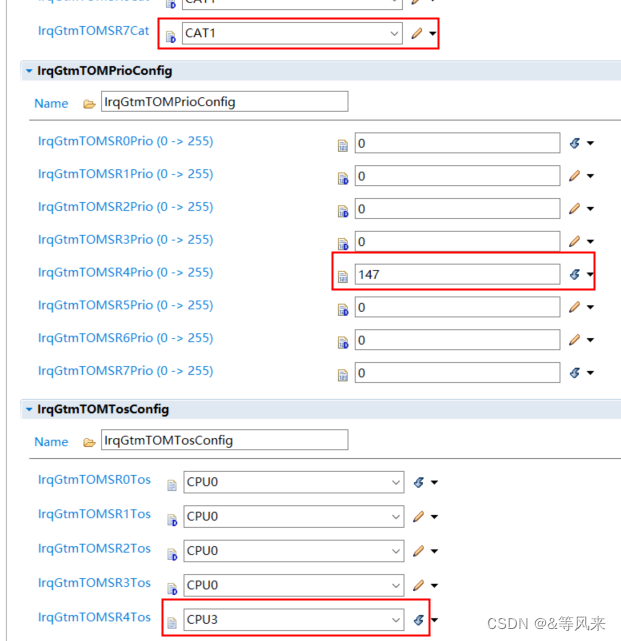

如上图所示,配置为一类中断,中断源为TOM1_8或者TOM1_9(SR0对应通道0和通道1,以此类推),服务提供者为CPU3。

代码编写

首先进行初始化和中断使能,初始化一般放在EcuM_AL_DriverInitOne里,中断使能可以放在相应的模块(如果在OS里配置了,那么OS初始化中断向量表时会使能中断)。伪代码如下:

IrqGtm_Init();

SRC_GTMTOM14.B.SRE = 1;

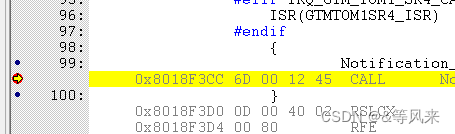

再对中断函数进行编址,并调用中断服务函数,以Tasking为例

#define IFX_INTERRUPT(isr, vectabNum, prio) \

void __interrupt(prio) __vector_table(vectabNum) isr(void)

#if (IRQ_GTM_TOM1_EXIST == (STD_ON))

#if IRQ_GTM_TOM1_SR4_TOS != IRQ_TOS_DMA

#if((IRQ_GTM_TOM1_SR4_PRIO > 0) || (IRQ_GTM_TOM1_SR4_CAT == IRQ_CAT2))

#if((IRQ_GTM_TOM1_SR4_PRIO > 0) && (IRQ_GTM_TOM1_SR4_CAT == IRQ_CAT1))

#if(IRQ_GTM_TOM1_SR4_TOS==IRQ_TOS_CPU0)

IFX_INTERRUPT(GTMTOM1SR4_ISR, 0, IRQ_GTM_TOM1_SR4_PRIO)

#elif(IRQ_GTM_TOM1_SR4_TOS==IRQ_TOS_CPU1)

IFX_INTERRUPT(GTMTOM1SR4_ISR, 1, IRQ_GTM_TOM1_SR4_PRIO)

#elif(IRQ_GTM_TOM1_SR4_TOS==IRQ_TOS_CPU2)

IFX_INTERRUPT(GTMTOM1SR4_ISR, 2, IRQ_GTM_TOM1_SR4_PRIO)

#elif(IRQ_GTM_TOM1_SR4_TOS==IRQ_TOS_CPU3)

IFX_INTERRUPT(GTMTOM1SR4_ISR, 3, IRQ_GTM_TOM1_SR4_PRIO)

#endif

#elif IRQ_GTM_TOM1_SR4_CAT == IRQ_CAT2

ISR(GTMTOM1SR4_ISR)

#endif

{

ENABLE();

Notification_TOM1_SR4();

}

#endif

#endif

#endif

调试器调试

TC3XXMCU的中断系统详解:原理、功能配置与实战应用

TC3XXMCU的中断系统详解:原理、功能配置与实战应用

4738

4738

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?