1、模块介绍

CAN 总线是一种广泛应用于汽车、工业控制和其他领域的串行通信协议,CAN 英文名称:Controller Area Network。最初由德国的 Bosch 公司开发,用于汽车电子系统之间的通信。CAN 总线具有高可靠性、抗干扰能力强和实时性好等特点,因此被广泛应用于需要可靠数据传输的领域。

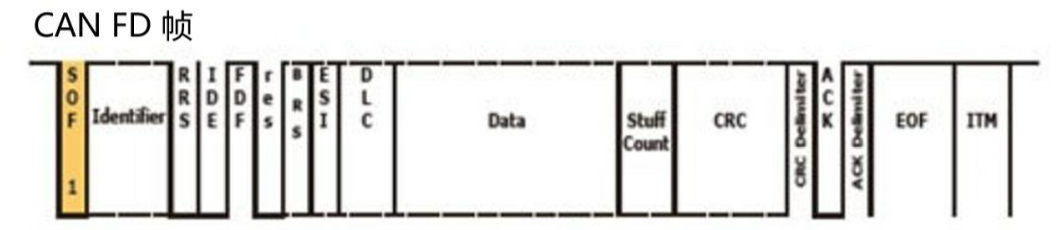

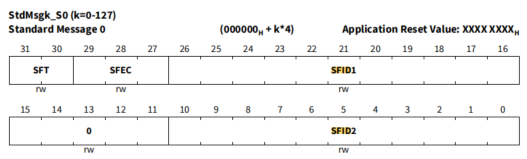

CAN2.0B 协议中的 CAN 最多支持 29 位 ID,但是网络架构中使用的一般是 11 位的标准帧 ID。如下图是标准 CAN FD 帧数据结构:

关于 CAN 协议相关内容,本文不作阐述。

Aurix2G TC3XX 系列的 CAN 模块称为 MCMCAN,集成的是 Bosch 的 M_CAN 内核,最多集成了三个 CAN Module,每个 CAN Module 包含 4 个 CAN 节点(M_CAN)。支持 ISO11898-1&-4 协议,支持 SAE1939 协议,支持最高单帧 64 字节的 CANFD 传输,支持 5Mbit/s 的波特率,且在时钟高达 80MHz 的情况下可扩展至 8Mbit/s。

2、功能介绍

2.1、CAN 硬件框架

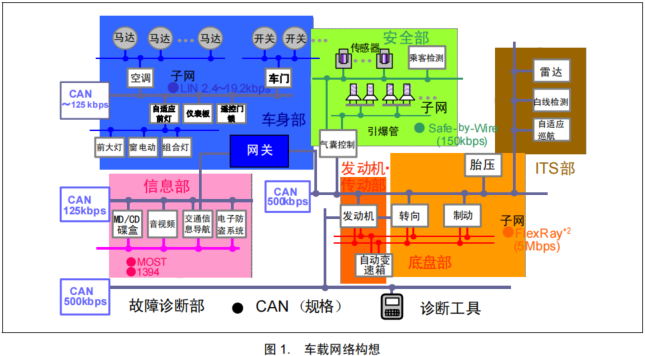

如下图 1 为 CAN 车载网络构想图:

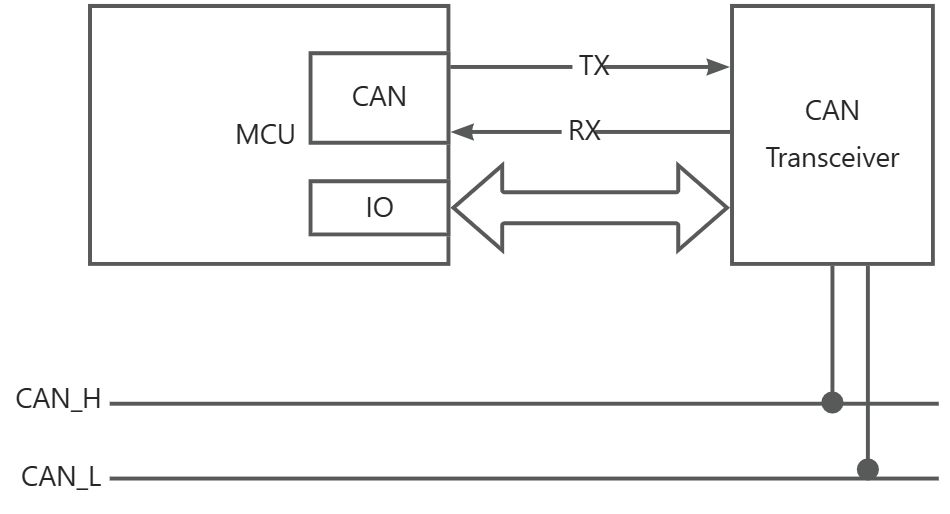

如下图 2 为控制器端的结构示意图:

在 CAN 控制器节点中,一般 MCU 中集成了 CAN 控制器,同时节点配备板载 CAN 信号收发器即 Can Transceiver,CAN 控制器和 CAN Transceiver 之间通过 TX 和 RX 进行数据交互。MCU 通过 IO 控制 Transeiver 的状态,以及状态回读。

Transceiver 则通过 CAN_H 和 CAN_L 连接到整车的 CAN 网络上,通过差分信号进行数据交互。

另外对于具备休眠唤醒的 Transceiver,存在一些电源控制连接。

2.2、CAN 时钟配置

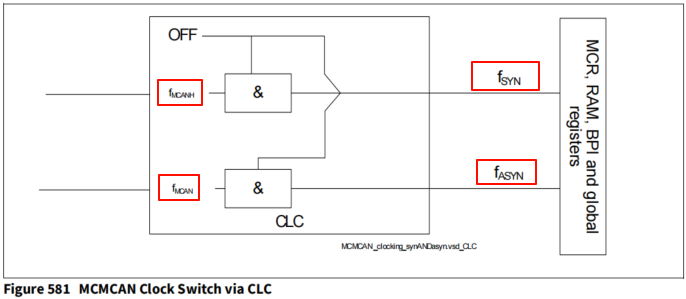

TC3xx CAN 模块有两路主时钟源,来自系统的 CCU 模块。如下图 581 所示:

fSYN 由 CCU 的 fMCANH 和 fASYN 提供。fSYN 用作寄存器和 CAN RAM 访问速度,通过 CCUCON5.MCANHDIV 来进行配置;

fASYN 由 CCU 的 fMCAN提供。fASYN 主要用作配置标准与快速 CANFD 波特率配置。通过 CCUCON1.MCANDIV 来配置;

如上图 CAN 模块时钟fASYN 可通过时钟控制寄存器 CLC 关闭。fASYN 推荐 80,40,20MHz,必须满足 fSYN>fASYN。

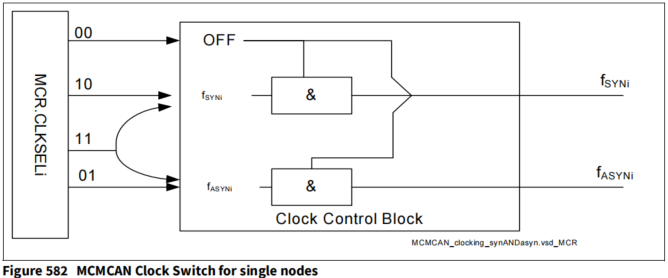

CAN 模块内部每个Node的时钟都可以通过 MCR.CLKSELi进行独立控制,此处不分频。如下图:

2.3、CAN 波特率及采样点

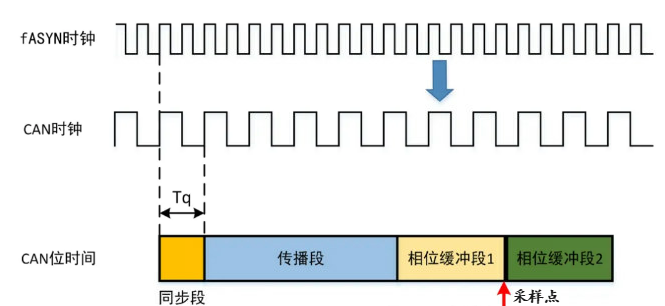

波特率及采样点的设置涉及到同步段 Sync_Seg、传播段 Prop_Seg、相位缓冲段 Phase_Seg 等。

fASYN 时钟到达 CAN 模块之后,通过设置 DBTP.DBPR 进行分频,得到 CAN 时钟。一般不分频即 DBTP.DBPR=0。

波特率计算公式为:BaudRate = fASYN/((CBRP+1)*( Sync_Seg+Prop_Seg+Phase_Seg1+Phase_Seg2))

采样点计算公式:SamplePoint = (Sync_Seg+Prop_Seg+Phase_Seg1)/(Sync_Seg+Prop_Seg+Phase_Seg1+Phase_Seg2)*100%

M_CAN 中,DBTP.STSEG1 = Prop_Seg + Phase_Seg1 -1,DBTP.DTSEG2 = Phase_Seg2 - 1。DBTP.DSJW 等于同步跳转宽度减 1。同步段为固定值 1。

2.4、MCMCAN 概括

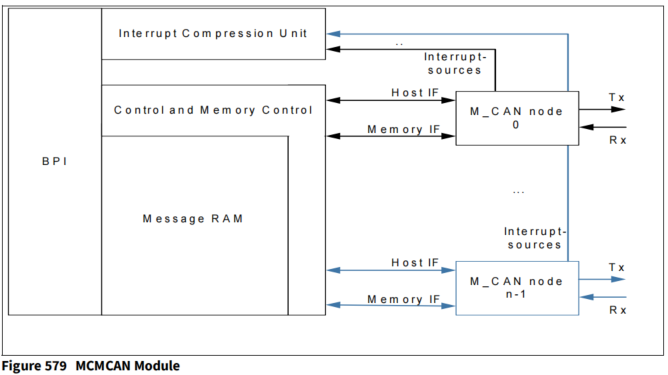

TC3XX 中一个 CAN Module 包含 4 个 M_CAN Node,其芯片内部框图如下图所示:

由上图可知每个 CAN Module 有一块共有的 RAM,为 Message RAM。因为 CAN 模块需要一块额外的 RAM 用于数据的收发和控制等,这个是由芯片厂商来实现的,例如 TC3XX 系列中,Message RAM 就集成在 CAN 模块外设地址起始位置。每个 CAN Node 有 Host IF 和 Memory IF 与主机(CPU)相连,同时通过 TX/RX 与外部进行信号交互。(其中 TC38xx 系列 CAN0 外设最大 32kByte,CAN1 与 CAN2 外设为 16 kByte。)

我们把 CAN Node 展开,该部分为 Bosch IP 内核,每个 M_CAN Node 的框架如下图所示:

由上图可知,CAN 模块作为从机通过 Host IF 接口接入到芯片内部的 Host(TC3XX 中即 CPU),Hos 通过控制 CAN 模块的寄存器来进行控制交互。CAN 模块还作为主机通过 Memory IF 接口接入到 Message RAM,用于存取传输数据。

CAN Core

CAN 协议内核控制器,接收,发送移位寄存器,支持 ISO 11898-1:2015 协议功能,支持 11 位和 29 位 CAN ID。

Sync

用于在 CAN Core 和 Host 之间进行时钟同步。

Clk

时钟管理模块。

Cfg&Ctrl

CAN Core 及相关模块的控制和配置位。

Interrupt & Timestamp

中断控制和 16 位 CAN 位时间计数器用于接收和发送时间戳的生成。

Tx Handler

控制从 Message RAM 到 CAN Core 的消息传输。最多可配置 32 个 Tx Buffers 用于传输。Tx 缓冲区可以用作专用 Tx Buffer、Tx FIFO,Tx Queue 的一部分,或作为它们的组合。一个 Tx 事件 FIFO 存储 Tx 时间戳和相应的消息 ID。M_CAN 还支持发送取消。

Rx Handler

控制从 CAN Core 到 Message RAM 的接收消息的传输。Rx 处理程序支持两个 Rx FIFO,每个都是可配置的大小,以及多达 64 个

专用的 Rx Buffer,用于存储已通过接收过滤的所有消息。一个专用的 Rx Buffer,用于仅存储具有特定标识符的消息。Rx 时间戳与每条消息一起存储。最多可为 11 位 ID 定义 128 个过滤器,最多可为 29 位 ID 定义 64 个过滤器。

Generic Slave Interface

将 M_CAN 连接到客户指定的主机 CPU。通用从属接口能够连接到 8/16/32 位总线,以支持广泛的互连结构。

Generic Master Interface

将 M_CAN 访问连接到外部 32 位 Message RAM。单个 M_CAN 最多可使用 4.25K*32bit。

Extension Interface

中断寄存器 IR 的所有标志以及选定的内部状态和控制信号都路由到这个接口。该接口用于 M_CAN 与模块外部中断单元或其他模块外部组件的连接。这些信号的连接是可选的。

2.5、Message RAM

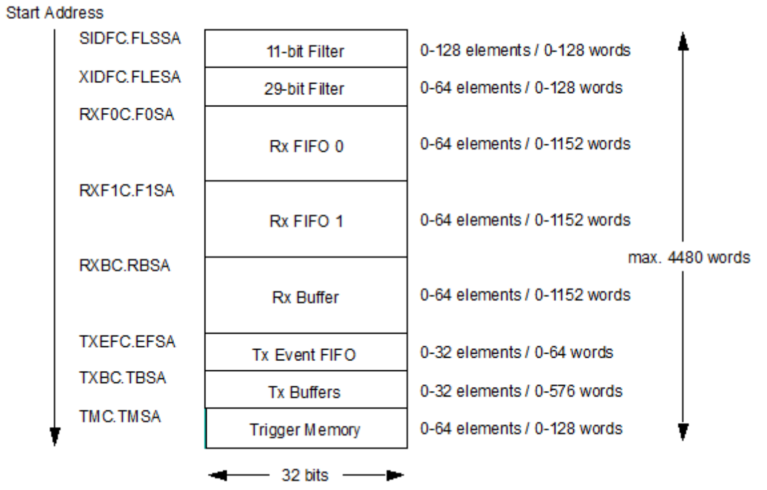

Message RAM,也就是 CAN RAM。首先介绍下 CAN RAM 在内存中的结构(TC3XX 系列中一个 CAN Module 的

4 个 Node 共享一块 RAM)

CAN RAM 是 32 位宽格式,用于存储 CAN 的接收过滤配置,收发数据。其在内存中的结构如下:

由上图可以看出,CAN RAM 被划分为多个块,每个块都有特定的寄存器指示其相对于 CAN RAM 的地址偏移。比如 Tx Buffers 块的绝对地址等于 CAN RAM StartAddr + TXBC.TBSA。需要注意的是,TC3XX 中每个 CAN Module 中的 4 个 CAN Node 是共用一块 CAN RAM 的,因此在资源分配时,若控制器需要的 CAN 节点数量没有超过 CAN Module 数量时,尽量使用不同 CAN Module 中的 Node。

2.5.1、Standard Message ID Filter Element

CAN ID 有 11bit 的标准 ID,还有 29bit 的扩展型 ID,因此 CAN 模块的 ID 过滤器有两种。

标准过滤器(Filter Element)占一个 Word(4 字节),可以通过寄存器 SIDFC.FLSSA 获取过滤器区域在 CAN RAM 中的相对地址偏移,

通过 SIDFC.LSS 获取过滤器的数量。

标准过滤器的寄存器如下:

SFT:Standard Message ID Filter Element,标准过滤器过滤类型

00 = 范围过滤,SFID1 到 SFID2 之间

01 = 双 ID 过滤,SFID1 或 SFID2

10 = 经典过滤, SFID1 = filter,SFID2 = mask

11 = 过滤器关闭

SFEC:Standard Filter Element Configuration,标准过滤器配置,所有过滤器都会被用于接收帧处理,直到第一个过滤器与之匹配

或者达到过滤器末端。若 SFE = 111b,则 SFT 无需关注,该帧直接存储到 Rx Buffer 中。

SFID1:Standard Filter ID 1,标准过滤器 ID1,在 Rx Buffer、同步报文、Debug 报文下,ID 与之相等的帧就会过滤成功,被存 储到Rx Buffer 中。

SSYNC:Standard Sync Message,标准同步帧,用于标记是否使能时间戳;

SFID2:Standard Filter ID 2,标准过滤器 ID2,该 ID 在 SFEC 定义的特殊匹配模式下配合 SFID2 使用;其中 SFID[5:0] 指示该过滤

器引用的 Rx Buffer(SFEC 为 111b 时有效)

当使用 FULL CAN 类型接收帧时,配置 SFEC 为 111b,配置 SFID1 为目标帧的 ID,即可进行接收。

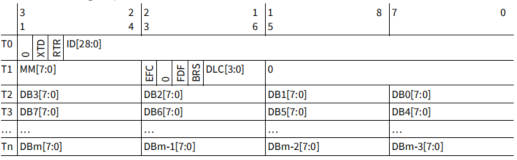

2.5.2、Tx Buffer Element

Tx Buffer 用于处理 CAN 数据的发送,CPU 通过将用户的待发送数据复制到 Tx Buffer 中,操作 CAN 发送寄存器,随后 CAN 模块

就从 CAN RAM 的 Tx Buffer 中读取数据进行发送。Tx Buffer 可用于特定帧 Buffer、Tx FIFO 以及 Tx Queue。

Tx Buffer 的数据位宽不是固定的,取决于数据宽度。通过** TXBC.TBSA **获取 Tx Buffer 在 CAN RAM 中的相对地址偏移,

通过 TXBC.NDTB 获取 Buffer 的数量。

每个 Tx Buffer 包括两个 Word 的头和若干数据组成,每个 CAN Node 的数据长度由 TXESC.TBDS 获取指定,结构如下:

通过 Tx buffer,完成了 CPU 与 M_CAN 之间的数据交互协议,CPU 填写 Tx Buffer 的头部信息,包括 CAN ID、DLC 等 ,以及数据

数据内容,然后操作寄存器进行,CAN 模块按照 Tx Buffer 中的信息和数据进行发送。

假设我们配置数据宽度为 64 字节,则第 n 个 TxBuffer 的内存中的绝对地址为 CanRamStartAddr + TXBC.TBSA+n*(8+64)。

2.6、Operation Modes 操作模式

2.6.1、初始化

软件需要设置** CCCR.INIT**,并设置 CCCR.CCE(M_CAN 配置寄存器仅当该位置位时才可访问),然后开始初始化,此时 CAN 模块

停止收发,错误计数保持不变。然后通过软件配置各项寄存器,以及 CAN RAM 初始化。完成寄存器配置后将 CCCR.INIT 位

清除,CCCR.CCE 会自动随之清除,已完成硬件配置。

2.6.2

2.6.2、普通模式

当完成寄存器和 CAN RAM 的配置后,CAN 模块会自动与外部收发器进行同步,进入普通工作模式。

对于接收帧的过滤器和 Rx Buffer、FIFO 等,是在初始化阶段设置的。CAN 模块在工作模式下若收到与之匹配的

CAN 报文,就会保存到 Rx Buffer 或者 FIFO 中。

而发送帧报文的 Tx Buffer 则是在发送时更新的。

2.6.3、CANFD 模式

CANFD(Controller Area Network Flexible Data Rate)模式中有两种变种,一种是常规的 CANFD 发送模式(BRS==1),

即报文中的控制段、数据段、CRC 段以较高的波特率进行传输,而帧开头和结尾以普通速度进行传输。另外一种

则是所有段都按照普通波特率进行传输

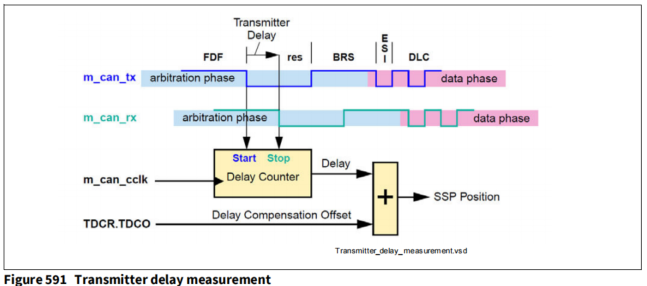

2.6.4、第二采样点 Transmitter Delay Compensation Measurement

CAN 总线节点在发送过程中,是要对输入信号进行回采的,以进行总线仲裁以及错误判断。如果一定时间内没有回采

到预期值,则会出现位错误。该时间阈值取决于 CAN 时钟频率。

当使用 CANFD 时且配置了较高频率的时钟,就会导致该延时阈值较短,也就是需要硬件在更短时间进行回读,但硬件

的延时相对较为固定,这个时候就容易误报位错误。也就是实际该帧发送正常,但是硬件回读时间大于阈值。

M_CAN 针对该特性提供了发送采样延时补偿,即第二采样点。通过硬件来放宽回读的间隔,且该特性使能后由硬件

自动标定,能够对不同时钟频率进行自适应。通过 寄存器 DBTPi(i=0-3)的 TDC 位控制是否使能。如下图:

2.6.5、受限操作模式 Restricted Operation Mode

当总线出现错误或负载过高时,例如发送错误计数 ECR.TEC 达到一定次数,表示无法往总线发送报文,CAN 控制器

会进入受限模式。受限模式下 CAN 模块不发送数据帧、远程帧、活动错误帧或过载帧,直到总线空闲 CAN 模块会

重新与总线同步。

Host 可以通过设置 CCCR.ASM 寄存器主动进入受限操作模式,该位只能主机在 CCCR.CCE 与 CCCR.INIT 同时设置为 1

时被主机重置。

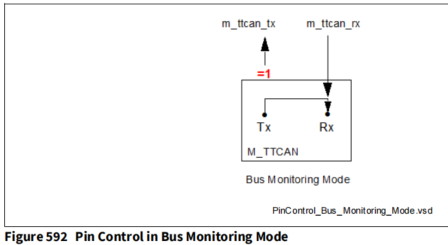

2.6.6、总线侦听模式 Bus Monitoring Mode

M_CAN 模块可以通过设置 CCCR.MON 进入侦听模式,在侦听模式下,CAN 模块的发送被切断,只侦听总线上的报文。

2.6.7、禁用重传模式 Disabled Automatic Retransmission

M_CAN 提供了在传输过程中丢失仲裁或被错误干扰的帧的自动重传的手段。可以通过 CCCR.DAR 禁用自动重传。

2.6.8、休眠模式 Power Down(Sleep Mode)

M_CAN 支持硬件休眠模式,通过设置 CCCR.CSR 寄存器,使能 CAN 模块进入休眠模式。当所有等待发送的报文

完成发送,M_CAN 会自行设置** CCCR.INIT** 来阻止后续报文的发送,此时 M_CAN 通过设置 CCCR.CSA 表征其已经

准备好进入休眠模式了,然后 Host 可以关闭 CAN 模块时钟。

要退出休眠模式,首先也要启动 M_CAN 时钟,然后清除** CCCR.CSR** 寄存器。同样 M_CAN 通过清除 CCCR.CSA 来

表征自己退出休眠模式,然后 Host 可以通过设置 CCCR.INIT,并设置寄存器以重启 CAN 模块

2.6.9、测试模式 Test Mode

M_CAN 模块支持测试模式,通过先将 CCCR.TEST 寄存器置位来开启。

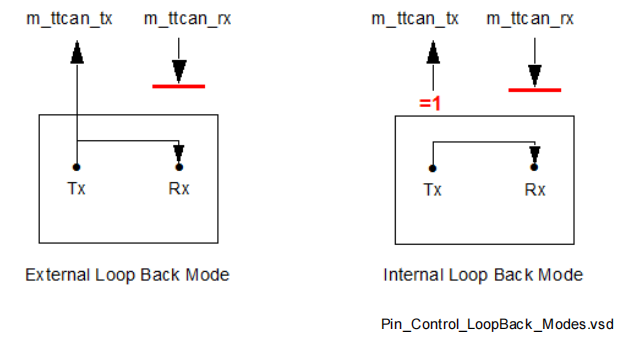

测试模式有两种,一种是 External Loop Back Mode,即外回环模式,通过设置 TEST.LBCK 为 1 来实现。

在该模式下,CAN 模块切断了外界的接收连接,将自己发送的报文视为接收报文,以进行 CAN 回环测试。

在该模式下,CAN 忽略总线应答错误。

另外一种是 Internal Loop Back Mode,即内回环模式,除了 TEST.LBCK,还需要设置 CCCR.MON,区别在

于该模式下 CAN 模块的发送连接也被切断,也就是测试模式和侦听模式组合。

2.7、时间戳功能

M_CAN 模块提供了一个内部 16 位的循环计时器,并且具备一个 4 位的分频寄存器 TSCC.TCP。可通过

TSCV.TSC 寄存器读取计时器的值。当计时器回滚时,中断标志位 IR.TSW 置位。

在接收、发送报文的开始时刻,计时器的值会被保存到 Rx Buffer、Rx FIFO、Tx Event FIFO 的时间戳段中,以

实现计时功能。

2.8、接收流程 Rx Handling

Rx Handler 控制接收过滤,Rx Buffers 和两个 Rx FIFO 接收消息的传输,以及 Rx FIFO 的 Put 和 Get 索引。

2.8.1、接收过滤 Acceptance Filtering

上文提到,M_CAN 提供两套过滤器,分别用于对标准 CAN ID 和扩展 CAN ID 进行 ID 过滤。这些过滤可以被分配

到 Rx Buffer、Rx FIFO1、Rx FIFO2(通过过滤器中字段进行配置)。当收到一帧报文时,会从对应过滤器列表从头到尾

进行匹配。当出现匹配过滤器时,后续的过滤器就不会执行匹配。不同于发送报文,接收过滤器是在初始化阶段由 Host

配置好的,当初始化完成之后 M_CAN 按照指定的配置进行接收过滤。

过滤器主要包括以下特性:

支持以下三种过滤模式:

1、范围过滤(from - to -) 2、一个或两个特定 ID 过滤 3、经典的按位掩码过滤

过滤器可以配置为接收过滤或者拒绝过滤

每个过滤器可以配置独立使能;

过滤器按照顺序依次匹配,出现第一个匹配的过滤器即停止后续过滤;

相关的寄存器包括全局过滤配置寄存器(Global Filter Configuration ,CFG),标准 ID 过滤器配置寄存器(Standard ID

Filter Configuration,SIDFC),扩展 ID 过滤器配置寄存器(Extended ID Filter Configuration, XIDFC),扩展 ID&

掩码寄存器(Extended ID AND Mask,XIDAM)。

当过滤器与接收报文匹配上时,根据 CAN RAM 中过滤器的配置(SFEC/EFEC),执行相应的操作:

将接收帧存储到 FIFO0 或 FIFO1;

将接收帧存储到 Rx Buffer;

将接收帧存储到 Rx Buffer 并在过滤器事件 Pin 上产生信号;

拒绝该帧;

设置高优先级中断标志位 IR.HPM;

设置高优先级中断标志位 IR.HPM,并将接收帧存储到 FIFO0 或 FIFO1;

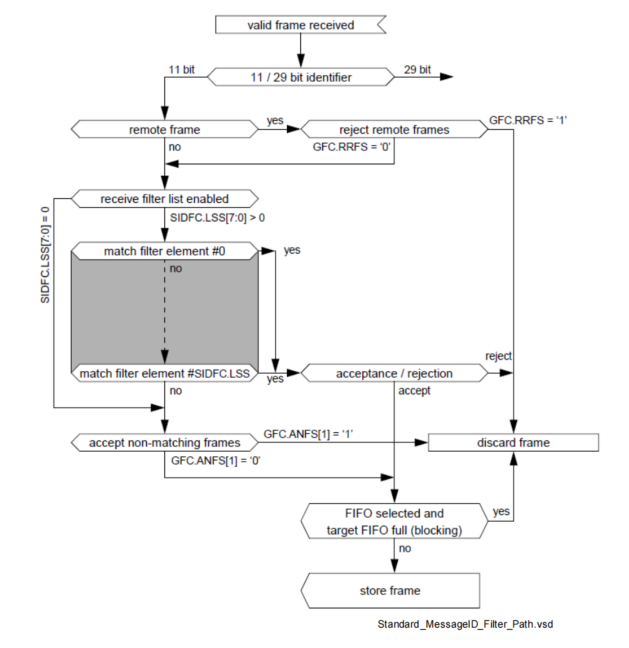

当一帧报文到达 CAN 模块的时候,过滤器的工作流程如下图所示(以标准 ID 帧为例):

由上图可知,当一帧 11bit ID 标准帧到达时,若不是远程帧且接收过滤器使能了,就会进入过滤器匹配环节。

若没有与之匹配的 ID,且配置模式不接收非匹配帧(一般不对非预期帧进行处理),该帧就会被丢弃。如果过滤器

中有与之匹配的 ID,且所引用的存储空间可用(Rx Buffer 或者 FIFO),则进行帧存储。

2.8.2、Rx FIFO

在 AUTOSAR 协议中,CAN 报文类型在接口层分为 FULL CAN 和 BASIC CAN,FULL CAN 表示该报文的处理独占

一个硬件资源,也就是 Rx Buffer;而 BASIC CAN 则表示多个接收帧需要共用一个硬件 FIFO,并且相同 ID 的报文

可以在 FIFO 中存储多次,这个 FIFO 在硬件上就是我们要介绍的 M_CAN 的 Rx FIFO。

每个 M_CAN 节点有两个 Rx FIFO,每个 FIFO 最多可处理 64 帧报文。分别通过 RXF0C 和 **RXF1C **寄存器来进行

Rx FIFO 的配置。初始化阶段我们通过 RXFnC.FnSA 配置该 FIFO 在 CAN RAM 中的相对地址偏移,通过** RXFnC.FnS**

配置该 FIFO 的尺寸,也就是最多容纳的报文数量。通过** RXFnC.FnWM** 配置该 FIFO 的水位线。

当过滤器中的 SFEC/EFEC 字段指定过滤的动作作为存储到 RX FIFO 中,在接收帧与过滤器匹配时,就会被存储到

指定的 RX FIFO 中。

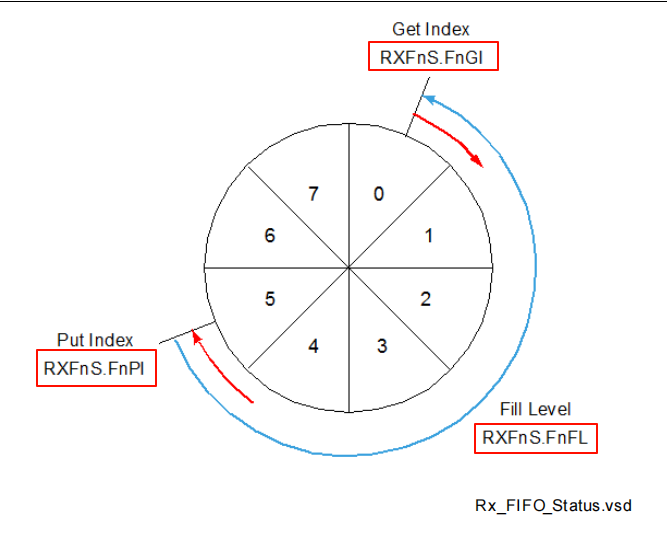

Rx FIFO 的设计结构如下图所示:

该模型的状态由 M_CAN 模块维护,Host 可以通过 RXFnS 寄存器访问。RX FIFO 有两个索引,一个是 Put 索引 RXFnS.FnPI,

接收到报文后从该位置进行存储,然后将 Put 索引累加。另一个是 Get 索引 RXFnS.FnGI,Host 从该位置开始进行报文读取

还有一个填充指示位** RXFnS.FnFL**,用来表征当前 FIFO 里已经有多少报文了,当 FIFO 满了时(Get 索引等于 Put 索引),

FIFO 溢出标志位** RXFnS.FnF** 会置位,同时发送 IR.RFnF 中断信号。

前文中提到通过 RXFnC.FnWM 配置该 FIFO 的水位线,它的作用是当 FIFO 中存储的报文数量达到水位线时,产生 FIFO 中断,

即 IR.RFnW 信号,以促使 Host 进行接收报文处理。

RX FIFO 在 CAN RAM 中的相对地址偏移分别为** RXF0C.F0SA** 和 RXF1C.F1SA。与 Tx Buffer 形式相同,每个 Rx FIFO 包含 3 个

Word 的头和特定长度的数据,数据尺寸由 **RXFcF.FnDS **决定。

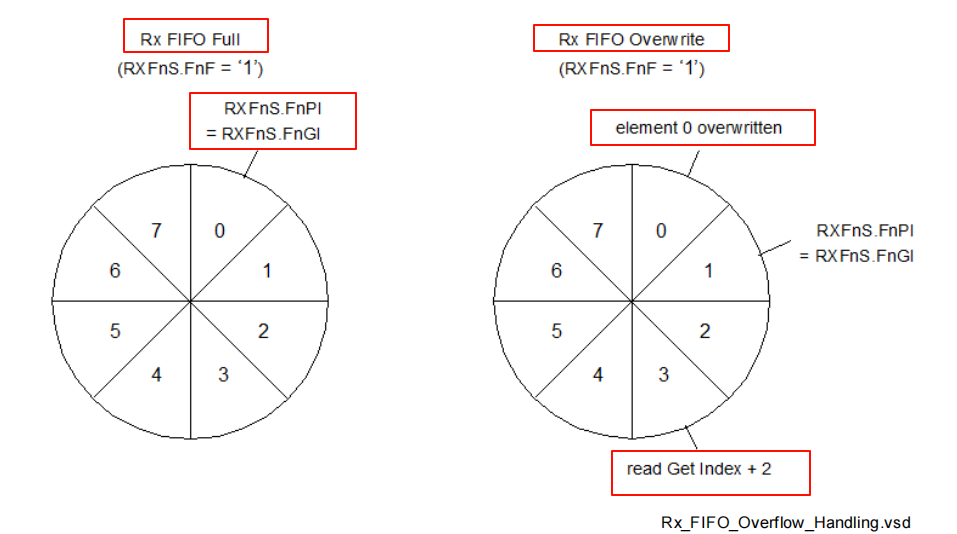

Rx FIFO 由两种工作模式,通过操作 RXFnC.FnOM 来控制。当 RxFnC.FnOM = 0 时,Rx FIFO 配置为默认的 Block 模式,该

模式下,若 FIFO 满了,将不在接收任何报文。当 RXFnC.FnOM = 1 时,Rx FIFO 配置为覆写模式,在该模式下若 FIFO 满了

新接收的报文将覆盖最旧的一帧报文,并且将两个索引都累加。如下图:

2.8.3、Rx Buffer

当配置接收帧为 FULL CAN 时,也就给该帧配置了一个专属的 Rx Buffer,用于该帧的报文接收。每个 M_CAN 最多可配置 64 个

Rx Buffer,其在 CAN RAM 中的相对地址偏移由 RXBC.RBSA 指定,Rx Buffer 的格式与 Rx FIFO 完全相同,每个 Rx Buffer 包含 3 个 Word 的头和特定长度的数据,数据尺寸由 RXBC.RBDS 决定。

在过滤器 ID 匹配成功时,且过滤器中的 SFEC/EFEC 为 111b(表示帧存储到 Rx Buffer 中),且 SFID2/EFID2[10:9] 为 0(非 Debug 帧),则 CAN 模块将该报文存储到指定的 Rx Buffer 中,其中 Rx Buffer 的索引由过滤器中 SFID2/EFID2[5:0] 位域

指定。同时中断标志位 IR.DRX(Message stored in Dedicated Rx Buffer)置位,即常见的 CAN 接收中断。

除此之外,接收完成之后,对应的 New Data Flag 寄存器 NDAT1 或** NDAT2** 中的位会置位(每个 Buffer 一个位),在该位被

清除前,该 Rx Buffer 将拒绝数据接收,同时对应的过滤器也停止进行过滤,但是位于该过滤器后面的其它过滤器可以继续对

该帧,也就是说该帧可以被存储到其它的 Rx Buffer 或者 FIFO 中。用户可以通过对该位写 1 进行清除。

接收的处理流程如下:

1、清除中断标志 IR.DRX;

2、读取 New Data Flag 寄存器确定需要处理的 Buffer;

3、从 CAN RAM 中读取数据;

4、清除处理好的 Buffer 的 New Data Flag。

2.9、发送流程 Tx Handling

Tx Handler 处理专用 Tx Buffers、Tx FIFO 和 Tx Queue 的传输请求。它负责传输报文到 CAN Core,管理 Put 和 Get 索引

以及 Tx Event FIFO 的传输。不同于 Rx Buffer 和 Rx FIFO 有各自的独立资源,在发送端专用 Tx Buffer 和 Tx FIFO、Tx Queue

共用 32 个 Tx Buffer。

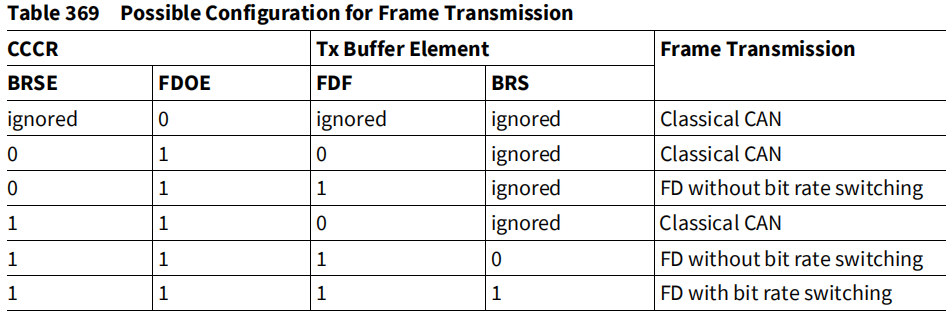

CAN 模块在发送端可以发出三类报文:普通报文、非变速 CANFD 报文、变速 CANFD 报文,受节点的 CCCR 寄存器和每个

Tx Buffer 内部的配置影响,参照如下表:

Tx Handler 在每次发送 Buffer 请求等待寄存器(Tx Buffer Request Pending register,** TXBRP**)更新时执行依次扫描,然后在

CAN RAM 中寻找优先级最高(CANID 最小的 Tx Buffer)的等待中的 Tx Buffer 开始发送。而 TXBRP 是在每次有一帧发送完

成,或者有用户通过写发送 Buffer 添加请求寄存器(Tx Buffer add Request register,TXBAR)时更新。即发送完一帧,或者

用户添加发送请求,Tx Handler 就会开始执行发送扫描,寻找优先级高的 Tx Buffer 然后发送。

2.9.1、Transmit Pause( 发送暂停)

CAN 总线是无主式通讯,仲裁的依据是 CANID。但如果具有高优先级 ID 的控制器以较高的频率持续发送报文,持有低

优先级 ID 的控制器便无法将报文发出。因此 CAN 控制器存在一个发送暂停的功能,通过将 CCCR.TXP 置位来使能。使能

之后,该控制器在完成每帧发送之后,会进行两个 bit 的暂停,以保证低优先级 ID 的报文能够发送到总线上。

2.9.2、Tx Buffer

每个 M_CAN 最多可配置 32 个 Tx Buffer,其在 CAN RAM 中的相对地址偏移由 TXBC.TBSA 指定,每个 Tx Buffer 包括两个

Word 的头和若干数据组成,每个 CAN Node 的数据长度由 TXESC.TBDS 获取指定,比如 CAN FD 一般数据为 64 字节。

Tx Buffer 可以用作给特定帧的专有 Buffer,也可以组成 Tx FIFO、Tx Queue,更可以组成 Tx Buffer 与 FIFO/Queue 的混合

模式,这种使用较少。但是 FIFO 与 Queue 是二选一存在的。

专有 Tx Buffer 是完全由 Host 来控制的,每个 Tx Buffer 指定专有的 CAN ID。和接收一样,专有 Tx Buffer 对应配置中的

FULL CAN。以防 多个 Tx Buffer 具有相同的 CAN ID,因此 Tx Buffer 的发送顺序是按照 Buffer 的序号进行的进行的,低

序号的 Tx Buffer 具有优先发送权,一般也会将较小 ID 的报文分配给靠前的 Tx Buffer 。每个 Tx Buffer 都可以通过写

TXBAR 寄存器中的关联位单独进行发送请求添加。

2.9.3、Tx FIFO

当把 TXBC.TFQM 配置为 0,并通过 TXBC.TFQS 配置一定数量的 Tx Buffer 用作 FIFO,就可以使用 Tx FIFO 模式进行报文

发送,并允许同一个 ID 的报文多次添加到 FIFO 中。FIFO 的结构同样类似 Rx FIFO,有一个 Get 索引** TXFQS.TFGI**,和一个

Put 索引 TXFQS.TFQPI,用来指示头和尾。用 TXFQS.TFFL 来指示当前 Buffer 空闲数量

当 Host 执行发送请求时,Put 索引进行累加,当 Tx Handler 执行发送时,Get 索引进行累加。当 FIFO 满了以后,

TXFQS.TFQF 置位。

2.9.4、Tx Queue

当把** TXBC.TFQM** 配置为 1,并通过** TXBC.TFQS** 配置一定数量的 Tx Buffer 用作 Queue,就使用了 Tx Queue 模式。Queue

中的报文从 ID 小的开始执行发送,当 Queue 中出现相同 ID 的 Buffer,则先从 Buffer 序号小的发送,Tx Queue 只有一个

Put 索引** TXFQS.TFQPI**,用于指示 Queue 中序号最小的可用 Buffer。

当新的发送请求发送到 Tx Queue 中,Put 索引会自动指向下一个 Queue 中序号最小的可用 Buffer。当 Queue 满了时

(TXFQS.TFQF),Put 索引成为无效值,并且后续报文无法添加到 Queue 中,直到一个报文发出去或者报文被取消。

2.9.5、发送取消(Transmit Cancellation)

M_CAN 支持发送取消功能,该特性是专门为 AUTOSAR 中网关应用程序设计的。为了取消 Tx Buffer 或者 Tx Queue 中的

pending 报文的发送,Host 需要向发送 Buffer 取消请求寄存器(Tx Buffer Cancellation Request register,TXBCR)中的相关

位 CRn 写 1。Tx FIFO 中的报文无法取消。

取消成功后,TXBCF 中的相应位 CFn 会置位。

若一帧已经在发送流程中了,若最终没有取消成功,那么 TXBCF 和 TXBTO 中的相应位都会置位,若取消成功,那么只有

TXBCF 中相应位置位。

2.9.6、发送事件 FIFO Tx Event FIFO

为了支持发送事件处理,M_CAN 维护了一套 Tx Event FIFO 机制。在 CAN RAM 设置了一块内容,专门保存 CAN 发送事件

的信息。当 CAN 模块往总线上发送一帧报文之后,报文 ID、Message Marker、时间戳等信息就会被保存到 Tx Event FIFO

这么做的目的是把 CAN 发送处理和发送事件信息分开处理,好处是当一帧报文发送完成之后,Tx Buffer 能够立刻给下一帧

使用,尤其是在 Tx Queue 模式下。

当出现新的 Tx Event 之后,触发中断标志位** IR.TEFN**,表示专有 Tx Buffer、Tx FIFO 有发送完成,一般将该信号用作 CAN

发送中断。

Tx Event FIFO 满了之后会触发中断标志位 IR.TEFF。后续的事件无法继续保存,直到下一次读取发生。

为了避免 FIFO 溢出,可以使用 Tx Event FIFO 水位线,通过设置 TXEFC.EFWM,当 Tx Event FIFO 中的事件数量达到了

水位线,将中断标志位 IR.TEFW 置位。

2.10、FIFO Ack 机制

上文提到的 Rx FIFO0、FIFO1 和 Tx Event FIFO,它们的 Get 索引都是通过 Ack 机制来实现控制的。通过写入指定

的 Ack 寄存器,来将 FIFO 的 Get 索引进行累加。比如在从 Rx FIFO0 中接收报文完成之后,需要在接收 FIFO0

应答寄存器(Rx FIFO 0 Acknowledge,RXF0A)来修改与该 Buffer 关联的索引号。

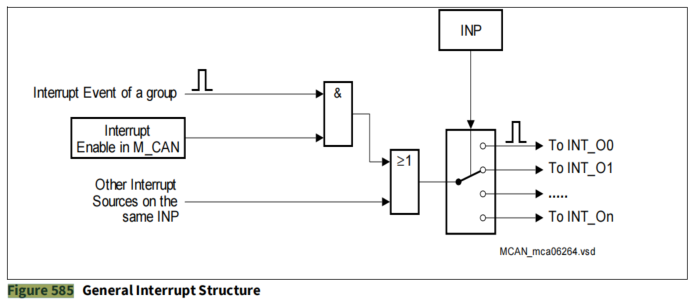

2.11、中断连接

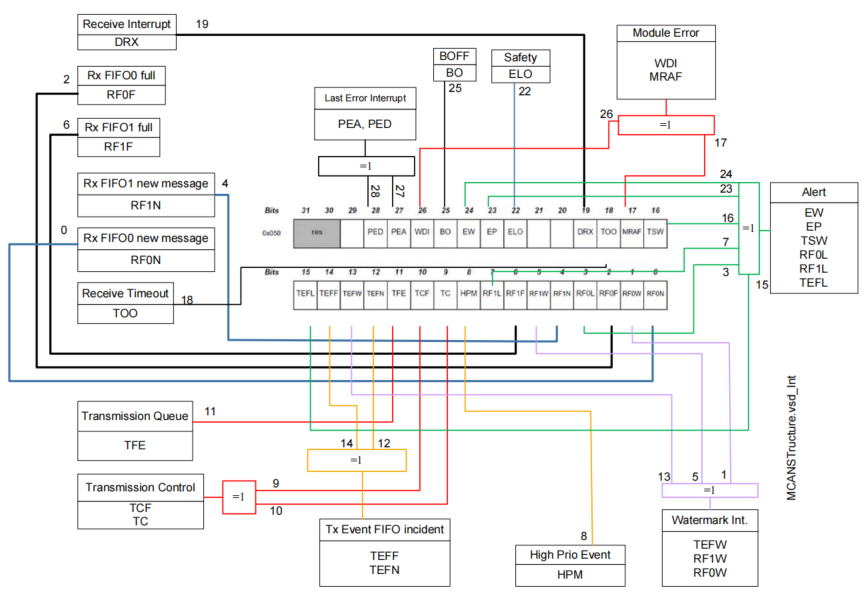

一个 M_CAN 节点提供了十几种中断,包括前文提到的接收中断、发送完成事件中断等。如下图:

首先在 M_CAN 模块内部,对于每种类型的中断,在中断使能寄存器 CAN_N_IE 中都有一个专属的使能位。该使能

位需要在启动阶段由 Host 设置(一般在 Start Controller)

然后在 TC3XX 的中断路由模块 IR 中,每个 CAN Module 分配了 16 个中断源,也就是说一个 Module 中的 4 个

Node 要共用这 16 个中断源,每个 Node 的中断信号与这 16 个中断源是可以任意连接的,来自这些 Node 的多个

信号也可以连接到同一个中断源中。通过设置 Node 中的 GRINT1 和** GRINT2** 来为 Node 中的中断信号指定中断源

一般情况下,我们会将 16 个中断源平均分给 4 个 Node,每个 Node 使用 4 个关键中断信号,分别分配给 Rx Buffer

中断、Tx Buffer 中断、BusOff 中断和 Rx FIFO 中断。

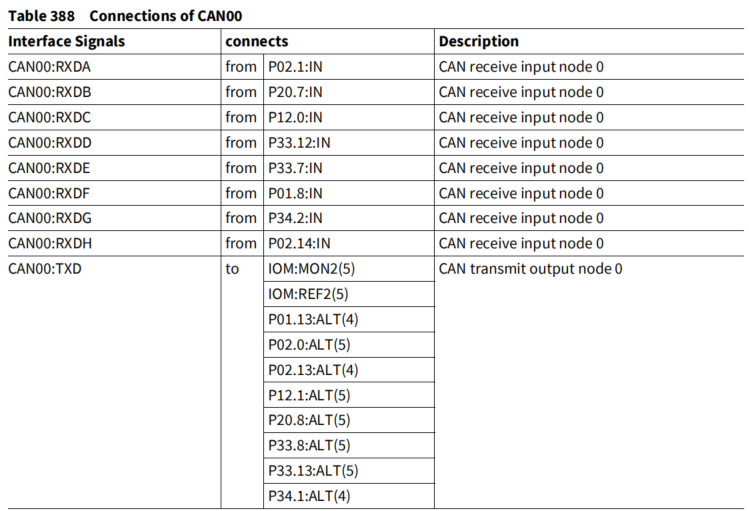

2.12、引脚连接

TC3XX 中 CAN 模块与 Port 的连接也是比较丰富的,对于每个节点都有多组引脚可选为 CanRx 和 CanTx 信号。

连接需要指定型号的用户手册(非 Family 手册),这里我们以 TC38X User Manual 为例,我们打开手册 38.4

MCMCAN Connectivity 章节,找到** Table 388 Connections of CAN00**。

这里 CAN00 表示是 CAN Module0,Node0 的连接关系,如果是 Module1,Node2 就是 CAN12,以此类推。

CAN00 提供了 8 对引脚可供选择,我们从硬件设计获悉引脚关系后,查询对应的 Rx Signals,比如 Rx 硬件

连接为 P12.0,则在 MCAL 中配置 Rx 为 RXDC。发送端不需要配置,因为对于 CAN 模块来说,对每个内部

连接都进行发送,由 Port 来配置使用哪个。

选择了对应的 Rx Tx 引脚之后,在 Port 端进行引脚功能配置即可。

3、Mcal 配置介绍

3.1、General 介绍

General 中还是一些常规接口使能配置:

CanMainFunctionModePeriod:CAN 的发送接收等可以选择是中断还是轮询,若选择中断,可忽略该配置

CanMultiplexedTransmission:该配置表示是否使用 Tx FIFO/Tx Queue 和专有 Tx Buffer 混用。

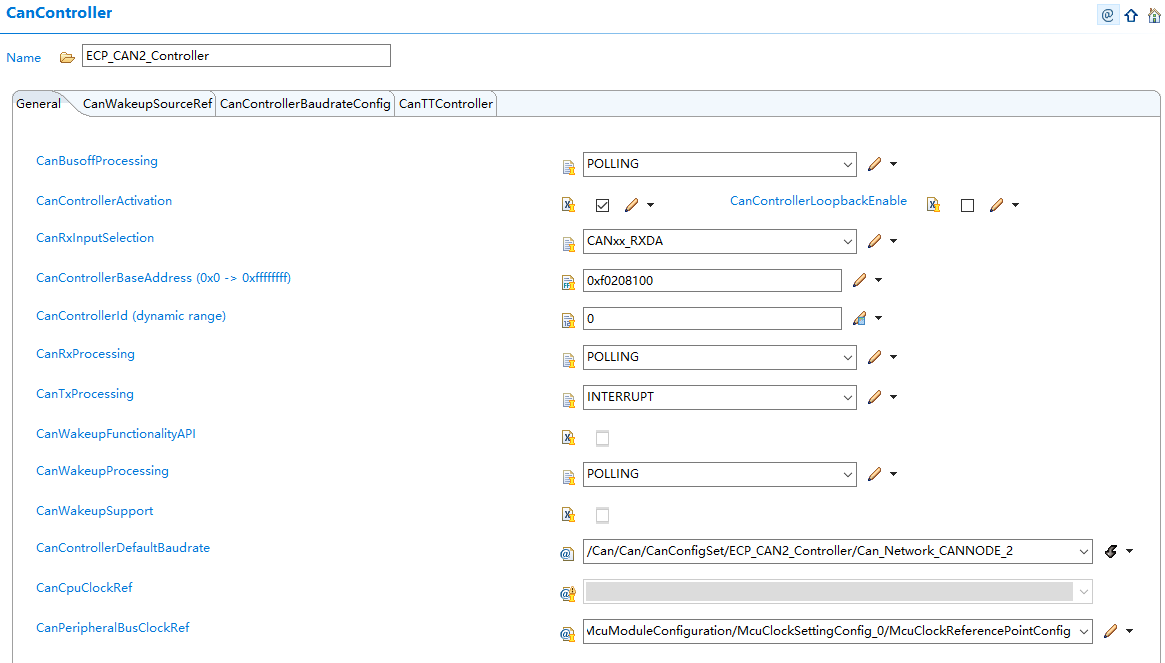

3.2、Can Controller

Can Controller 对应 Can Node 配置,每路 CAN 有各自的一个 Controller。

CanBusoffProcessing、CanRxProcessing、CanTxProcessing、CanWakeupProcessing:中断、轮询选择。如上所述,若选择

Polling 就是在 MainFunction 中轮询。

CanControllerActivation:Controller 激活,勾选视为激活。

CanControllerLoopbackEnable:内部总线测试连接,注意非测试软件不要勾选,且勾选后 RxInputSelection 默认只能使用 RXDA

CanRxInputSelection:Rx 引脚选择,如上所述:

CanControllerBaseAddress:CAN Controller 基址,MCAL 配置中对于该 Controller 使用哪个 Module 的哪个 Node,由本参数决定,对应 ACCENNODE0 寄存器的地址,可在对应型号手册中查询,或者 IfxCan_reg.h 文件中搜索 CAN0_N0_ACCENNODE0,例如 Module0 Node0 的 ACCENNODE0 地址为 0xF0208100;

CanControllerld:Controller 的软件 ID 标识;

CanWakeupFunctionalityAPI:Can_CheckWakeup()使能;

CanControllerDefaultBaudrate:默认波特率配置引用,我们可以配置多种波特率,并在运行时切换,这里配置启动后的默认波特率;

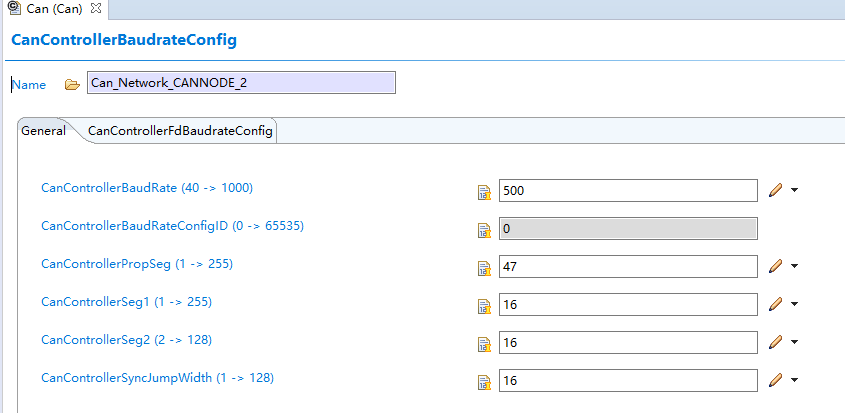

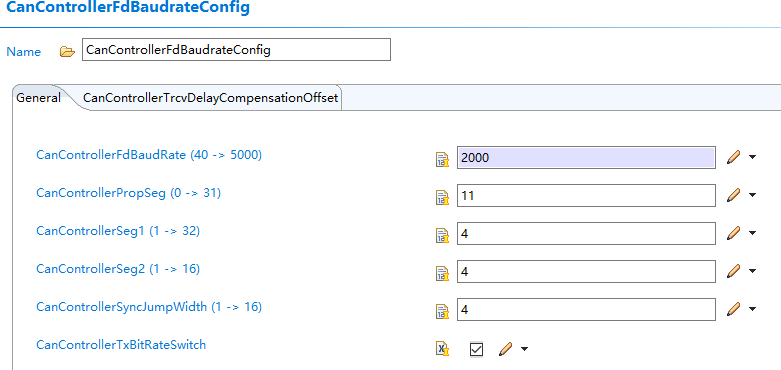

3.3、CanControllerFdBaudrateConfig

这里对应上面提到的波特率计算,用户根据实际需求填写传播段、相位缓冲段等参数即可。需要注意的是,时钟

分频是不能填写的,而是工具根据这些参数自动计算的。

如下图 CANFD 波特率设置同理,若配置了第二采样点,则打开了发送采样延时补偿,由硬件自动标定,配置的任意

数字都只是使能。

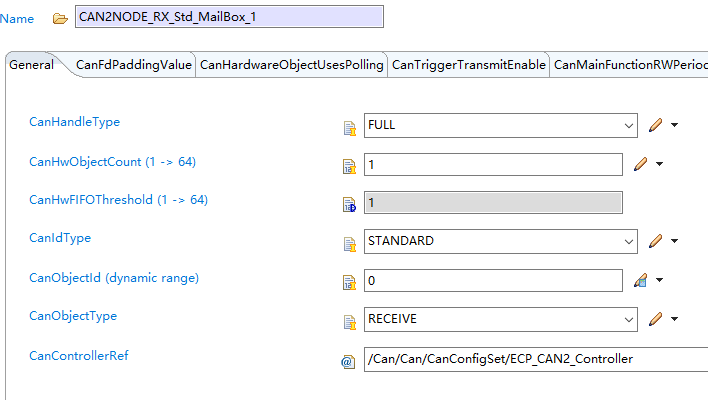

3.4、CanHardwareObject

CanHardwareObject 是对发送、接收帧硬件资源定义的地方,也就是配置前文提到的 Rx Buffer、Tx Buffer 等。

CanHandleType:硬件资源类型,这里我们 FULL CAN,使用专有 Buffer,配置为 1 即可

CanHwObjectCount:Tx FIFO 数量。若为 FULL CAN,配置为 1 即可;

CanHwFIFOThreshold:Tx FIFO 水位线,即中断触发阈值;

CanIdType:ID 类型,标准 11 位还是扩展 29 位

CanObjectType:Obj 类型,发送还是接收

CanControllerRef:分配给哪个 Controller;

1140

1140

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?