超低功耗亚阈值电路设计中的MOSFET综合掺杂方案

摘要

用于亚阈值电路的器件不需要像传统的超阈值器件那样采用晕圈和倒退掺杂。这将显著减少亚阈值器件制造工艺中的步骤数、寄生电容和衬底噪声。本文提出了一种适用于亚阈值电路中晶体管的全新综合掺杂方案。所提出的掺杂方案将在晶体管的源极和漏极区域以及衬底和沟道区域引入掺杂变化。该掺杂方案的特点是在源极端和漏极端不存在晕环结构。我们建议在源极和漏极区域内采用高斯掺杂分布,并从沟道表面向体区方向,在晶体管深度上呈现低‐高‐低的掺杂分布。此外,在沟道区域下方沿晶体管长度方向也具有低‐高‐低的掺杂分布。结果表明,采用所提出的掺杂分布的优化器件在更小的体偏置条件下可提供更高的开态电流(Ion)。通过改变掺杂轮廓、体偏置和栅‐源电压(Vgs),对所提出的掺杂分布进行了分析,以观察关态电流(Ioff)、阈值电压变化、Ion/Ioff比值的大小、跨导以及输出电导的变化情况。

& 2016 爱思唯尔有限公司. 版权所有。

1. 引言

超低功耗电路设计由于电池供电设备、便携式设备、传感器和 biomedical 应用的广泛使用,已成为一个极为关键的研究重点。使器件工作在亚阈值区是设计超低功耗电路最有效的方法。亚阈值电路的行为与超阈值电路不同,因此沟道掺杂等器件参数需要针对亚阈值和超阈值电路进行不同的优化。对于超阈值工作,通常采用逆向掺杂和晕圈掺杂分布来最小化短沟道效应、体穿通、漏极感应势垒降低(DIBL)以及阈值电压的变化。逆向沟道剖面(RCP)(也称为低‐高掺杂剖面)在晶体管表面附近区域掺杂较轻,而衬底掺杂较重。如果从轻掺杂表面到重掺杂衬底的过渡非常陡峭,则称为超陡倒退(SSR)剖面。与RCP相反的是高‐低掺杂剖面,其表面掺杂较高,内部掺杂较低衬底。低‐高和高‐低掺杂分布的替代方案是均匀掺杂(UD)分布。中提供了SSR与UD沟道的比较。对于给定的阈值电压,高‐低掺杂分布的耗尽层宽度大于均匀掺杂(UD)分布,而低‐高掺杂分布的耗尽层宽度小于均匀掺杂(UD)分布。为了抑制短沟道效应,提出了双晕圈(DH)和单晕圈(SH)或横向非对称沟道(LAC)器件等不同的沟道工程技术。此外,超阈值电路需要采用缩放的非均匀掺杂分布,以更好地控制器件的电学特性。

再次强调,为CMOS数字电路优化的掺杂方案可能并不适用于模拟和混合信号电路。在[3],中,分析并比较了具有LAC的MOSFET按比例缩小对模拟和混合信号性能的影响与传统MOSFET的差异。结果显示,采用LAC的器件在模拟性能方面有显著提升(包括器件增益、跨导与驱动电流比(即跨导生成因子)、输出电阻、阈值电压失配等)。双口袋或超级晕圈器件在数字性能方面表现优异(表现为高Ion/Ioff比以及对漏电流和短沟道效应的良好控制),但其模拟性能通常不如SSR器件[3]。基于亚阈值器件工作的模拟电路由于漏极电流的指数特性,还具有显著更高的增益优势亚阈值区。这种指数行为确保了更高的跨导生成因子(gm/Id)。研究表明,新型单口袋器件相比传统SSR器件具有更优的本征模拟性能。结论是,对于模拟、数字和混合信号电路而言,存在许多因素(栅极电容、射频性能、载流子密度、漂移速度、漏致势垒降低等),它们对掺杂分布具有相互冲突的依赖性或要求。因此,亚阈值工作的掺杂分布必须针对特定需求进行优化。

与超阈值电路相比,亚阈值电路在低得多的电压下工作。在亚阈值区,许多期望和非期望效应将有所不同。研究人员已得出结论:亚阈值器件不需要晕圈掺杂[7]。这将简化制造工艺并减少许多寄生效应。这促使我们寻找适用于亚阈值设计器件的合适掺杂剖面。近年来,针对超低功耗应用的亚阈值电路的各种掺杂方案引起了广泛关注。我们最近提出了一种用于亚阈值电路中晶体管沟道和衬底区域的3D掺杂方案[8,9]。

包括我们论文在内的大多数现有工作[8,9]集中于沟道和体区掺杂剖面的优化,并假设源极和漏极区域采用均匀掺杂。本文提出一种新的综合掺杂方案,该方案将同时解决源极、漏极区域以及沟道和体区的掺杂问题。本文其余部分组织如下。第2节阐述了所提出的掺杂方案的总体概述。第3节提供了所提出的亚阈值器件掺杂剖面组合的结果与分析。第4节总结了本文的成果。

2. 亚阈值器件的综合掺杂方案

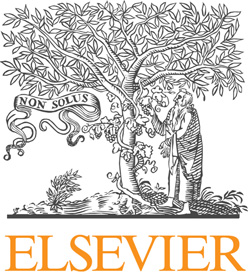

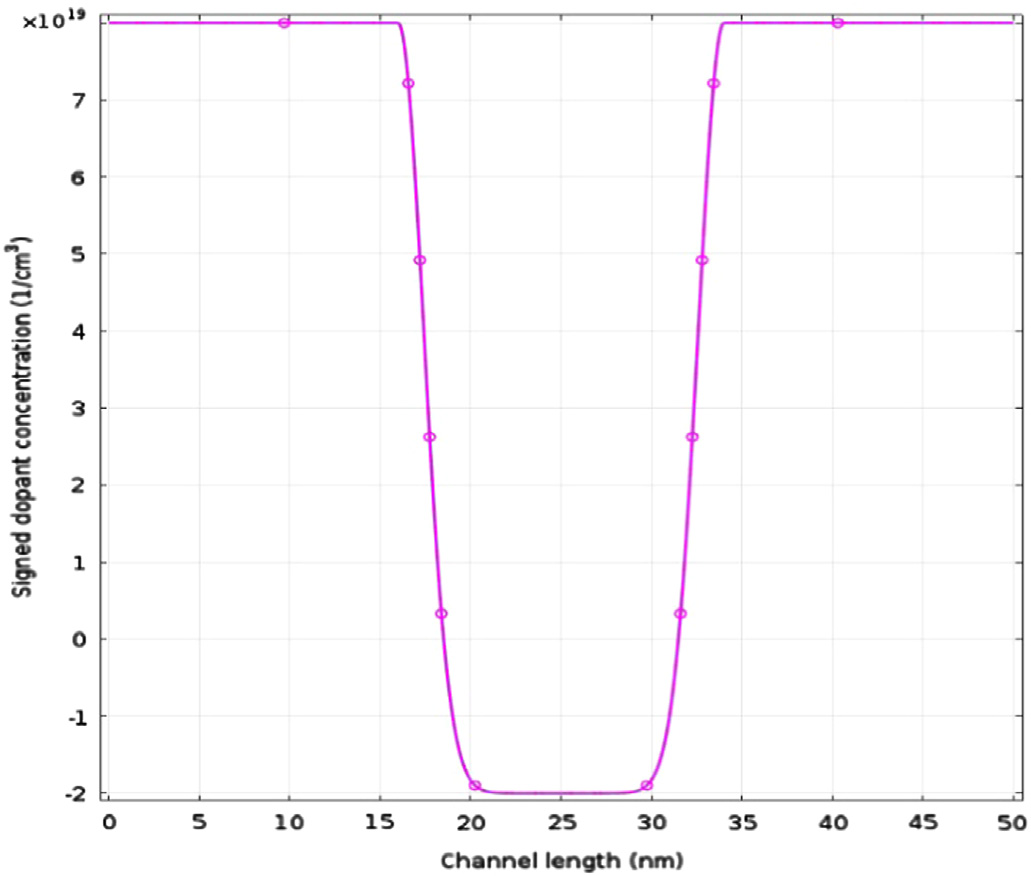

我们为亚阈值电路提出的掺杂方案将对源极和漏极区域以及衬底和沟道区域带来改变。所提出的综合掺杂方案如图1所示。该掺杂方案的特点是在源极端和漏极端没有晕环结构。我们提出在源极和漏极区域内采用高斯掺杂分布,并且从沟道表面向体区方向,在晶体管深度上呈现低–高–低的掺杂分布。此外,在沟道区域下方沿晶体管长度方向也具有低–高–低的掺杂分布,如图1所示。

在所提出的方案中,整体掺杂过程将包括四个步骤。对于N沟道MOS晶体管,首先在所有区域中分布恒定的背景受主掺杂剂。第二步,对源极和漏极区域进行注入掺杂。此处我们建议采用高斯doping profile在源极和漏极区域的分布如图1所示。在定义源极/漏极的高斯掺杂分布时,引入了一个具有恒定高浓度施主掺杂的矩形区域。高斯衰减发生在该高掺杂矩形区域边缘之外。随后指定了高斯衰减发生的长度。通过分布一个恒定背景受主浓度掺杂水平来完成高斯衰减。

一种低–高–低掺杂剖面file沿着栅极下方器件深度方向至衬底被考虑。沟道区域下方的均匀高掺杂区并未从源极延伸至漏极,而是仅覆盖中间部分,在两端留下间隙(低掺杂区域),如图1所示。因此,在所提出的方案中,低–高–低掺杂剖面file同时沿器件深度方向和沟道长度方向被考虑。首先分析沿深度方向的低–高–低掺杂。中心处的高掺杂维持了阈值电压,栅极表面附近的低掺杂降低了隧穿效应,而靠近衬底一侧的低掺杂则确保了更小的体漏电流。接下来关注从源极端到漏极端沿沟道长度方向的低–高–低掺杂分布。从源极到漏极沟道下方的这种低–高–低掺杂剖面file减少了栅极在源极和漏极两侧的错位效应。此外,源极和漏极端附近的低掺杂保证了高迁移率、降低的峰值电场以及碰撞电离。

本文表明,对于特定的技术代,通过为亚阈值工作专门重新设计器件,可以在亚阈值区实现更低功耗和更高性能。在当前的设计实践中,标准晶体管在亚阈值区工作以实现亚阈值逻辑[10]。然而,为了更好地控制器件的电学特性,期望采用非均匀掺杂分布。此前已提出高‐低掺杂分布用于亚阈值工作[10]。具有极低偏置电压的亚阈值器件经历最小的短沟道效应。这允许降低沟道源端和漏极端的掺杂浓度。基于这一观察,我们建议在源端和漏端减少掺杂量。在超阈值器件中,源/衬底和漏/衬底附近的晕环或LAC区域显著增加结电容,从而增加逻辑门的开关功耗和延迟。我们提出的在源端和漏端两侧均采用低掺杂将降低结电容。在体材料底表面Y方向上提出的低‐高‐低掺杂分布将导致底部结电容减小,并减轻衬底噪声效应和寄生闩锁问题。沟道区域与体材料低端之间的强掺杂将有助于在低阈值电压下更快地形成沟道。

3. 结果与分析

我们已进行了COMSOL多物理场分析,以研究所提出的掺杂分布对器件行为的影响。引入金属接触以定义源极端的金属‐半导体界面。该端子可连接至零偏压或负偏压,以调节阈值电压。在漏极端也形成类似类型的金属‐半导体界面,并连接至0 V。第三个金属连接到衬底的底部区域,可根据需要连接至零偏压或任意固定偏压,以控制阈值电压。栅极由厚度为1纳米、氧化物介电常数为4.5的薄绝缘层构成。文献[11]中提出了一种基于亚阈值电流‐电压(I–V)特性提取二维掺杂分布的技术。

我们基于MOSFET亚阈值电流建模采用与[11]相同方法提出的沟道掺杂分布。该模型的推导以N沟道MOS晶体管为例,但可轻松推广至P沟道MOS晶体管。在我们的分析中,源极和漏极矩形区域内的掺杂浓度被视为均匀的ND=1×10²⁰ cm⁻³。从栅极下方1纳米开始无任何掺杂(除背景掺杂外),随后在距栅极表面3.5纳米范围内分布有高浓度的均匀受主掺杂NA=1×10¹⁹ cm⁻³,之后衬底内部则为低掺杂(背景掺杂)。本文考虑的沟道长度为15纳米。恒定的背景受主掺杂剂浓度设为N₀=1×10¹⁹ cm⁻³。

在常规体硅晶体管中,随着漏极电压的增加,短沟道效应或夹断效应是一种非常常见的现象。在我们的仿真中,针对特定掺杂分布的电子浓度图显示,在漏极端处的短沟道效应或夹断效应非常小。对于极短沟道器件而言,短沟道效应(SCE)将对器件性能至关重要。我们的分析表明,在采用所提出的掺杂方案的器件仿真中未发生夹断现象。这使其成为超低功耗电路工作的理想选择。此外,在施加任何偏置电压之前,源极和漏极端的电场是均匀的。当偏置电压增加时,由于电子准费米能级降低,导致漏极端的反型电荷密度减小,从而降低了漏极端电势的幅值。同时,y方向的电势变化比x方向的电势变化更剧烈。与此同时,源极端的电势幅值增加。并且随着偏置电压的增加,电势减小。

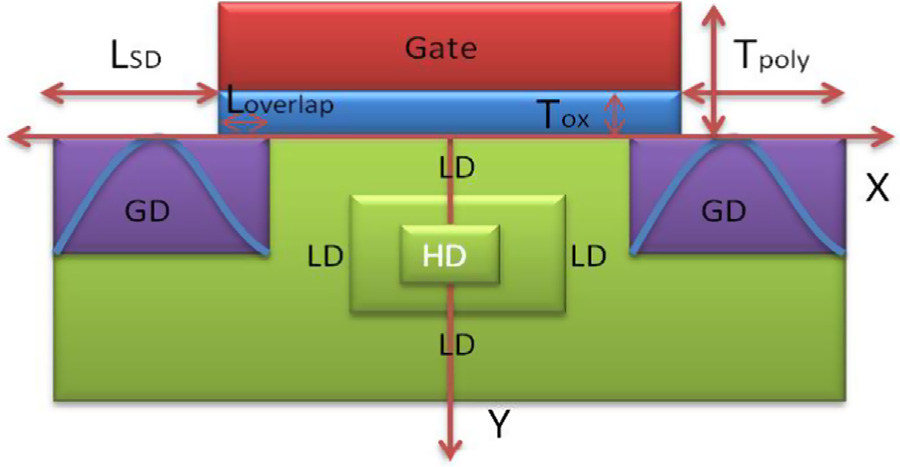

栅极电压与漏极电流的关系,其中Vd=0.01 V且Vbs=0 V。阈值电压约为0.17 V。(b) 栅极电压与漏极电流的关系,其中Vd=0.01 V且Vbs=-0.1 V。阈值电压约为0.20 V。)

栅极电压与漏极电流的关系,其中Vd=0.01 V且Vbs=0 V。阈值电压约为0.17 V。(b) 栅极电压与漏极电流的关系,其中Vd=0.01 V且Vbs=-0.1 V。阈值电压约为0.20 V。)

图2a显示了在零体偏压Vbs=0 V时栅极电压与漏极电流的变化关系,图2b显示了Vbs=-0.1 V时的情况。在这两种情况下,偏置电压均保持在Vd=0.01 V。从图2a可以看出,在零体偏压(晶体管的体区和源极相连)时的阈值电压约为Vgs=Vth=0.17 V;而图2b显示当体偏置Vbs=-0.1 V时,阈值电压为Vgs=Vth=0.2 V。在负体偏置情况下,源极与体结保持反向偏置。随着Vbs变得更负,更多的空穴被吸引到衬底连接处,留下更多的负电荷,耗尽区变得更宽。

从(1)可以看出,阈值电压是耗尽区中总电荷的函数,因为在反型层形成之前,栅极电荷必须与耗尽电荷相平衡。这就是负体偏压导致阈值电压升高的原因。跨导由gm = dId/dVgs定义,也受到体偏置的影响。从图2a和b中可以明显看出,与Vbs=-0.01 V体偏置相比,零体偏压降低了跨导效应。

$$

V_{th} = V_{FB} + 2\psi_B + \frac{t_{ox}}{\sqrt{\frac{4\varepsilon_s\varepsilon_0 q N_A \psi_B}{q}}} \cdot \frac{1}{\varepsilon_{ox}/\varepsilon_0}

\tag{1}

$$

$$

V_{FB} = \phi_m - \chi + \frac{k_B T}{q} \ln\left(\frac{n_e}{N_c}\right)

\tag{2}

$$

$$

\psi_B = \frac{k_B T}{q} \ln\left(\frac{p_e}{n_i}\right)

\tag{3}

$$

此处 $ t_{ox} $ 为氧化层厚度,$ \varepsilon_{ox} $、$ \varepsilon_0 $ 和 $ \varepsilon_s $ 分别为氧化物、自由空间和衬底的介电常数,q 为电子电荷,$ N_A $ 为沟道中的受主浓度,$ V_{FB} $ 为平带电位,$ \psi_B $ 为本征能级与费米能级之间的电势差。$ \phi_m $ 为金属接触的功函数,$ \chi $ 为电子亲和能,$ N_c $ 为导带中的半导体态密度,$ n_i $ 为本征载流子密度,$ n_{eq} $ 和 $ p_{eq} $ 分别为平衡电子和空穴密度。

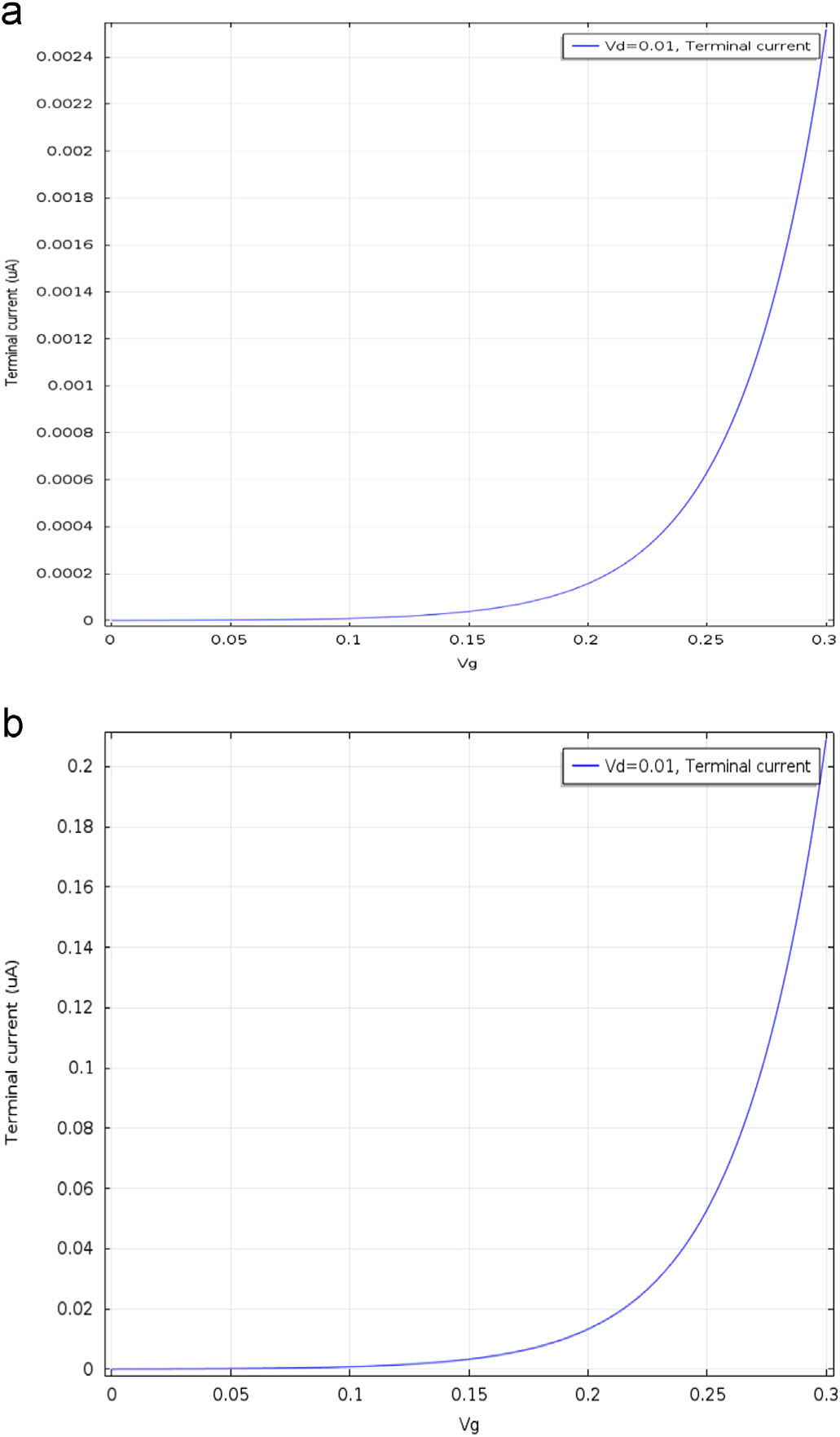

不同栅极电压下的漏极电压与漏极电流关系,以及(a)Vbs=0 V,(b)Vbs=-0.1 V。)

不同栅极电压下的漏极电压与漏极电流关系,以及(a)Vbs=0 V,(b)Vbs=-0.1 V。)

图3显示了不同栅极电压下漏极电压与漏极电流的关系曲线。该曲线表现出三个工作区域:(a) 低电压下的线性区,(b) 中等电压下的非线性区,以及(c) 高电压下的饱和区。电流饱和是由于所谓的夹断效应引起的。当漏极电流增大时,更多电流沿沟道流动,沿其长度方向的电势降也随之增加。因此,栅极与半导体之间的电压随沟道位置而变化。

图3a显示了在不同栅极电压和零体偏压下的漏极电流变化,而图3b显示了施加体偏置Vbs=-0.1 V时的相同电流曲线。这种分析展示了不同体偏置下漏极电流大小的变化。在零体偏压情况下,漏极电流的幅度低于体偏置为Ion的电流。负体偏置有助于更快、更强地形成反型层,从而在较低的栅极偏置电压下产生更大的电流。

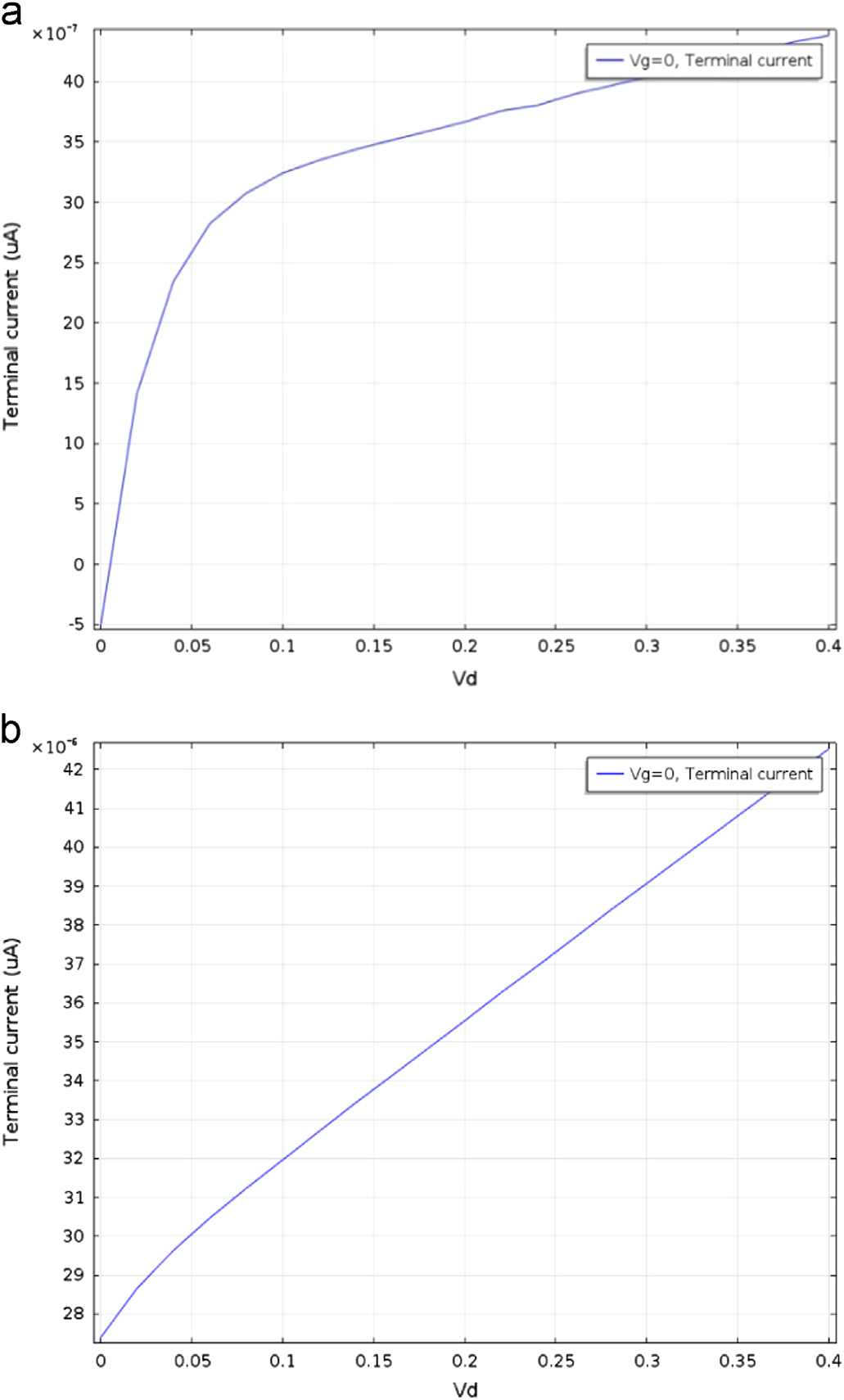

关断电流是指在栅极电压为零时从源极到漏极的电流。图4(a)和(b)显示了Vbs=0时的关断电流和Vbs=-0.1 V时的关断电流。

Vbs=0 V,(b)Vbs=-0.1 V。)

Vbs=0 V,(b)Vbs=-0.1 V。)

表1 晶体管行为总结。

| 晶体管参数 | Vbs=0 V | Vbs=-0.1 V |

|---|---|---|

| 阈值电压,Vth | 0.17 V | 0.2 V |

| 开态电流,Ion | 0.016 mA | 0.26 mA |

| 关断电流,Ioff | 4×10⁻⁶ mA | 42×10⁻⁶ mA |

| Ion/Ioff | 4000 | 6190 |

为了证明我们提出的掺杂方案的合理性,我们将结果与表2中关于不同MOS掺杂技术的大多数已发表工作进行了比较。表2中提供了用于对比的其他新兴和现有掺杂方案的简要概述。在[13,14], n型–i–n型 TFET的掺杂剖面中提出了一种–i–结构,其中采用深反向掺杂剖面以获得优异的开态‐关态特性以及相较于传统平面体硅MOSFET更低的–Vσ-VTH。文献[15],中提出了一种垂直高斯型掺杂剖面,并得出结论:对称双栅MOSFET相比非对称结构更具效率。在[17],中表明,非对称漏极掺杂剖面可改善TFET在亚阈值斜率方面的性能,并抑制双极性导电,从而使TFET更适合低功耗电路设计。梯度沟道双材料双栅(GCDMDG)[18]在较低漏极电流下实现了更高的漏极电流、峰值跨导以及更高的截止频率。文献[19]中指出较缓和的逆向沟道掺杂梯度表明,三栅MOSFET设计对于延续体硅CMOS晶体管缩放具有前景,并且能够实现类似的开态电流性能和固有延迟。在[20],中,研究了欠重叠源/漏区的高斯掺杂梯度,发现通过增加欠重叠源/漏区长度,亚阈值摆幅、漏致势垒降低和栅功函数均降低,而随着源/漏掺杂梯度的增加,这些参数则升高。在[21],中,通过采用SSR沟道掺杂分布有效抑制了短沟道效应,并在[22]中利用非对称欠重叠双栅MOSFET实现了良好的亚阈值工作特性。[23]中提出的模型通过源/漏掺杂种类捕捉横向电场扩展的影响,随着源/漏分布横向拖尾的增加,器件的阈值电压和有效沟道长度降低。本文所提出的掺杂剖面在亚阈值器件中提供了更高的Ion/Ioff比和适中的Ion电流。我们分析了

表2 器件列表的数据表( 本工作),包含不同的栅长(LG)、阈值电压(Vth)、Ion、Ioff、Ion/Ioff、MOSFET技术以及掺杂轮廓。 *

| LG(nm) | Vth(V) | Ion(mA/mm) | Ioff(mA/mm) | Ion/Ioff | FET技术 | 掺杂轮廓 | Ref. |

|---|---|---|---|---|---|---|---|

| 15 | 0.17 | 0.016(当VG=0.3 V,VD=0.4 V时) | 4×10⁻⁶ | 4×10³ | Bulk | 综合的 | *** |

| 100 | – | 600(当VG=1 V,VD=0.5 V时) | 0.3 | 2×10³ | 纳米线 | n‐i‐n结构 | [13] |

| 250 | 0.5 | 70 在 (VG=1 V, VD=1 V) 时 | 2×10⁻⁴ | 3.5×10⁴ | 平面/体材料 | 深反向 | [14] |

| 100 | 0.4 | 900 在(VG=1 V,VD=1 V)时 | – | – | 双栅(DG) | 垂直高斯 | [15] |

| 15 | 0.3 | 400 在 (VG=0.5 V, VD=1 V) 处 | 0.5 | 800 | 双栅(DG) | 梯度沟道 | [16] |

| 45 | 0.7 | 0.12(当(VG=0.5 V, VD=1 V)时) | – | – | DG 隧穿场效应晶体管 | 均匀,高斯 | [17] |

| 15 | 0.4 | 300(当(VG=0.5 V, VD=1 V)时) | 0.5 | 600 | 双栅(DG) | 低‐高‐低(突变) | [18] |

| 18 | 0.2 | 45 在(VG=0.3 V,VD=0.7 V)时 | 7×10⁻³ | 6.4×10³ | 鳍式场效应晶体管,三栅 | 逆向 | [19] |

| 9 | – | 在(VG=0.3V,VD=0.6 V)时 | 0.5 | – | 纳米双栅 | 高斯 | [20] |

| 28 | 0.34, 0.32 | 476,428(在 VG=0.5 V,VD=0.38 V 时) | 1.08×10⁻³ | 4.4×10⁵, 3.9×10⁵ | 平面/体材料 | 均匀,超陡逆向 | [21] |

| 30 | 0.23 | – 在(VG=0.3 V,VD=0.3 V)时 | – | – | 双栅欠叠 | 源/漏欠叠 | [22] |

| 70 | 0.3 | 400 在 (VG=0.5 V, VD=1 V) 处 | – | – | 双栅 | S/D横向高斯 | [23] |

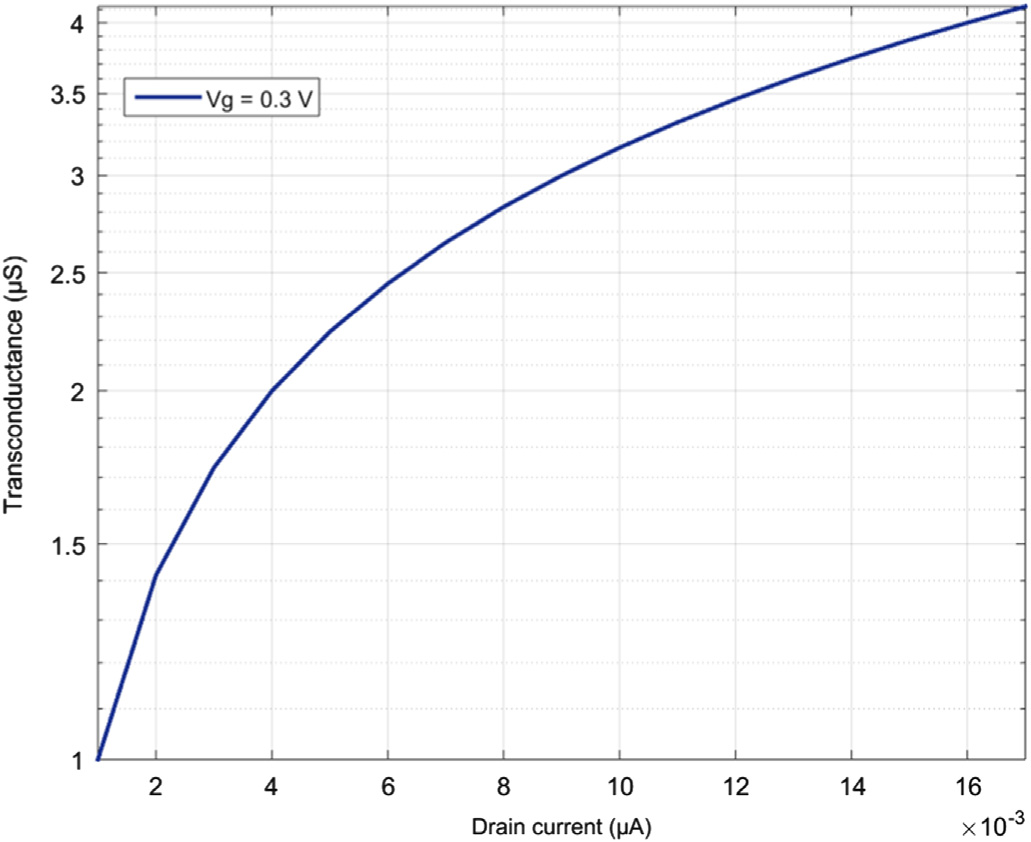

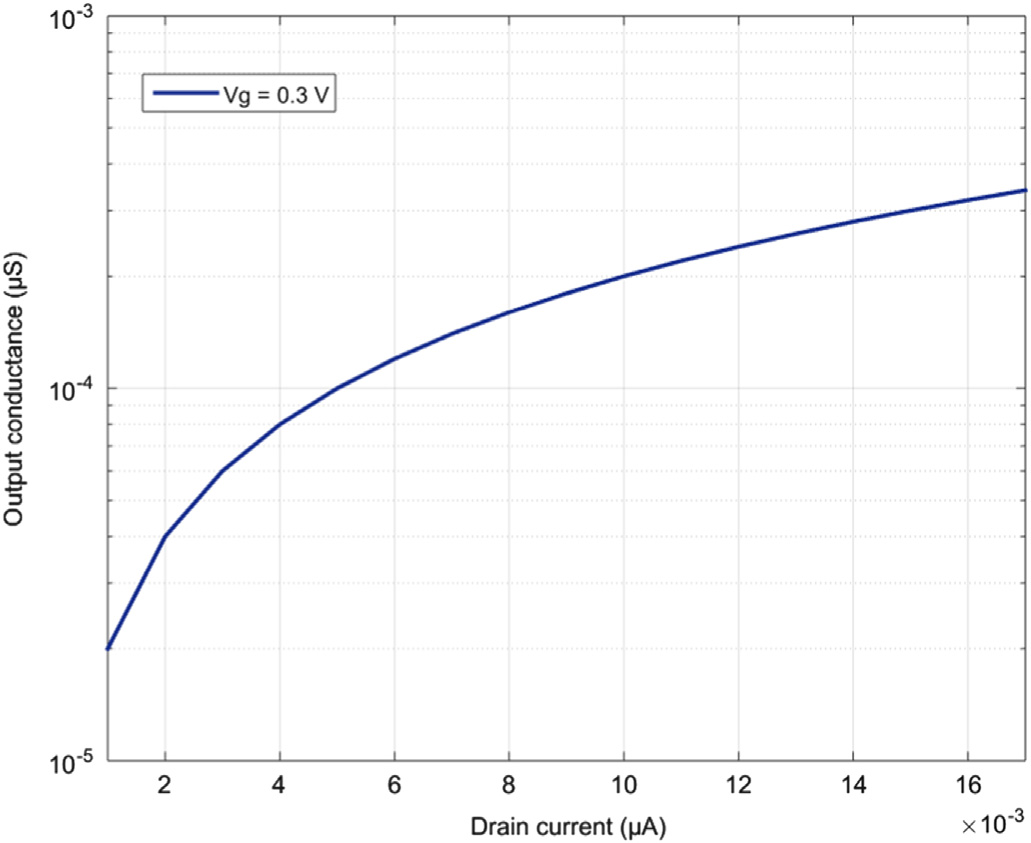

对于MOSFET,两个小信号输出尤其值得关注,因为它们提供了有关器件性能的信息。这两个参数分别是跨导(gm)和输出电导(g₀)。跨导是指漏极电流变化与栅极电压变化的比值。图5显示了跨导的变化情况。跨导越大,放大能力越强,且MOSFET能够在给定栅极电压下提供更大的电流。跨导随着漏极电流的增加而迅速增大,并在0.017mA处达到最大值。输出电导定义为漏极端口电流变化与漏极端口电压变化的比值(输出电导:g₀=∂ID/∂VD)。图6显示了输出电导的变化情况。输出电导越大,在给定漏极电压下漏极电流越大。通过频域扰动步骤,将一个交流信号叠加在漏极电压上。在本研究中,漏极电压在0至0.3 V范围内变化,栅极电压保持恒定在0.3 V。利用小信号分析,输出电流表达式可表示为(4),其中id为小信号电流,gm和g₀分别为跨导和输出电导。

$$

i_d = g_m v_{gs} + g_0 v_{ds}

\tag{4}

$$

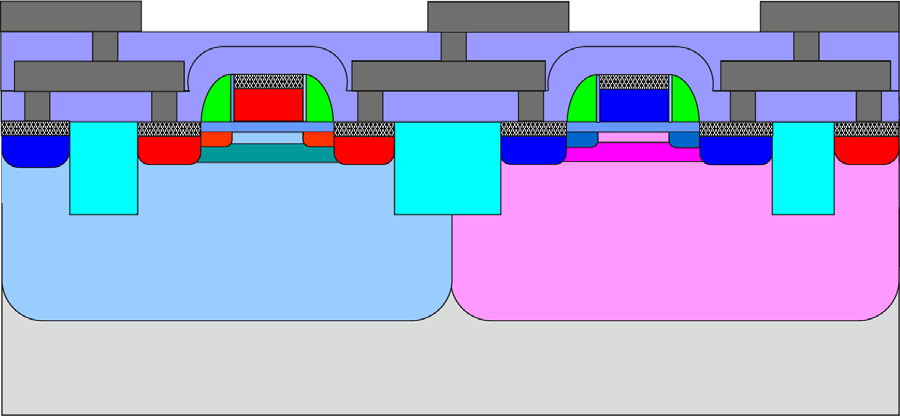

对于器件性能优化,精确调节掺杂分布是一项非常关键的任务。图7显示了N沟道MOS在P型阱内构建,P沟道MOS在N型阱内构建,并且两者均被放置在同一N型衬底上。此外,轻掺杂漏极(LDD)和超陡峭反向阱(SSRW)也被引入到基本的互补金属氧化物半导体结构中,如图7所示。器件内部如何引入低掺杂的源极和漏极,以及如何形成金属接触以构建所需的逻辑电路,也在图7中展示,以便读者理解。

图8显示了沿沟道长度方向的净掺杂浓度分布。图9显示了在栅极电压恒定、漏极电压Vd变化时的电子浓度分布。当漏极电压Vd增加时,沟道区域内的电子浓度会降低,最终导致夹断状态。从图9可以看出,在沟道内部,电子浓度的减少非常小,对于不同的漏极电压。这一现象也证实,采用我们所提出的掺杂方案的器件在饱和区具有显著更低的夹断效应。它还显示了源极和漏极端理想的电子分布图,其值应高于沟道区域。

图10显示了器件区域内的空穴分布图。空穴分布应远小于且与源/漏和沟道区域内的电子分布相反。图10确认了在整个器件中空穴分布的期望形状。电势也是完美器件操作的另一个重要因素。图11显示了漏极端的电势分布。随着漏极电压升高,漏极端的电势也应上升。图11显示,在Vd=0.4V时,漏极端的电势最高,而在Vd=0V时电势最低。

4. 结论

本文提出了一种用于亚阈值晶体管的综合掺杂剖面。所提出的掺杂剖面在亚阈值器件中提供了更高的Ion/Ioff比以及适中的Ion电流。我们采用该综合掺杂方案,在不同的体偏置和栅极偏压条件下,分析了亚阈值器件应用中的参数Ion、Ioff和Vth。同时还分析了不同偏置条件下的跨导、输出电导、电子/空穴分布以及电势。结果表明,与表2中列出的具有不同掺杂分布的现有MOS技术相比,使用所提出综合掺杂剖面的优化器件能够在最小VD和VG下提供更好的Ion电流。结果还显示,在考虑体偏置时,Ion/Ioff比更高。需要明确的是,目前工业界大多数仍在使用优化的超阈值设计,并依赖器件尺寸调整来实现低功耗操作。在超阈值器件中引入晕环注入是为了在沟道中产生反向短沟道效应,从而导致器件的尺寸设计基于比实际工艺节点更早期的节点(例如65纳米节点采用100纳米沟道长度)。在我们所提出的掺杂剖面中消除晕环注入可去除这一影响,使最优器件尺寸回归到当前节点的最小尺寸,从而实现硅面积的实际减小。然而,仍存在一些困难和不变性需要解决。漏极感应势垒降低(DIBL)是其中之一问题。漏致势垒降低在较高电压下会导致穿通,且可能导致对器件行为的控制能力下降。我们未来的工作将详细分析其他参数,如漏致势垒降低和亚阈值摆幅,以相对于现有掺杂技术对所提出的掺杂方案进行更综合的分析。

24

24

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?